我们可以把路由器比作网络世界的骨架,我们之所以能够在网络世界里畅游,很大程度上是得益于这个铁盒子。

自:http://blog.csdn.net/hanhannina/article/details/7166452

路由器硬件结构

1、 主要硬件组成

硬件:中央处理器(cpu)、内存、接口、控制端口、等物理硬件和电路

软件:路由器的IOS系统

2、 中央处理器(CPU)

Cisco路由器主要采用Motorola68030和Orion/R4600

主要负责路由器的配置管理和数据包的转发工作

3、 只读内存(ROM)

只读内存(ROM ,Readly Memory) 只能读取而不能写入。用来储存厂家固化写入的程序数据。

ROM中主要高扩

① 系统加电自检代码(POST),检测硬件部分是否完好

② 系统引导区代码(BootStrap),用于启动路由器并载入IOS操作系统

③ 备份的IOS操作系统。通常这个IOS版本比现运行的版本低一些。

4、 闪存(flash)

可读可写的存储器。在系统重新启动或关机之后仍能保存数据。Flash中存放着当前使用的IOS。Flash大则可以放入多个版本的IOS,对升级有利。避免长时间的网络故障。

5、 非易失性RAM(NVRAM)

NVRAM(Nonvolatile RAM)是可读可写的,在系统重新启动或者关机之后仍能保存数据。仅用于保存启动配置文件(Startup-Config),故其容量较小,通常只配置32KB~128KB。同时NVRAM速度快,且成本高。

6、 随机存储器(RAM)

RAM可读可写。但是存储的内容在系统重启或关机后将被清除。RAM是运行期间暂时存放操作系统和数据的存储器。让路由器能迅速访问这些讯息。RAM的存取速度优先于前面的存取速度。

运行期间,RAM中包含有:路由表项目、ARP缓冲项目、日志项目和队列中排队等待发送的分组、运行配置文件、正在执行的代码、IOS操作系统程序、临时数据信息。

RAM分为两大类:

Static RAM/SRAM。速度快、价钱高。用在CPU的一级、二级缓存。

Dynamic RAM/DRAM。比任何ROM都快。只能将数据保持很短的时间。为了保持数据DRAM必须搁一段时间刷新(refresh)一次。如果没刷新,数据就会丢失。

7、 路由器接口

每个接口都有自己的名字。

对于接口固定的路由器:名字由类型标志与数字编号构成。例:Ethernet0

对于支持“在线插拔和删除”或具有动态更改物理接口配置的路由器:全名称中至少有连个数字,中间用斜杠“/”分割。例:serial3/0、Ethernet4/0/1

8、 控制台端口

用于用户或者管理员能够利用终端与路由器进行通信,完成路由器配置。该端口提供了一个EIA/TIA-232异步串行接口,用于在本地对路由器进行配置(首次配置必须通过控制台端口进行)。采用DB25连接器。

9、 路由器加电启动过程

① 系统硬件加电自检。运行ROM中的硬件检测程序,检测各组件能否正常工作。完成硬件检测后,开始软件出事话工作。

② 软件初始化过程。运行ROM中的BootStrap程序,进行初步引导工作。

③ 寻找并载入IOS系统文件。

④ IOS装在完毕,系统在NVRAM中搜索保存的Starup-Config文件,进行系统的配置。如果NVRAM中存在Starup-Config文件,则将该文件调入RAM中并逐条执行。否则,系统进入Setup模式,进行路由器初始配置

路由器硬件架构

随着专用多核网络处理器、专用转发芯片的出现,使得现代路由器摆脱了以往纯软件转发的局限,向着高吞吐率、硬件快速转发等方向发展。高端的路由器设计成多板分布式+冗余备份的架构,使转发能力成倍的增强,同时还大大提高了业务的稳定性。

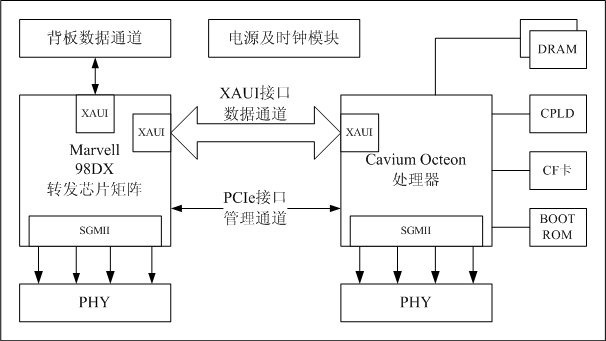

下图是一幅典型的路由器硬件架构图:

目前高端路由器大多采用专门的多核网络处理器作为CPU,如Cavium公司研发的Octeon系列处理器,主流的6000系列16~32个核,即将上市的7000系列多达64个核,并行处理能力大大加强。并且这类专用网络处理器在硬件上都对网络报文的解析、保序、转发等方面提供了专门的协处理器进行支持,优化并提高了系统的转发能力,也为软件研发者省去了不少麻烦。

Broadcom、Marvell等公司提供专门的转发芯片,通过VLAN、硬件路由等功能,在硬件上直接支持了对报文的二三层的线速转发,并且多片交换芯片之间可连接,最终形成一个大的交换矩阵网络。

CPU和交换芯片之间的数据通道可由10G高速接口相连,实现海量数据的传输;管理通道通过PCIe总线相连,传输控制信号。

64位的CPU有着广阔的寻址空间,可以支持很大的DRAM内存。

CF卡或SD卡用来存储系统程序,可以很方便的对系统程序进行升级。

BOOT ROM存储着系统加载程序,系统上电时首先从BOOT ROM开始运行,由BOOT ROM来负责加载整个操作系统。

CPLD中存储着系统的版本信息,由BOOT ROM来负责读取版本参数,并通知给系统。

作为分布式系统的话,各个单板之间通过背板接口传输数据和管理信息。

路由器软件架构

路由器是一个典型的嵌入式系统,我们只讨论与网络相关的部分:

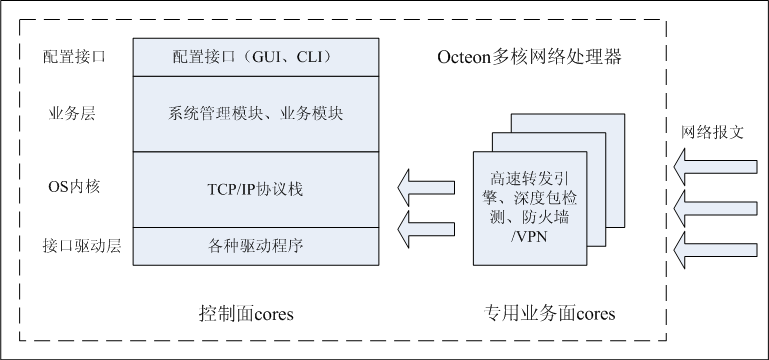

由于使用多核处理器,软件的设计架构可以非常灵活,我们一般在CPU层面就把业务划分开,拿出几个核跑特定的核心业务(无操作系统),这样可以大大加快核心业务的处理能力。其它的核一般跑Linux、VxWorks等嵌入式操作系统,作为控制面。相比较而言,控制面的报文转发能力就很差了,但由于有操作系统和协议栈的支持,控制面可以跑更复杂、更定制化的业务,根据客户需求灵活的设计业务模式。

1030

1030

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?