1.1PLL功能配置

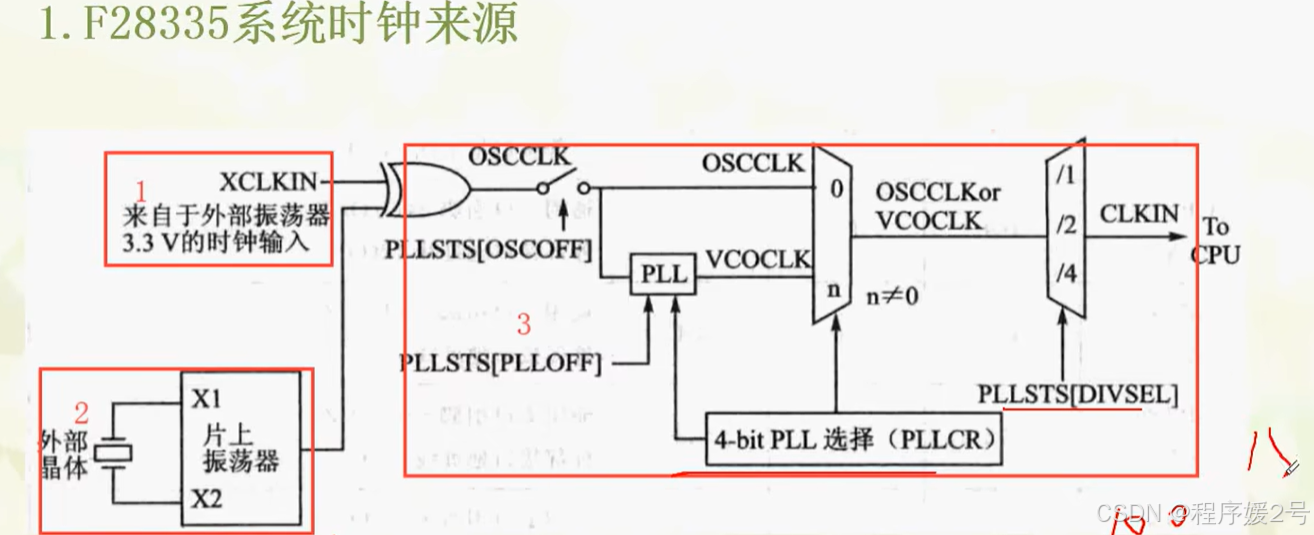

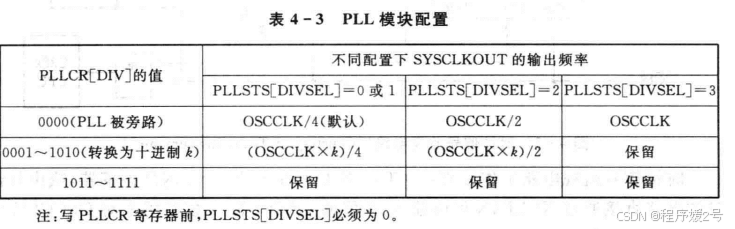

一般选择第二种时钟源,外部晶体产生30MHZ晶振,走PLL这条路,通过PLLCR进行10倍频,再通过DIVSEL进行2分频,即可得到150MHZ晶振;

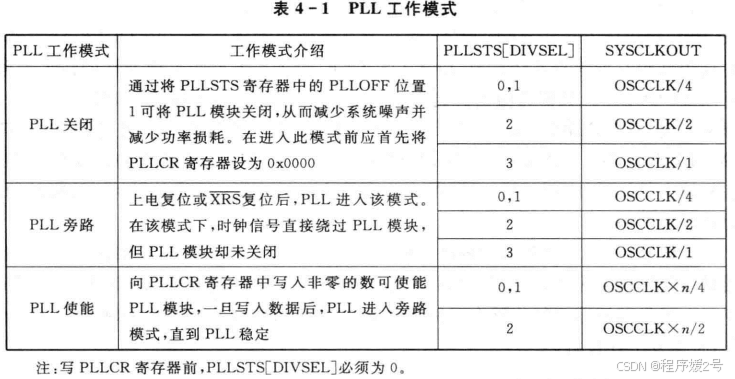

OSCCLK信号由内部振荡器或外部电路直接提供,而OSCCLK之后的时钟信号处理由PLL模块进行控制。PLL模块具有三种工作模式,由寄存器PLLSTS[DIVSEL]位决定;如表所示

1.2时钟信号监视电路

系统复位后,应首先通过软件检测PLLSTS[MCLKSTS]位,如果该位为1,则表明系统时钟信号丢失,应对硬件电路进行检查。通过向PLLSTS[MCLKCLR]位写1可将其清零并复位整个信号监视电路,如果再次检测到信号OSCCLK信号丢失,将重复上述过程

1.3相关寄存器

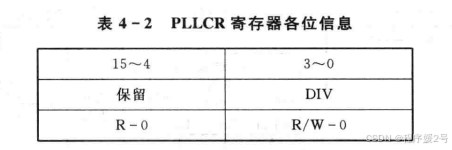

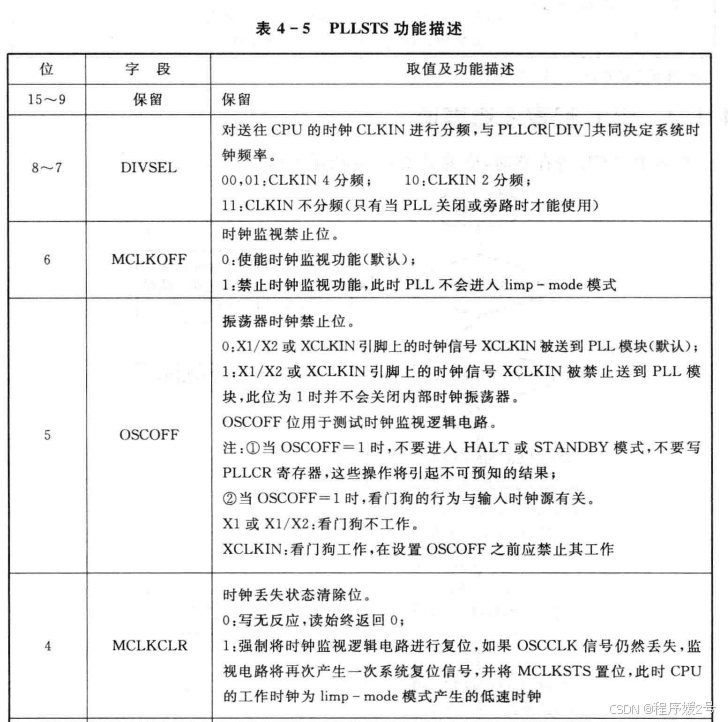

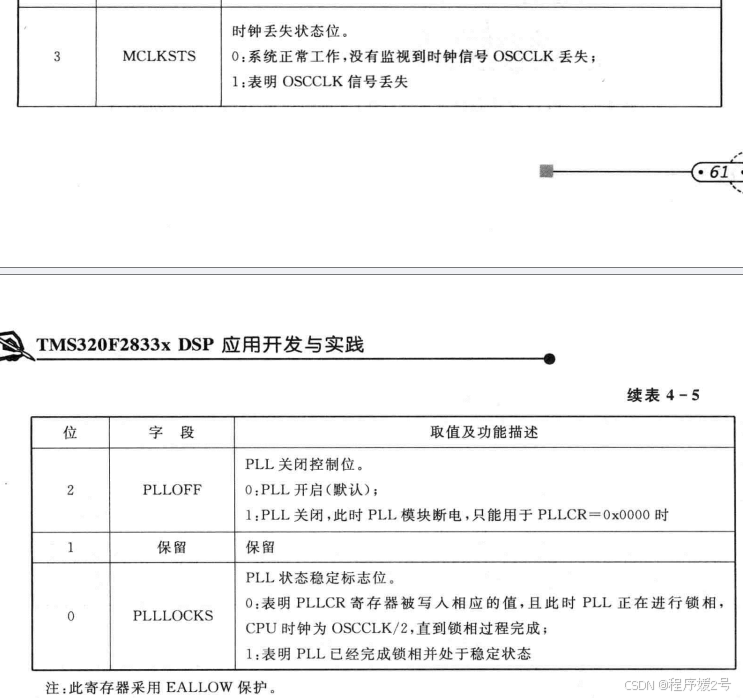

PLL模块相关的寄存器主要有PLLCR和PLLSTS两个;

PLLCR寄存器的DIV位段用来控制OSCCLK的倍频系数,并与PLLSTS[DIVSEL]位一起决定系统时钟SYSCLKOUT的频率

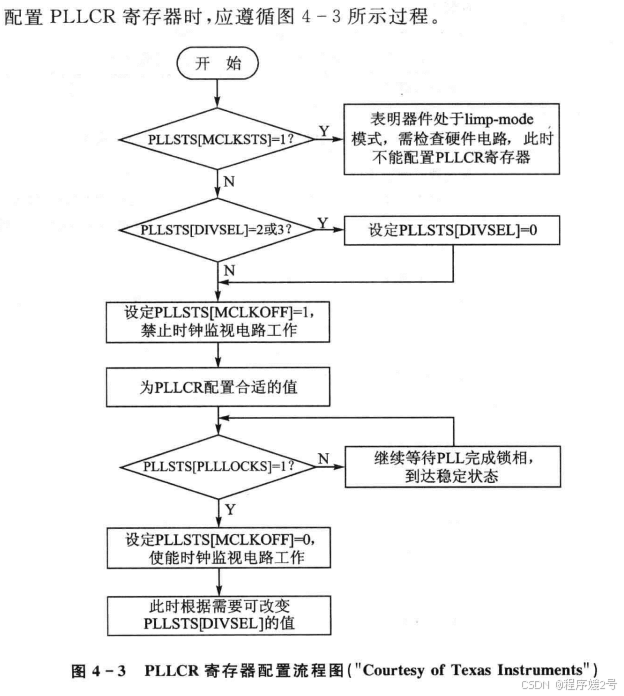

1.4PLL配置寄存器流程图

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?