名称:32位的ALU(算术逻辑单元)设计Verilog代码modelsim仿真(文末获取)

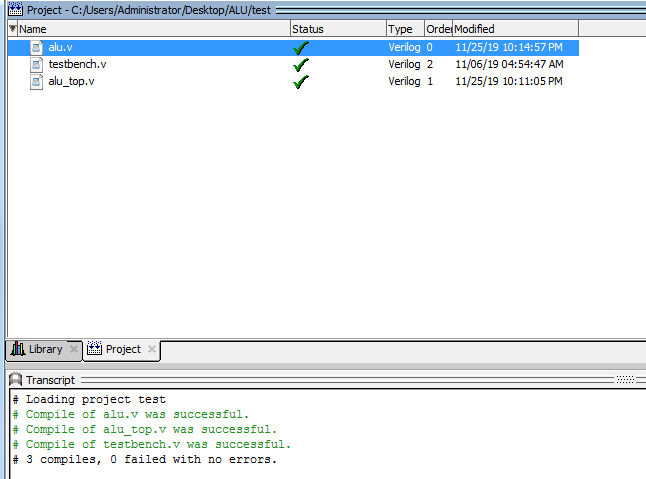

软件:modelsim

语言:Verilog

代码功能:

32位的ALU(算术逻辑单元)设计

这个实验室的目标是实现一个32位的ALU(算术逻辑单元)。ALU是CPU的基本计算组件。它的操作包括和、或、加、减法等。这个家庭作业将帮助您理解CPU架构。测试台的功能是自动读取输入数据,输出错误数据

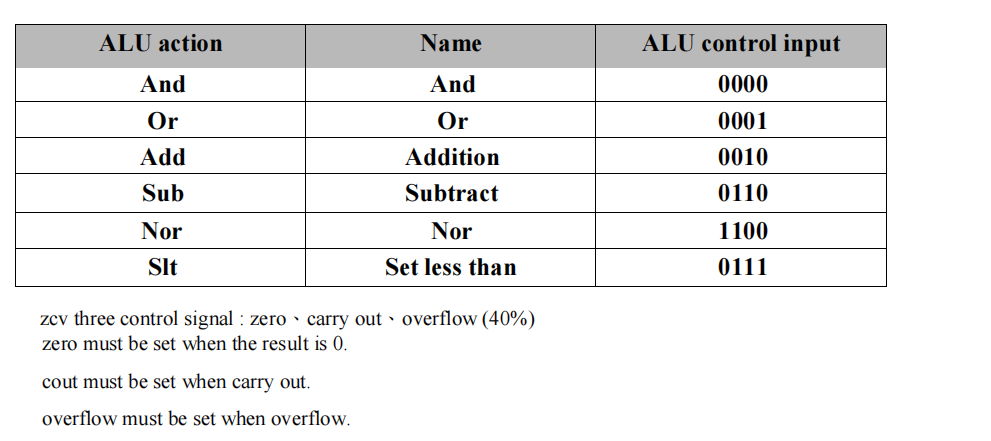

支持以下运算

1. 程序文件

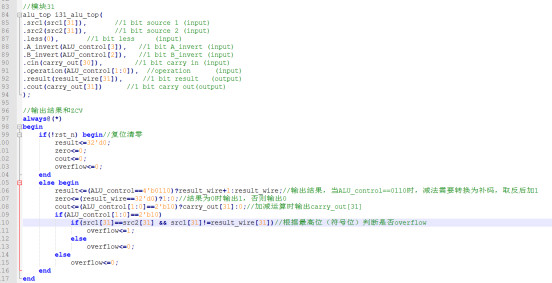

ALU_top

ALU

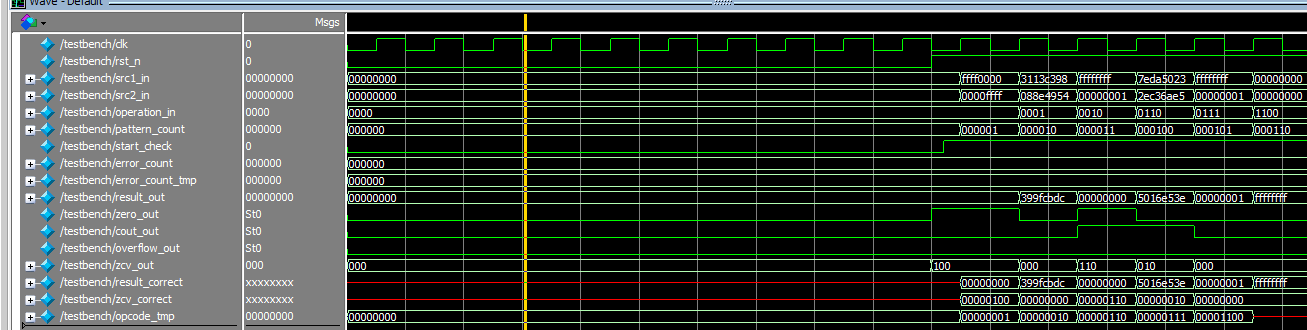

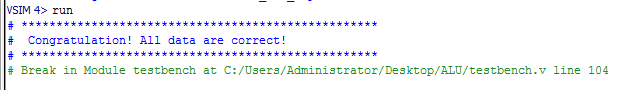

2. 仿真图

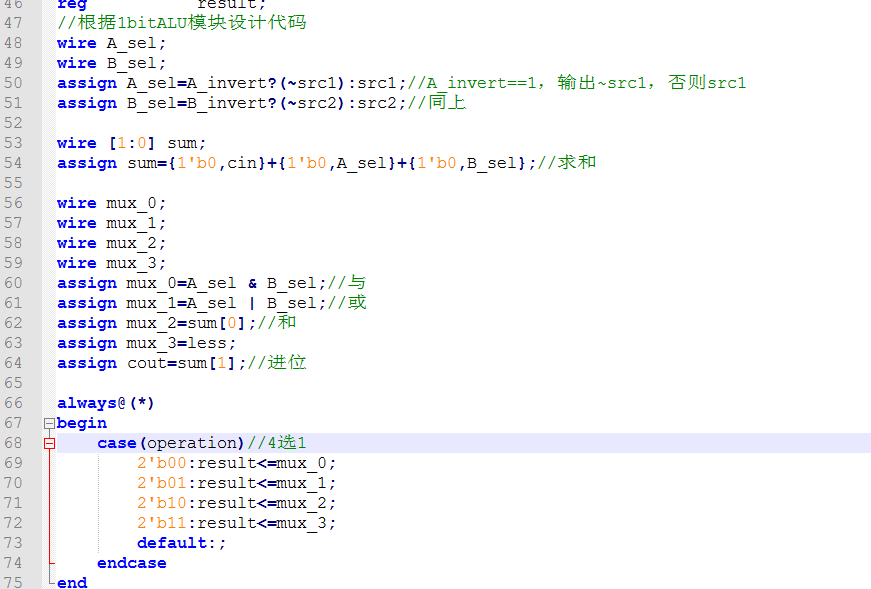

部分代码展示:

`timescale 1ns/1ps // // Company: // Engineer: // // Create Date: // Design Name: // Module Name: alu // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module alu( rst_n, // negative reset (input) src1, // 32 bits source 1 (input) src2, // 32 bits source 2 (input) ALU_control, // 4 bits ALU control input (input) result, // 32 bits result (output) zero, // 1 bit when the output is 0, zero must be set (output) cout, // 1 bit carry out (output) overflow // 1 bit overflow (output) ); input rst_n; input [32-1:0] src1; input [32-1:0] src2; input [4-1:0] ALU_control; output [32-1:0] result; output zero; output cout; output overflow; reg [32-1:0] result; reg zero; reg cout; reg overflow; //根据32bitALU设计代码 //调用32个1bitALU模块 wire [32-1:0] carry_out; wire [32-1:0] result_wire; //模块0 alu_top i0_alu_top( .src1(src1[0]), //1 bit source 1 (input) .src2(src2[0]), //1 bit source 2 (input) .less(1), //1 bit less (input) .A_invert(ALU_control[3]), //1 bit A_invert (input) .B_invert(ALU_control[2]), //1 bit B_invert (input) .cin(1'b0), //1 bit carry in (input) .operation(ALU_control[1:0]), //operation (input) .result(result_wire[0]), //1 bit result (output) .cout(carry_out[0]) //1 bit carry out(output) ); //使用FOR循环调用1~30模块 generate genvar i; for (i=1;i<31;i=i+1)begin:alu_num alu_top i1_alu_top( .src1(src1[i]), //1 bit source 1 (input) .src2(src2[i]), //1 bit source 2 (input) .less(0), //1 bit less (input) .A_invert(ALU_control[3]), //1 bit A_invert (input) .B_invert(ALU_control[2]), //1 bit B_invert (input) .cin(carry_out[i-1]), //1 bit carry in (input) .operation(ALU_control[1:0]), //operation (input) .result(result_wire[i]), //1 bit result (output) .cout(carry_out[i]) //1 bit carry out(output) ); end endgenerate //模块31 alu_top i31_alu_top( .src1(src1[31]), //1 bit source 1 (input) .src2(src2[31]), //1 bit source 2 (input) .less(0), //1 bit less (input) .A_invert(ALU_control[3]), //1 bit A_invert (input) .B_invert(ALU_control[2]), //1 bit B_invert (input) .cin(carry_out[30]), //1 bit carry in (input) .operation(ALU_control[1:0]), //operation (input) .result(result_wire[31]), //1 bit result (output) .cout(carry_out[31]) //1 bit carry out(output) ); //输出结果和ZCV always@(*) begin

源代码

点击下方的公众号卡片获取

2073

2073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?