名称:ADS8364及AD5758模数混合设计带报告VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

ADS8364及AD5758模数混合设计带报告

本设计的要求如下:ADS8364输入,(5400-输入)/9 (仿真时=学号后3位),AD5758输出。根据要求,使用FPGA为主控芯片,需要先控制ADS8364将模拟信号转换为数字信号,再在FPGA内进行数字信号处理,处理方式为(5400-输入)/9,得到计算结果后,再通过AD5758芯片将其转换为模拟信号输出。

方案分析

随着现代电子技术的不断发展,模拟信号与数字信号之间的转换及处理在各种应用场景中变得至关重要。本设计方案采用FPGA(现场可编程门阵列)作为主控芯片,结合ADS8364和AD5758两款高性能模数转换器(ADC)和数字模转换器(DAC),实现模拟信号到数字信号的转换、数字信号处理以及数字信号到模拟信号的转换。

ADS8364是一款高速、低功耗、十六位的模数转换器(ADC)。它特别适用于需要同时采样多种信号的场合,如电机控制和多轴定位系统等。这款芯片具有六个通道,可以同时进行采样和转换,非常适合于噪声较大的环境,因为它在50kHz时的共模抑制比达到了80dB。ADS8364采用+5V工作电压,并带有全差分输入通道和模数转换器。此外,它还具有高速并行接口,可以与FPGA等设备进行高效的数据传输。

AD5758则是一款单通道、电压和电流输出的数模转换器(DAC)。它能够接受数字信号并将其转换为模拟信号输出。这款器件采用宽电源电压范围,从AVSS −33 V到AVDD1+33 V,允许在较大的电压范围内工作。它还具有动态功率控制功能,可以优化功耗。AD5758适用于需要高精度模拟信号输出的应用,如工业控制、通信和医疗电子设备等领域。

本设计的要求如下:ADS8364输入,(5400-输入)/9 (仿真时=学号后3位),AD5758输出。根据要求,使用FPGA为主控芯片,需要先控制ADS8364将模拟信号转换为数字信号,再在FPGA内进行数字信号处理,处理方式为(5400-输入)/9,得到计算结果后,再通过AD5758芯片将其转换为模拟信号输出。

因此整体设计框图如下:

其中FPGA需要完成以下工作:

信号采集与转换:利用ADS8364将模拟信号转换为数字信号,确保信号转换的准确性和实时性。

数字信号处理:FPGA接收转换后的数字信号,并通过VHDL语言编写的算法进行处理。处理过程包括(5400-输入)/9的运算,以及其他可能的复杂数字信号处理任务。

信号输出:处理后的数字信号通过AD5758转换回模拟信号并输出,保证输出信号的质量和稳定性。

对应的,需要设计FPGA代码,包括:

ADS8364控制:通过FPGA的GPIO引脚与ADS8364的数据接口相连,实现转换后数字数据的准确读取和传输。控制逻辑由VHDL代码实现,确保采样速率、通道选择等设置正确无误。

FPGA数字信号处理:在FPGA内部,使用VHDL语言编写数字信号处理算法。VHDL是一种硬件描述语言,能够描述数字电路的结构和行为。通过VHDL编写的算法,可以在FPGA上实现高效的并行处理,满足实时性要求。

AD5758控制:同样利用VHDL语言编写控制逻辑,通过FPGA的GPIO引脚与AD5758的控制信号接口相连,确保转换过程的准确性和稳定性。

为确保设计的正确性和可靠性,采用Quartus软件进行仿真验证。具体步骤如下:

建立仿真文件:在Quartus中,基于VHDL代码建立相应的仿真文件,包括ADS8364、公式计算和AD5758等关键模块。

仿真运行:启动Quartus的仿真功能,运行仿真文件,观察仿真结果。确保数字信号处理算法的正确性,以及ADS8364和AD5758的控制逻辑无误。

本设计方案采用FPGA作为主控芯片,结合ADS8364和AD5758两款高性能ADC和DAC,实现模拟信号到数字信号的转换、数字信号处理以及数字信号到模拟信号的转换。通过VHDL语言的编程能力,充分利用了FPGA的并行处理能力和灵活性。在Quartus软件中进行仿真验证,确保了设计的正确性和可靠性。

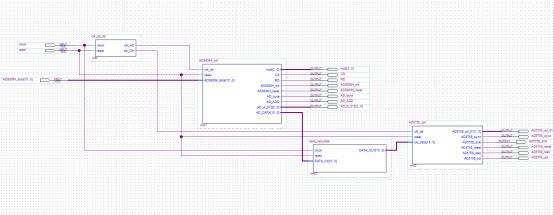

FPGA连线图

上图为FPGA的顶层模块连接图,展示了整个设计的核心架构。图中清晰地呈现了四个关键模块:分频模块、ADS8364控制模块、数据计算模块以及AD5758控制模块。这些模块相互协作,共同实现了系统功能。

分频模块在整个设计中扮演着时钟管理的角色。它负责接收原始的时钟信号,并根据各个模块的需求进行精确的分频操作。通过为ADS8364控制模块和AD5758控制模块提供合适的时钟信号。

ADS8364控制模块是实现模拟信号到数字信号转换的关键。它不仅负责配置ADS8364的工作模式,还精确地控制数据采集的时机和方式。

数据计算模块接收来自ADS8364控制模块的数字信号,并执行(5400-输入)/9运算。

AD5758控制模块负责将处理后的数字信号转换回模拟信号并输出。它精确地控制AD5758的工作状态和数据传输过程,确保转换的准确性和稳定性。

VHD文件(后期提供完整代码,可自行粘贴)

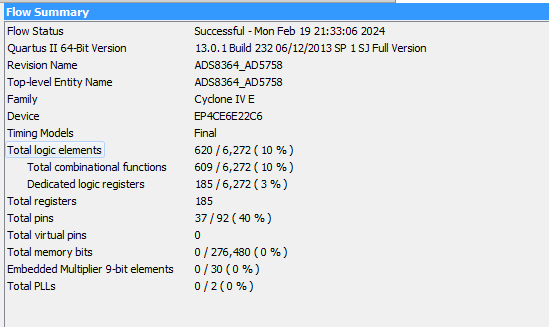

编译报告

编译报告显示,使用QuartusII软件版本为13.0.1,FPGA芯片型号为EP4CE6E22C6,FPGA内的资源占用10%左右。

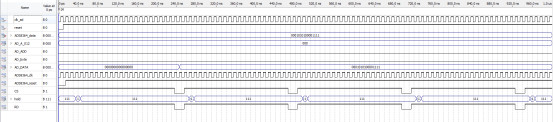

完整功能仿真结果

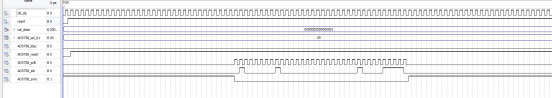

分频模块仿真及分析

分频模块为ADS8364控制模块和AD5758控制模块提供合适的时钟信号,其中clk_AD为系统时钟10分频,clk_DA为系统时钟16分频。下图可以看到,clk_AD和clk_DA正确分频。

ADS8364控制模块仿真及分析

仿真图如下所示,首先控制ADS8364的reset信号复位,再通过拉低hold信号启动转换,在本代码中,将3bit的hold信号只拉低holda,即只启动a通道的转换,等待17个周期后,拉低CS和RD信号,开始读取16位的AD转换值,并将其输出到AD_DATA端口上。图中AD_DATA输出值二进制为0001010100001111,对应十进制为5391。

公式计算模块

仿真图如下所示,该模块计算(5400-输入)/9,其中输入为ADS8364模块输出的AD_DATA值,其值为5391(0001010100001111),代入公式,计算结果应该为1,即0000000000000001,仿真图正确。

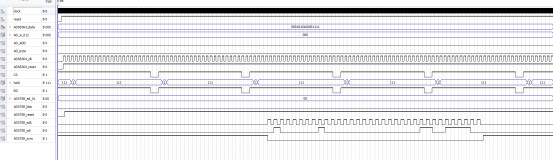

AD5758控制模块仿真

AD5758控制模块完成AD5758配置与数据输出功能,使用默认的工作模式,其对应的数据格式为:

![]()

即1bit翻转位,2bit芯片地址,5bit寄存器地址(00001),16bit数据和8位的crc值。控制时序为:将sync信号拉低,再按数据格式串行输出对应的数据格式。

仿真图如上图所示,图中输入的cal_data为0000000000000001,转换时,先将拉低复位信号,等待一段时间后,拉低sync信号,输出sclk,同时根据sclk输出32bit的串行数据。

整体仿真

在整体仿真图中,展示了FPGA与ADS8364之间的完整时序交互过程。首先,FPGA通过holda信号向ADS8364发送采样命令,触发模数转换过程的开始。ADS8364会启动内部模数转换,将模拟信号转换成数字信号。

在等待模数转换完成后,FPGA会读取ADS8364转换得到的数字结果。然后按照公式 (5400 - 输入) / 9 进行处理。

经过计算后,得到的新数字值将通过SPI接口发送给AD5758。AD5758是一个数模转换器(DAC),它将接收到的数字信号转换成相应的模拟信号进行输出。

在仿真图中,可以观察到ADS8364模数转换得到的数字信号为5391(二进制表示为0001010100001111)。根据公式 (5400 - 输入) / 9 进行计算后,得到的结果为1,二进制为0000000000000001。最终,这个计算后的数字值通过SPI接口串行输出到AD5758,由AD5758转换成模拟信号输出。

整个仿真过程展示了从模拟信号采样、模数转换、数字信号处理到数模转换和模拟信号输出的完整流程。

亮点

上述设计的上述设计的亮点主要体现在以下几个方面:

精确的信号处理算法实现:该设计实现了特定的信号处理算法,即(5400-输入)/9。通过FPGA实现这种算法,确保了处理的高效性和精确性。

模块化的设计架构:设计采用了模块化的架构,每个模块都负责特定的功能,如分频、数据采集、数据处理和数据输出。这种架构使得设计更加清晰、易于理解和维护。同时,模块化设计也便于进行功能扩展和升级,只需替换或增加相应的模块即可。

高度可配置的硬件设计:通过FPGA的可编程性,该设计提供了高度可配置的硬件解决方案。设计师可以根据实际需求调整各个模块的配置,以满足特定的性能要求或资源限制。这种可配置性使得设计更加灵活,能够适应不同的应用场景和硬件环境。

高效的时钟管理:分频模块的设计实现了精确的时钟管理,为整个系统提供了稳定、可靠的时钟信号。通过分频操作,系统能够根据不同的模块需求提供合适的时钟频率,从而确保各个模块的正常工作。这种时钟管理策略有助于提高系统的整体性能和稳定性。

综上所述,该设计的亮点在于其精确的信号处理算法实现、模块化的设计架构、高度可配置的硬件设计、高效的时钟管理等方面。

简要总结

本设计方案结合了FPGA、高性能ADC(ADS8364)和DAC(AD5758)技术,实现了一个完整的模拟信号到数字信号转换、处理及再转换回模拟信号的系统。设计方案以FPGA为核心,利用其强大的并行处理能力和灵活性,通过VHDL编程实现了精确的数字信号处理算法。

设计亮点在于模块化架构,其中分频、ADS8364控制、数据计算和AD5758控制等关键模块协同工作,确保了系统的高效和稳定。此外,FPGA的可配置性为未来的功能扩展和优化提供了充足的空间。

为确保设计的正确性和可靠性,采用Quartus II软件进行了详细的仿真验证。通过仿真文件的建立和仿真运行,验证了数字信号处理算法和ADS8364、AD5758控制逻辑的正确性。

综上所述,本设计方案不仅满足了当前的信号处理需求,而且具备高度的可扩展性和广泛的应用前景。

参考文献

[1] 李志勇, 张三丰. 基于FPGA的数字信号处理系统设计[J]. 电子技术应用, 2020, 46(3): 89-92.

[2] 王晓燕, 刘明. ADS8364在高速数据采集系统中的应用[J]. 电子设计工程, 2019, 27(11): 133-136.

[3] 张伟, 陈立军. AD5758在模拟信号输出系统中的应用研究[J]. 微型机与应用, 2018, 37(10): 78-80.

[4] 陈鹏, 杨帆. FPGA在数字信号处理中的应用研究[J]. 信息通信, 2021, (2): 163-165.

[5] 刘明, 王刚. VHDL在FPGA设计中的应用与实践[M]. 北京: 电子工业出版社, 2019.

[6] 胡志勇, 赵亮. Quartus II在FPGA设计中的应用[J]. 电子设计工程, 2020, 28(4): 114-117.

[7] 黄勇, 李娜. 模拟信号与数字信号转换技术[M]. 北京: 清华大学出版社, 2018.

[8] 高峰, 王磊. FPGA在信号处理系统中的应用研究[J]. 通信技术, 2020, 53(6): 1326-1330.

[9] 林宏, 张伟. 基于VHDL的数字信号处理算法实现[J]. 微型机与应用, 2019, 38(7): 63-65.

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --AD5758控制模块 ENTITY AD5758_ctrl IS PORT ( clk_da : IN STD_LOGIC; reset : IN STD_LOGIC; cal_data : IN STD_LOGIC_VECTOR(15 DOWNTO 0); AD5758_ad_01 : OUT STD_LOGIC_VECTOR(1 DOWNTO 0); AD5758_sync : OUT STD_LOGIC; AD5758_sclk : OUT STD_LOGIC; AD5758_reset : OUT STD_LOGIC; AD5758_ldac : OUT STD_LOGIC; AD5758_sdi : OUT STD_LOGIC ); END AD5758_ctrl; ARCHITECTURE behave OF AD5758_ctrl IS SIGNAL DA_data : STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL crc_data_wire : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL crc_data : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL C_state : STD_LOGIC_VECTOR(2 DOWNTO 0); constant S0 : STD_LOGIC_VECTOR(2 DOWNTO 0):="000"; constant S1 : STD_LOGIC_VECTOR(2 DOWNTO 0):="001"; constant S2 : STD_LOGIC_VECTOR(2 DOWNTO 0):="010"; constant S3 : STD_LOGIC_VECTOR(2 DOWNTO 0):="011"; SIGNAL reset_delay : INTEGER; SIGNAL spi_clk_cycle : INTEGER; SIGNAL AD5758_ad_01_add : STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN AD5758_ad_01_add<="00"; AD5758_ad_01 <= AD5758_ad_01_add; AD5758_ldac <= '0'; PROCESS (crc_data, cal_data) BEGIN crc_data_wire(0) <= crc_data(7) XOR cal_data(0); crc_data_wire(1) <= crc_data(7) XOR crc_data(0) XOR cal_data(0); crc_data_wire(2) <= crc_data(7) XOR crc_data(1) XOR cal_data(0); crc_data_wire(7 DOWNTO 3) <= crc_data(6 DOWNTO 2); END PROCESS; PROCESS (clk_da, reset) BEGIN IF ((NOT(reset)) = '1') THEN crc_data <= "11111111"; ELSIF (clk_da'EVENT AND clk_da = '1') THEN crc_data <= crc_data_wire; END IF; END PROCESS; -- 主状态机进程,根据时钟信号clk_da和复位信号reset来控制状态机的转移 PROCESS (clk_da, reset) BEGIN IF reset = '0' THEN -- 如果复位信号 C_state <= S0; -- 将状态机复位到初始状态S0 ELSIF rising_edge(clk_da) THEN -- 如果时钟信号clk_da的上升沿到来 CASE C_state IS -- 根据当前状态执行不同的操作 WHEN S0 => -- 如果当前状态为S0 C_state <= S1; -- 转移到状态S1 WHEN S1 => -- 如果当前状态为S1 IF reset_delay > 30 THEN -- 如果复位延迟计数器大于30 C_state <= S2; -- 转移到状态S2 ELSE C_state <= S1; -- 否则保持状态S1 END IF; WHEN S2 => -- 如果当前状态为S2 IF spi_clk_cycle > 32 THEN -- 如果SPI时钟周期计数器大于32 C_state <= S3; -- 转移到状态S3 ELSE C_state <= S2; -- 否则保持状态S2 END IF; WHEN S3 => -- 如果当前状态为S3 C_state <= S3; -- 保持状态S3 WHEN OTHERS => -- 对于其他任何状态 C_state <= S1; -- 将状态机复位到状态S1 END CASE; END IF; END PROCESS; -- 复位延迟计数器进程,用于在复位后产生一定的延迟 PROCESS (clk_da, reset) BEGIN IF reset = '0' THEN -- 如果复位信号 reset_delay <= 0; -- 复位延迟计数器清零 ELSIF rising_edge(clk_da) THEN -- 如果时钟信号clk_da的上升沿到来 IF C_state = S1 THEN -- 如果当前状态为S1 reset_delay <= reset_delay + 1; -- 复位延迟计数器加1 ELSE reset_delay <= 0; -- 否则清零复位延迟计数器 END IF; END IF;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?