名称:老虎机游戏设计VHDL代码Quartus仿真(文末获取0

软件:Quartus

语言:VHDL

代码功能:

老虎机游戏

设计一个游戏机,用3位数码管来代替老虎机的3个轮盘,用0-7的数字来代替老虎机轮盘上的不同图案。按下key1,3个数码管的数字开始循环显示,再次按下key1,3个数码管的数字停止循环,当显示的3个数字相同时,游戏胜利。

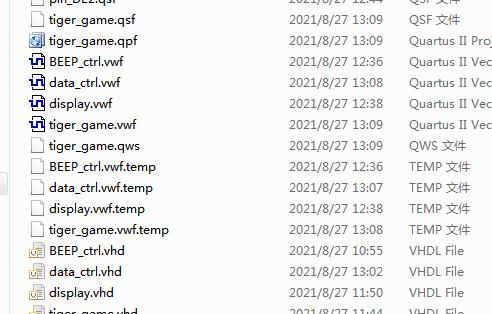

1.工程文件

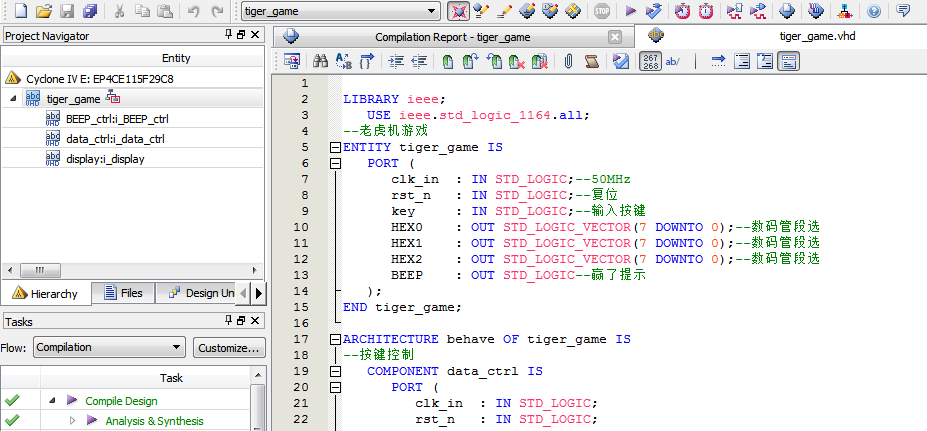

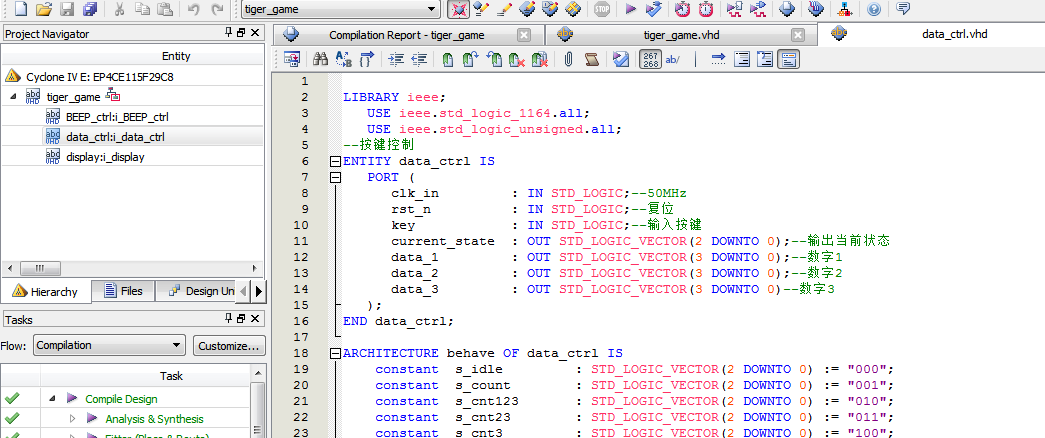

2.程序文件

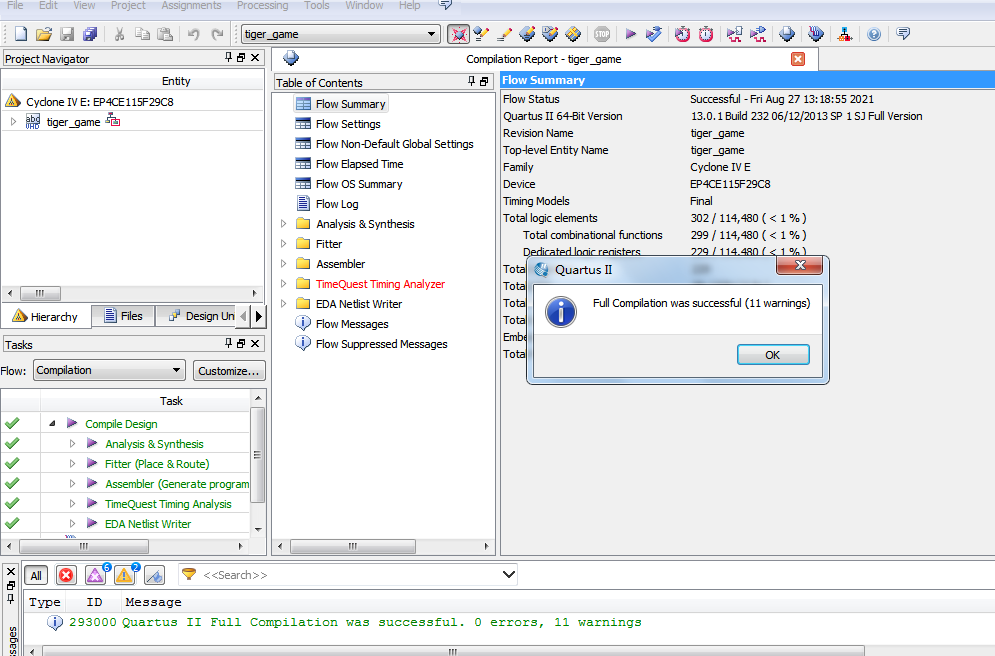

3.程序编译

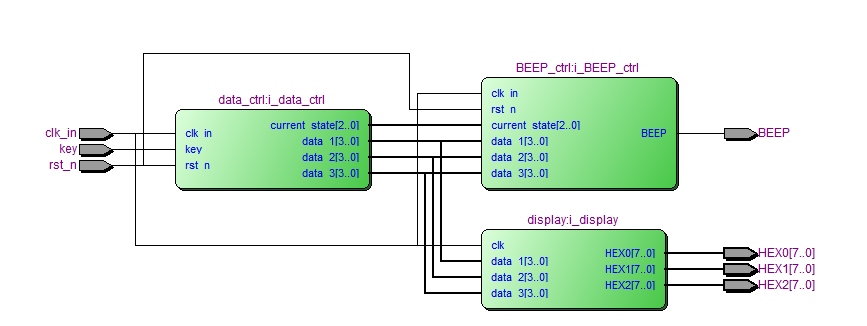

4.RTL图

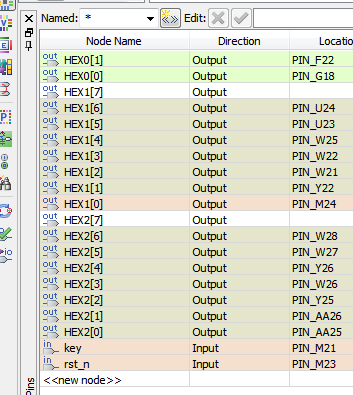

5.管脚分配

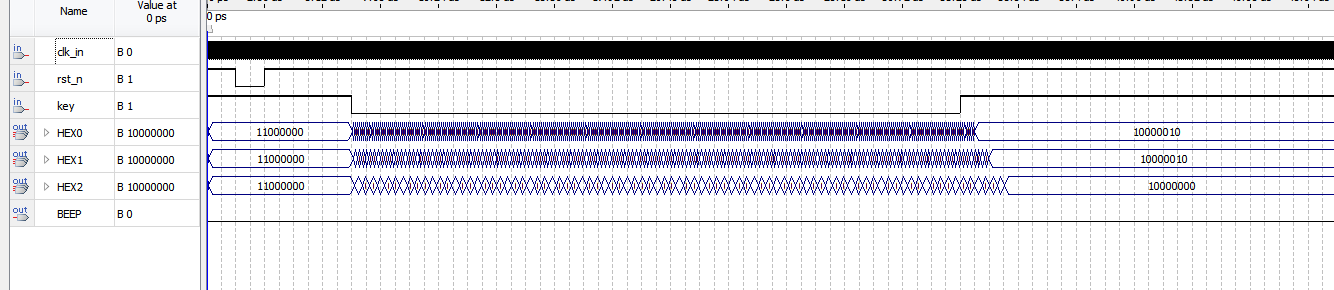

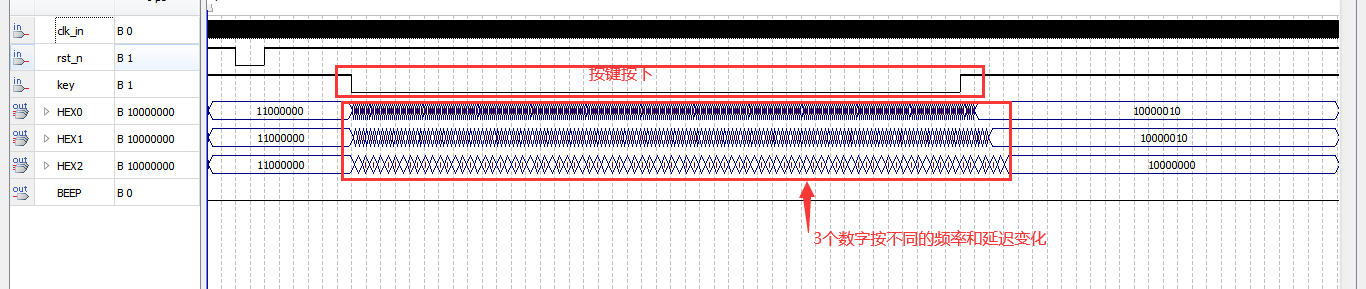

6.仿真图

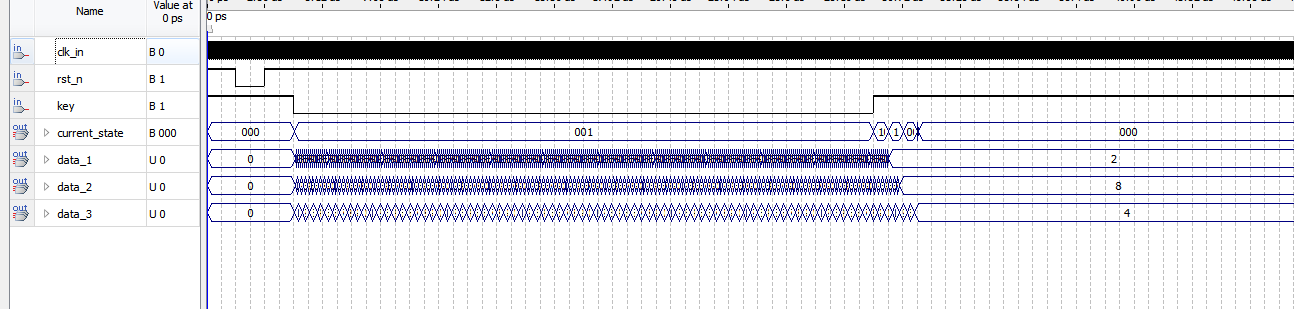

整体仿真图

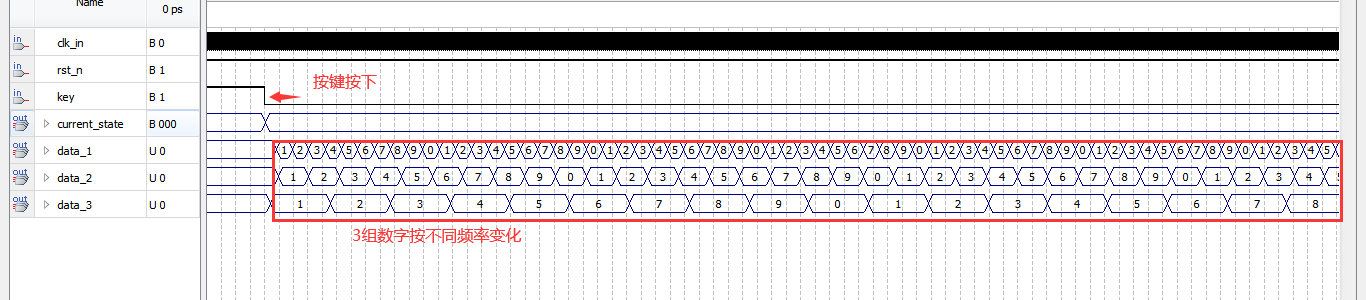

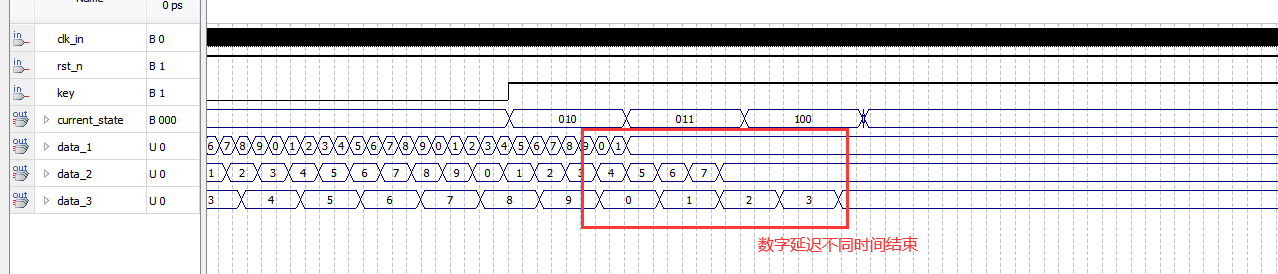

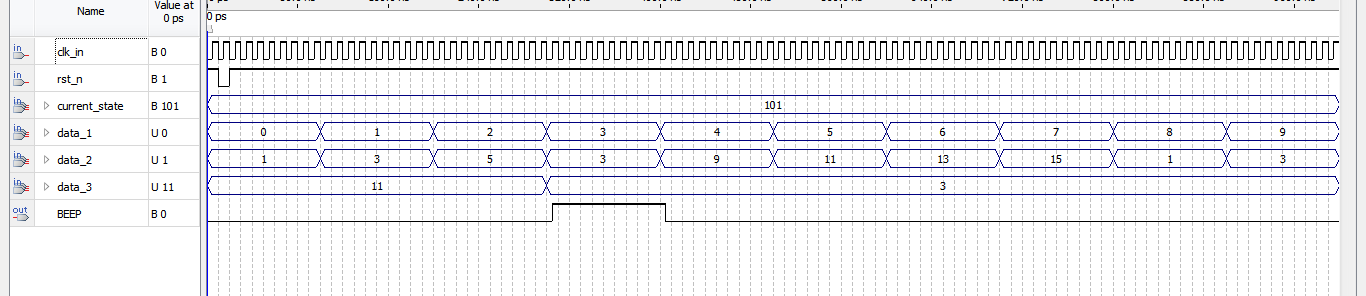

数据控制模块

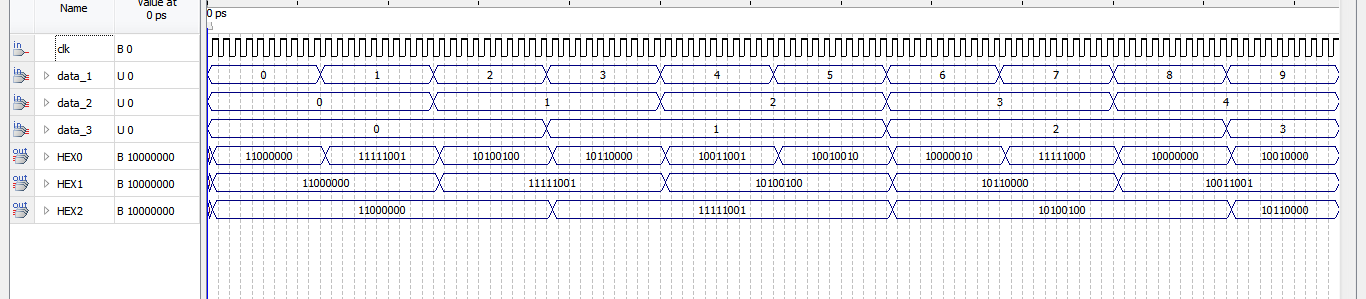

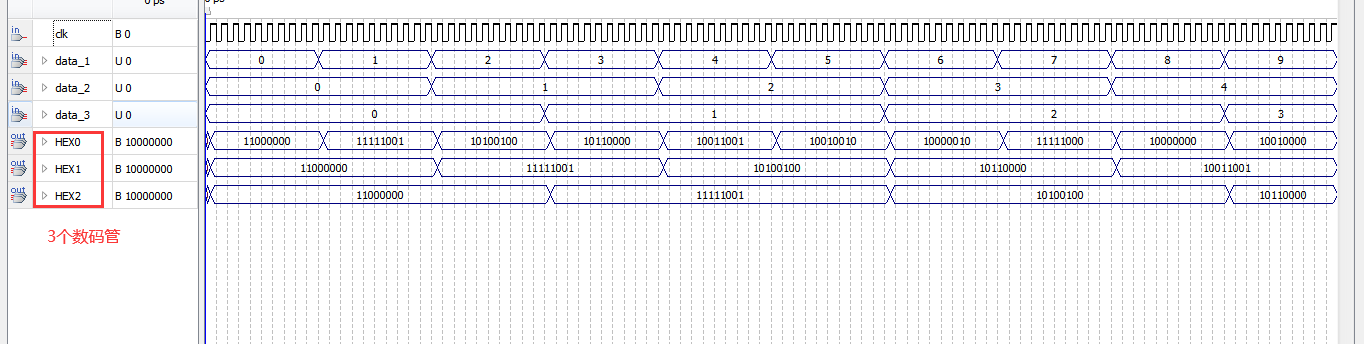

显示模块

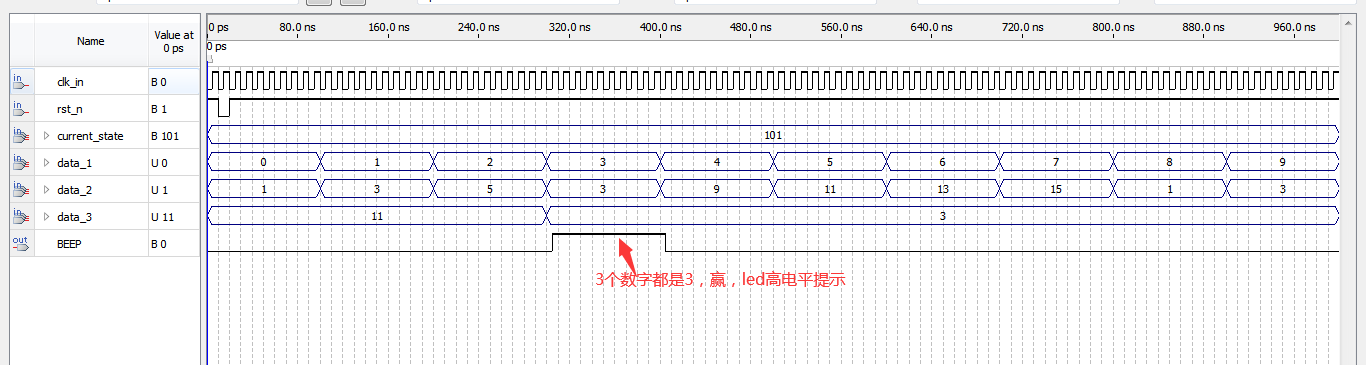

赢了提示模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --按键控制 ENTITY data_ctrl IS PORT ( clk_in : IN STD_LOGIC;--50MHz rst_n : IN STD_LOGIC;--复位 key : IN STD_LOGIC;--输入按键 current_state : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);--输出当前状态 data_1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数字1 data_2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数字2 data_3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--数字3 ); END data_ctrl; ARCHITECTURE behave OF data_ctrl IS constant s_idle : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; constant s_count : STD_LOGIC_VECTOR(2 DOWNTO 0) := "001"; constant s_cnt123 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "010"; constant s_cnt23 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "011"; constant s_cnt3 : STD_LOGIC_VECTOR(2 DOWNTO 0) := "100"; constant s_end : STD_LOGIC_VECTOR(2 DOWNTO 0) := "101"; SIGNAL cnt1 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL cnt2 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL cnt3 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL div_cnt_1 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL div_cnt_2 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL div_cnt_3 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL state : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; SIGNAL wait_1 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL wait_2 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL wait_3 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; BEGIN PROCESS (clk_in, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN--复位 div_cnt_1 = "00000000000000000000000000010000") THEN--5Hz div_cnt_2 <= "00000000000000000000000000000000"; ELSE div_cnt_2 <= div_cnt_2 + "00000000000000000000000000000001";--累加 END IF; END IF; END PROCESS; PROCESS (clk_in, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN--复位 div_cnt_3 <= "00000000000000000000000000000000"; ELSIF (clk_in'EVENT AND clk_in = '1') THEN IF (div_cnt_3 >= "00000000000000000000000000100000") THEN--2Hz div_cnt_3 <= "00000000000000000000000000000000"; ELSE div_cnt_3 <= div_cnt_3 + "00000000000000000000000000000001";--累加 END IF; END IF; END PROCESS;

源代码

点击下方的公众号卡片获取

500

500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?