冯诺伊曼结构是个 cpu 和主存储器的通信结构,一个通信过程时延可分为处理时延,传播时延,排队时延,三者共同构筑了内存墙。其中处理时延最核心也最无解,先看它。

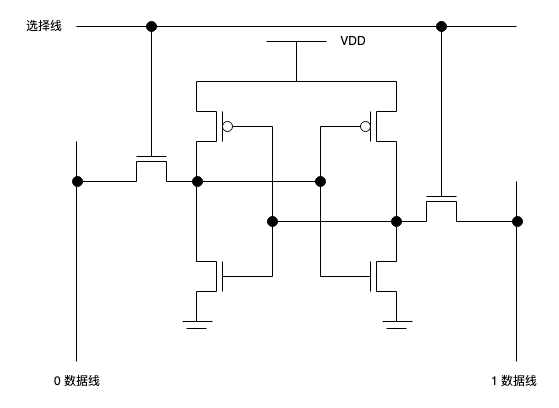

看个作为标准存储单元的双稳态触发器(至少教科书上就这样教的):

电路简单且高效,一次可直接读写 0 或 1。把这电路铺开,就能存储 8bit,32bit,1kbyte,1M,10M,100M…它可以存储任意大小的数据。

但世界不是线性堆砌的,再次推荐《规模-复杂世界的简单法则》。

在工程学上,系统工作原理一定会随着规模或尺度而发生变化,在本质上是由系统各部分的伸缩率不一致导致,这也是本文的升华,换在其它领域也合适。

一个双稳态触发器需要 6 个 MOS 管存储 1 个 bit,问题就是工程极限在哪里,这极限涉及到两方面,一个是技术极限,主要是人类目前的技术最大集成度,另一个是成本极限,即人们能承受多高的成本批量生产最大集成度的产品。

越来越多的 MOS 管集成在相对固定的面积上,逐渐逼近技术极限和成本极限,当继续这种线性扩展的集成方式变得不划算时,就要做个买卖,用另一种相对可承担的代价换更简单的存储,存储器的工作原理势必要改变,而这个代价就是时间,时间可换一切。

因此,上述双稳态触发器只能构建相对较小的存储器,比如 cpu cache。而相对更大的主存储器,存储单元一定更为简单,但操作速度肯定更慢,这是一笔买卖。

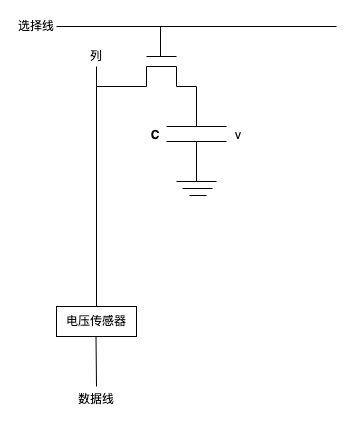

看主存储器的存储单元,它靠一个电容保存 0 或 1:

比双稳态触发器更简单,显然可集成度更高,适合做大存储。

如果双稳态触发器按照空间展开 “一次性” 读写 0 或 1,那么电容存储器则按照时间展开 “分步骤” 读写 0 或 1,一个时间换空间的 case:

- 选择线接通 MOS;

- 电压传感器往 “列” 线加 0.5*v 伏电压;

- 电压传感器感受到电压变化:如果 C 充电状态,电压传感器将感受到电压逐渐上升,反之则感受到下降;

- 如果电压传感器感受到升压,则往 “列” 线加压到 v 伏并给数据线高电平,同时充满 C 以弥补 “破坏性读”,如果感受到降压,则将 “列” 线直降到 0 并给数据线低电平,电容 C 放电。

电容存储器读写显然更慢,但存得更多了。

你不想摊得太大,你就要分很多步骤。你的书桌可以书本掀开,倒扣,摊得很乱,便于随手捡拾上次读到的那本书的那页码,但书房就不能这么搞,必须把书合上并堆叠在一起才能存放更多,取的时候也就要稍微费点事。

说回 cpu 内存墙。我们已经看到主存和 cpu 内部的 cache 相比是多么 “低效” 了,而这个低效又是个交易的固有结果,这堵内存墙已经被这买卖构筑了一大半。

传播时延同样不容小觑,而这依然和时间换集成度有关,又是个买卖。

一次向 cpu 传输大量数据还是多次传输少量数据,这涉及到内存总线宽度,而总线宽度和引脚数量直接关联,这又是个集成度的问题。

由于 cpu 和内存在空间上分离,它们间的部分没有 “硅属性”,换句话说内存,cpu 通道不是集成的,几乎就是焊在主板上的 “裸铜线”。与硅晶体在 < 10nm 级操作不同,铜线的尺度在 ms 级,二者相差 1000000 倍,并排几百根铜线想都别想。这意味着 32,64 根数据线已经够多了,如果要传输几 MB 的数据,必须往来很多次。

按照信号的传输速度 200000km/s,0.5ns 可传输 10cm 的距离,大概就是 cpu 到内存的尺度,往来 100 次就是 50ns,而 DDR5 的读写时延约 15ns,二者几乎在一个尺度,这与 tcp/ip 比就是龟速,相当于 sender 花 20ms 准备好 “浙江温州皮鞋湿” 这句名诗,然后花 20ms 从上海传输到广州,而实际上,sender 准备这句名诗的时间只在 ns 级,和传播时延差至少 5 个数量级。

如果内存读写要 15ns,传播要 50ns,总共 65ns 的时延,这对于 cpu 是必然要抱怨的,再加上多核 cpu 场景下还要拥塞控制,几乎就是 100ns 级时延了。

大容量几乎意味着廉价和共享,二者可以相互解释,没什么可抱怨的,追求性价比的心理对于构建多核心架构的分层存储体系非常必要。既然共享资源,就一定会出现拥塞,而拥塞控制的代价还是时间,这又是一个买卖,随着 cpu 核的增多,这买卖利润越低,越不好做。

以上就是 cpu 内存墙的本质。

最后要升华一下,我觉得冯诺伊曼结构构筑的 cpu 内存墙不是问题而是方案,正是这堵墙让计算机变得廉价可拥有,走向千家万户,走向几乎所有领域。

换句话说,分层存储体系就是可扩展性本身,而一味追求高效的 cpu cache 类存储是没有可扩展性的。如果从冯诺伊曼结构再往前,我们终将遇到图灵机,图灵机的读写头常用而不常有,而纸带无限,这是最基本的可扩性需求,也是图灵机时间换空间的精髓。

所以,不要嫌楼下的全家便利店贵了,你可以徒步去 800 米外的大润发超市,或者开车 1 小时去 30 公里外的批发市场。明白什么是可扩展性本身如何自噬就明白了世界的本质,到处都是内存墙,企图突破它既不可能,也没必要。

至于存内计算,往廉价的电容内存里增加晶体管,至于 DPU,至于在网计算,都需要一定的技术突破或发现新的物质,而不是堆砌现有的技术,否则,历史已经证明这种堆砌虽高效,但不划算。

浙江温州皮鞋湿,下雨进水不会胖。

893

893

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?