目录

1 Vivado调用VCS仿真

1.1 软件准备

VCS_MX_VO-2018.09-SP2:链接:https://pan.baidu.com/s/1tC5CSldNemZX9Kb4DjeYRQ 提取码:49b9

Vivado 2019.02:链接:https://pan.baidu.com/s/1dxS7AlAdW1Kosas7yd_P3A 提取码:9f56

注: 如果仿真软件下载链接有问题,请发邮件至909727985@qq.com,我再重新发一个。

注:用vcs仿真要在testbench中加入生成波形文件的语句。

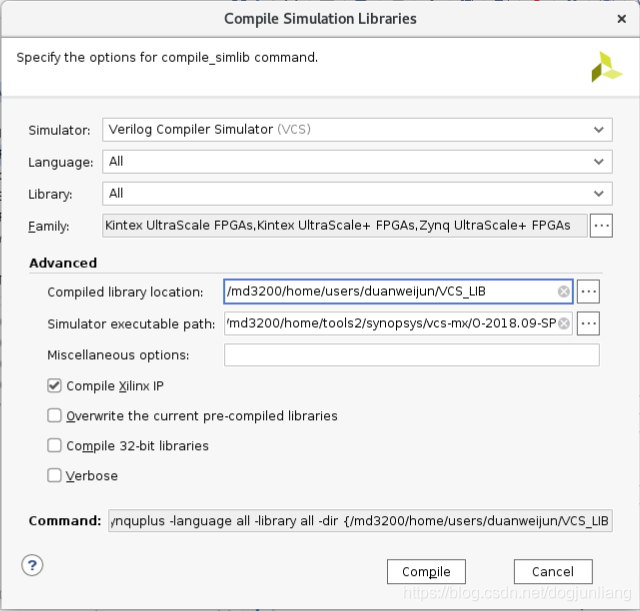

1.2 仿真库编译

仿真器选择:Verilog Compiler Simulator

编译库位置:自定义

仿真器路径:vcs_mx\O-2018.09-SP2\

ERROR:编译库出问题最多,首先是版本问题,版本最好使用MX版本的(可能的原因是Xilinx IP核多数是VHDL编写,有的是Verilog编写,所以需要混合编译), vcs_vO-2018.09-SP2这个版本的VCS也试过,没有编译通过。第二个就是权限的问题了,编译库成功后,Vivado调用VCS仿真,如果VCS未启动,最大可能的原因就是权限的问题了,此部分是公司IT帮忙解决。

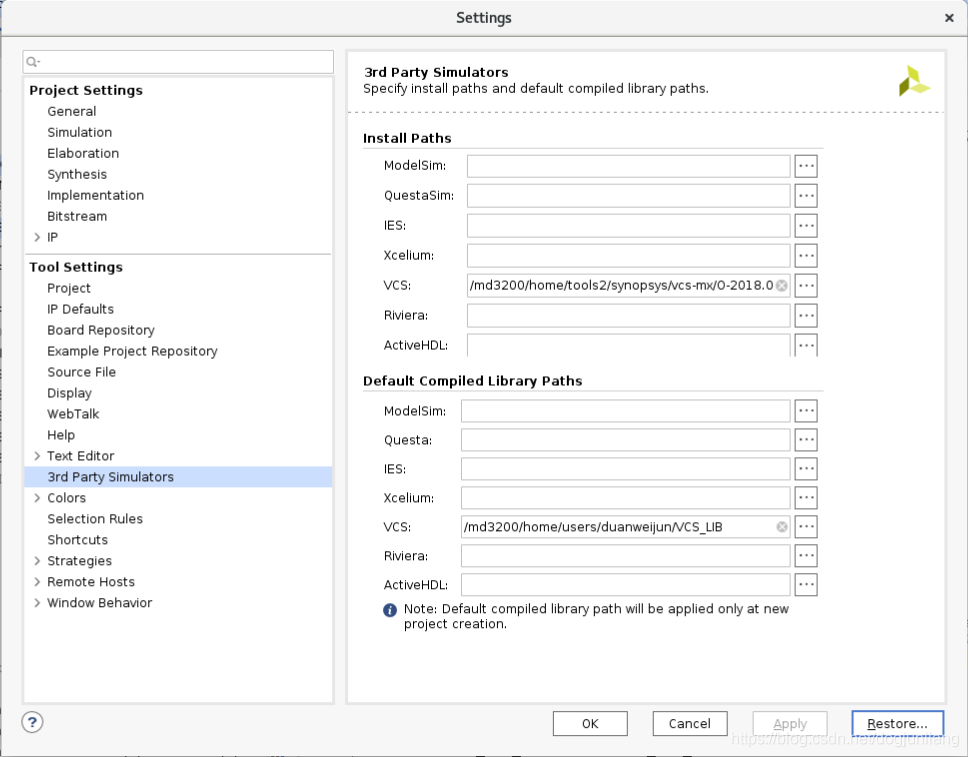

1.3 Vivado 2019.02第三方仿真软件配置

2 Vivado导出VCS脚本仿真

2.1 VCD文件生成

在testbench中加入以下语句:

initial

begin

$dumpfile("tb.vcd");

$dumpvars();

end2.2 FSDB文件生成

fsdb文件是verdi使用一种专用的数据格式。类似于VCD,但是它是只提出了仿真过程中信号的有用信息,除去了VCD中信息冗余,就像对VCD数据进行了一次huffman编码。

VCD文件使用verilog内置的系统函数来实现的,fsdb是通过verilog的PLI接口来实现的, $fsdbDumpfile,$fsdbDumpvars 等。因此fsdb数据量小,而且会提高仿真速度。

initial

begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars();

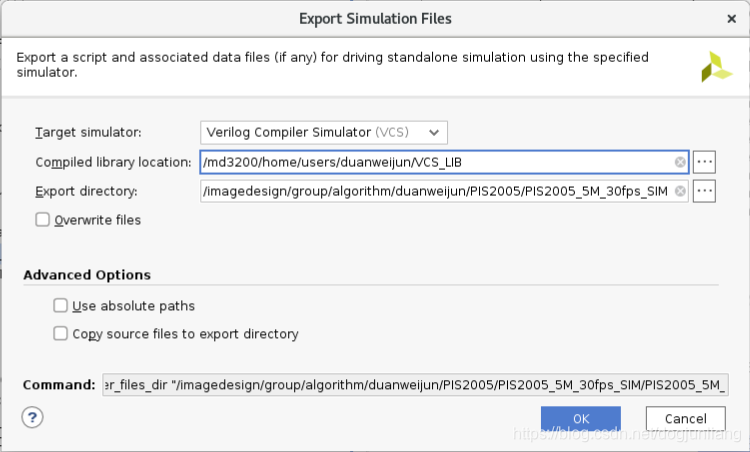

end2.3 导出脚本

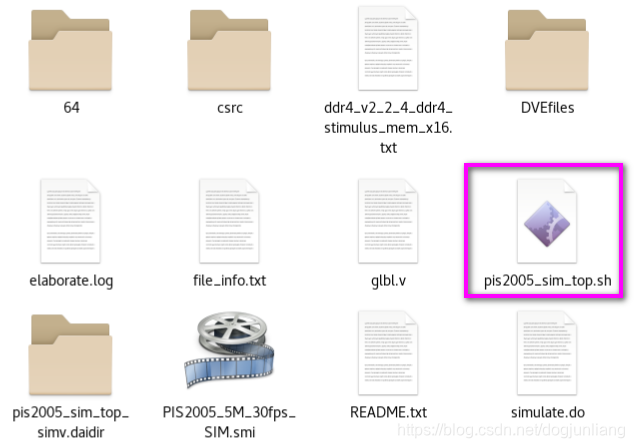

2.4 VCS编译

在命令行中运行vcs下的top_tb.sh脚本。

2.4 DVE查看波形

执行到出现 gs232 initial begin 没有报错就成功在vcs目录下生成波形文件了,将波形文件加载到dve或者verdi中就可以了。

参考博文

1. VCS+Verdi 安装及破解过程(亲测可用,包含形式验证工具安装) - 简书 (jianshu.com)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?