本文是针对此篇论文写的学习笔记:

Wenjie Mao ; Yaping Zhou ; Aniket Naik ; Sunil Sudhakaran (2013) Study of BGA package cap for high-performance computing GPU, Denver, CO, USA: IEEE.

学习目的

- 工作时遇到芯片power急速上升的情况, 这会造成供电电压瞬间下降, 如果这个电压低于某个安全值, 就会造成芯片功能出错, 后果很严重. 通常会通过降最大频率的方式来让芯片平稳度过电压不足的风险. 反过来说, 如果这个droop变小了, 就可以换取更快的频率, 芯片的性能也会提升.

- 这篇文章讲了Nvidia 在2013年的GK110核心也遇到同样的问题, 最终NV的工程师评估了各种手段来加package上的cap(电容), 以此减少了droop voltage. 效果喜人.

具体内容

GK110 是个什么样的芯片

- GK110, Kepler架构, TSMC28nm, 561mmsq, 很凶悍

- 2013年发布, 搭载这款芯片最著名的显卡就是GeForce GTX TITAN, 可见功耗之凶猛.

- 完整的芯片包括2880个shader, GPU clock: 902MHz(Quadro K6000 SDI). Max TDP 250W

参考网站: techpowerup.

遇到什么样的问题

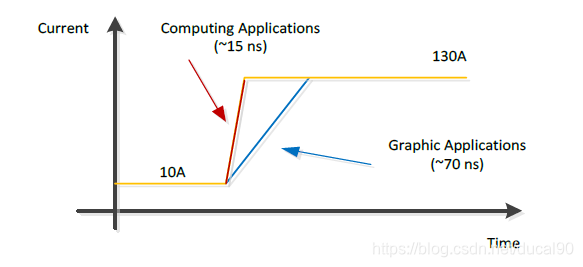

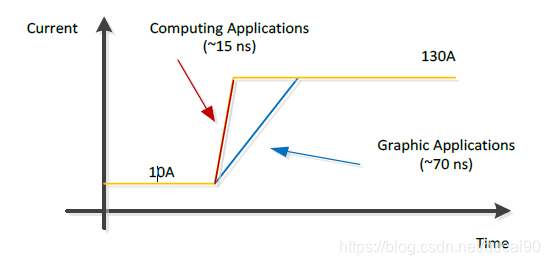

简单说来, 就是拿这款GPU来跑图形应用(游戏, 图形计算, 多媒体等等), 此处是跑了traditional stressful graphic application(比如3DMark), 电流上升的没有那么快(蓝线).

但是当去跑Linpack performance benchmark时, 所有Unit都同时工作起来, 导致电流上升的很快(红线), 15ns 就从10A飙到130A.

这对GPU power delivery来说是个挑战. 因为在之前GPU都是跑图形应用, 看到的slew rate 很小, 设计package时都不用考虑cap, 因为这么小的noise 可以被板子上靠近chip的cap给滤掉, 这样显卡的成本就降低了.

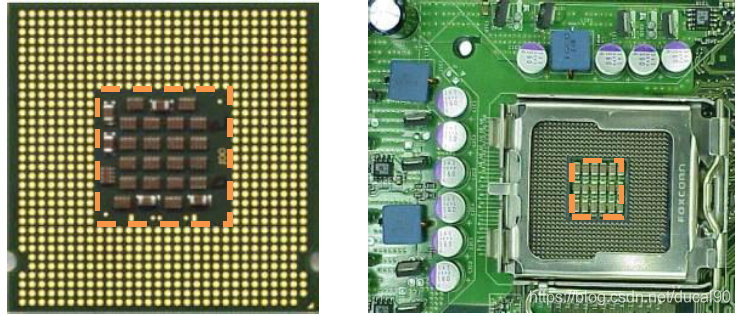

如果是高性能CPU, 就会考虑skew rate太大的问题, 那么会用到PGA(Pin Grid Array) 的pacakage技术, 这种技术需要socket来装在PCB板上, 这样会增加板子和package之间的电感(这不好), 所以要加额外的cap来抵消, 不过好在socket能给cap提供额外空间. 这种电容叫去耦电容(decoupling), 它们在供电电路的瞬态、高电流需求期间向电路提供电流的局部能量小储存器,防止电源轨上的电压被瞬时电流负载拉低. 所以高性能CPU对于高di/dt slew rate的解决方案很robust.

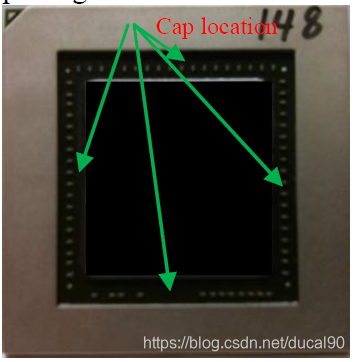

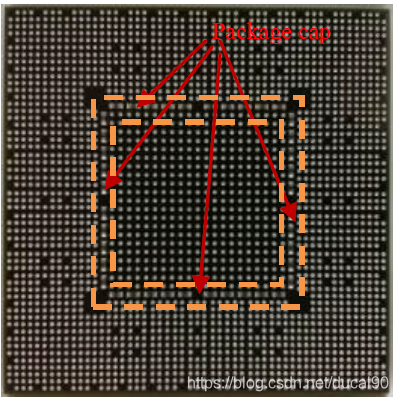

GPU一般使用BGA(Ball Grid Array) package 技术. BGA是把package直接焊在board上, 这样电感小.所以GPU上的去耦电容都在板子背面. 这足以应对之前GPU遇到的慢slew rate. 而且空间限制也不允许加更多cap. 下图高亮区内加cap最有效, 区域外的cap效果很差. 显然以前的package技术不能解决现在的问题了.

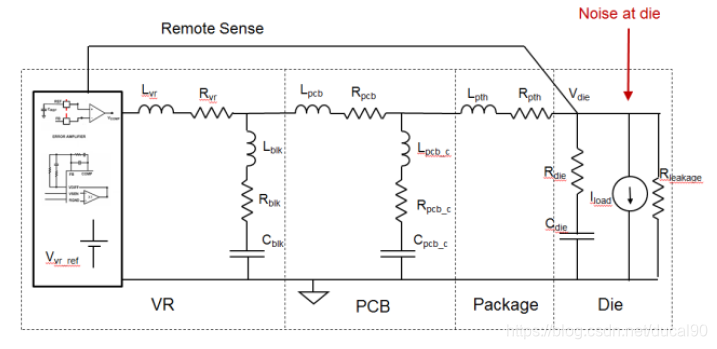

怎样simulate/measure power noise

想要知道die上current的变化会导致怎样的droop, 需要建立一个power delivery simulation model. Power supply 用的是5-phase buck converter. 测量就直接测die上noise.

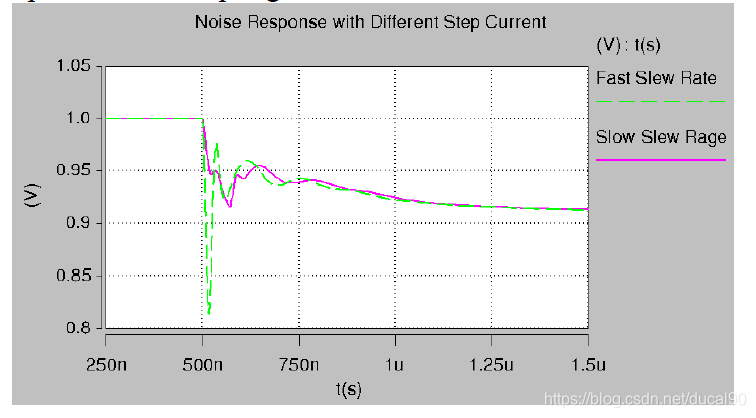

然后产生两种current变化来表示GPU在跑不同应用时遇到的电流变化情况. value一样只是slew rate 不同.

simulation结果

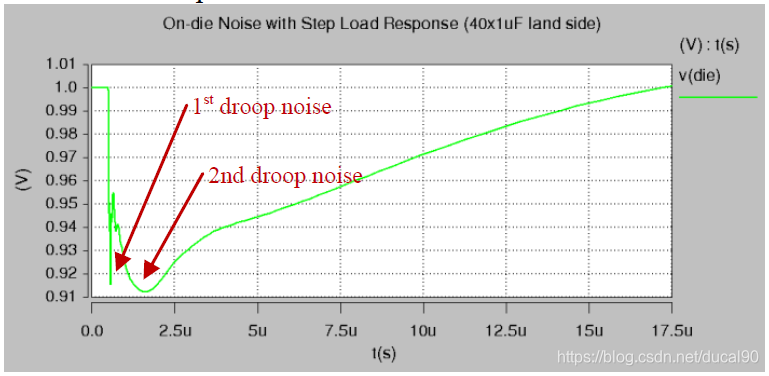

由图可见, 最大的droop发生在第一次droop上, 说明迅速上升的电流造成了第一次droop很大. 而第二第三次的droop不大, 这说明中低频的cap足够多了. 高频去耦电容不够. 因为之前说的GPU board上没什么地方放cap了, 所以得想办法在package上放cap.

这种high slew rate 造成了170mv的noise. 这会非常影响GPU performance.

学习package cap

首先来看cap可以加在哪里.

- die side, 在package cap 的顶端可以放cap, 而且没有高度限制. 但是这个cap不好和major power plane 联. 因为芯片周围都是I/O interface. 连接不当会导致额外的电感.

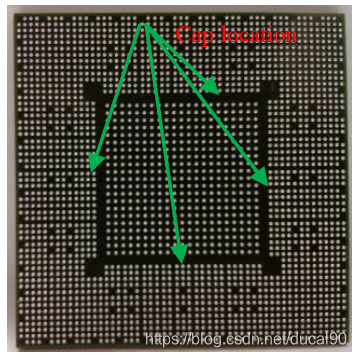

- land side, package 的最下面一层, 在I/O和core area之间有些小缝隙, 这里可以放land side cap. (首选)

- embedded cap, 在GPU芯片的背面. 但是当这种cap太多, 会影响yield. 所以不考虑.

作者还用仿真详细比较了land side cap 和die side cap, 最后结论也是land side cap 要好一些. 过程不再赘述.

因为package ball 有高度限制, 最大可以选的land side cap 是 low profile 0402, 多少cap 才够呢.

通过做时域simulation. 发现on die noise 的第一第二droop noise 很接近. 这说明40x0402 1uF 足够控制droop了.

作者还比较了不同的cap value对结果的影响, 结论是1uF的比较好.

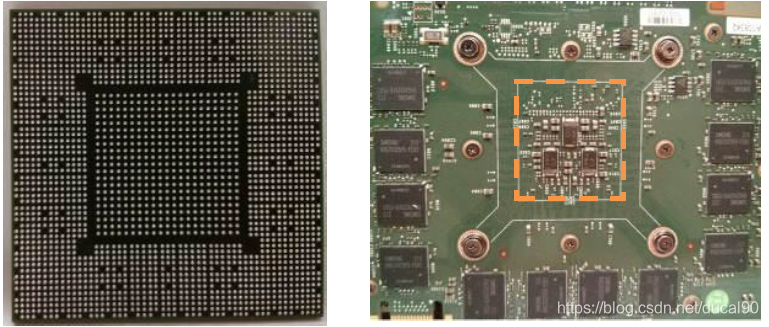

又做了cap 种类的比较, 40x1uF reverse geometric cap and 40x1uF 3-terminal cap. 3-termial caps 效果比较好. 但是最后没有用上, 因为MLCC 已经足够好了. 如图, land side cap 就加在 黄色框内.

结果

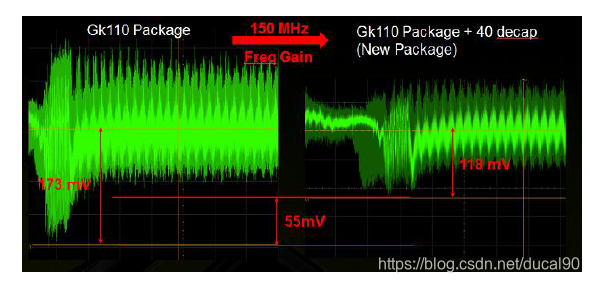

在linpack的current profile下, 做了带cap 和不带cap 的simulation. 结果发现die noise 从153.5mv 提升到了 107.4mv (越小越好). 30% noise 提升.

实际板子上测试的情况:

感叹一下NV真的做了两次package. 不带cap的(左边), 带cap的(右边)

减少了55mV noise, 这与simulation结果吻合. 55mv noise reduction相当于150MHz GPU CLOCK 的提升. 这个提升很喜人.

本文是关于研究BGA封装电容用于高性能计算GPU的学习笔记。工作中芯片功率急速上升会致供电电压下降,影响芯片功能。以GK110芯片为例,分析其在不同应用场景下的电流变化及电源噪声问题,通过模拟测量,研究在封装上加电容来减少电压降,最终取得较好效果,提升了GPU性能。

本文是关于研究BGA封装电容用于高性能计算GPU的学习笔记。工作中芯片功率急速上升会致供电电压下降,影响芯片功能。以GK110芯片为例,分析其在不同应用场景下的电流变化及电源噪声问题,通过模拟测量,研究在封装上加电容来减少电压降,最终取得较好效果,提升了GPU性能。

1276

1276

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?