上一期介绍了车规芯片PI方面面临的挑战以及优化策略,本期再重点介绍SI方面的挑战和优化策略。

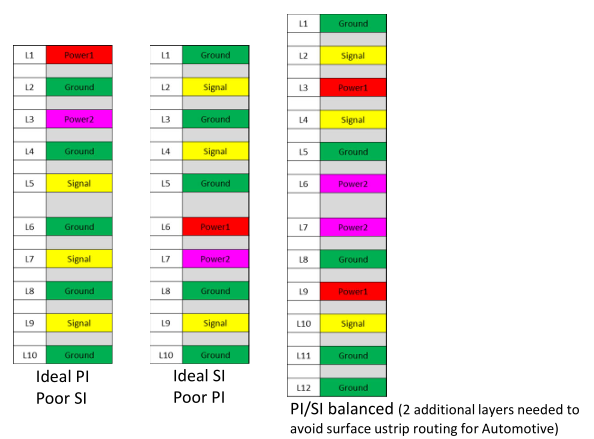

层叠定义方面trade-off SI/PI

层叠结构分配需平衡电源完整性与信号完整性。合理的层叠结构设计能减少电源噪声对信号的干扰,同时确保信号的传输质量,例如恰当安排电源层、地层和信号层的位置与间距。

需要考虑如下因素:

-

DSC 放置:尽可能将 DSC(die side cap)放置在靠近芯片(die)的位置。这样可以缩短信号传输路径,减少信号延迟和损耗,降低电磁干扰(EMI)的可能性,提高系统性能。如果考虑DSC的滤波性能就需要将Power层安排在CORE层的上方靠近DIE的位置,以保证DSC到DIE的环路电感最小化。

-

连接性: 确保从芯片到 DSC 再到 BGA(球栅阵列)的连接具有最佳的回流路径。良好的回流路径有助于提升电源和信号的稳定性,保障系统可靠运行。

-

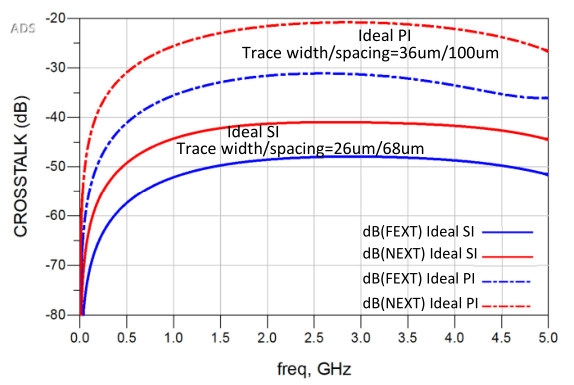

减少串扰:在最小化信号间距的同时减少串扰。

左侧层叠就是对PI最有利的层叠,power层分别在L1和L3层,DSC的滤波环路最小。而信号层分别在L5/7/9层,尤其是L5层由于两个参考平面中L6层较远,相同阻抗下L5层的线宽要比其它布线层更粗,保证串扰的情况下需要更大的布线间距。

中间层叠将Power层放到CORE层以下,由于L5-L6层的CORE层较厚,会极大的增大DSC的环路电感。这种层叠对PI不友好,但对SI比较有利。布线层分布在L2/L4/L9层,均可最小的线宽和间距实现阻抗和串扰控制。

串扰的对比如下:

最右侧层叠为平衡SI/PI性能的层叠。缺点就是增加了两层,导致成本的上升。而且L2/4/10三个信号层均存在单面参考GND、另一面参考电源层的情况。

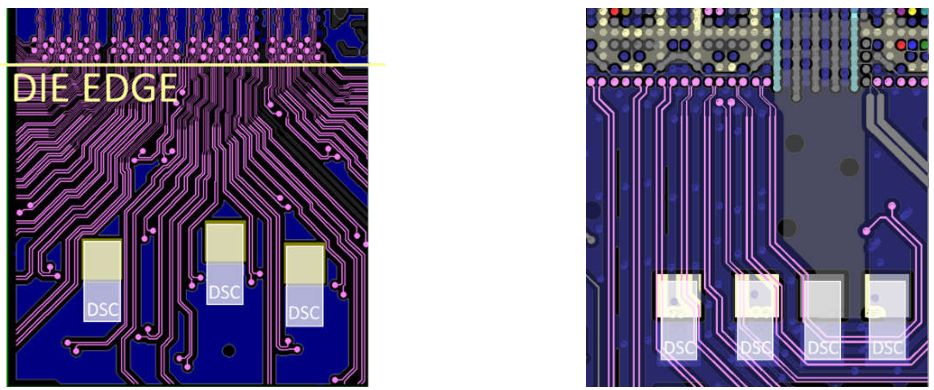

DSC导致布线空间受限

DSC的放置限制了表层微带线的布线区域,并减小了布线间距。这就意味着布线串扰的增加。设计时需要综合考虑SI/PI来确定DSC的数量以及布局位置。

由于空间受限,一些高速IO的布线已经可能会进入DSC电源/地孔的void区域。导致高速信号参考平面的不完整、进而导致阻抗突变和串扰增加。

上述两个因素都会恶化信号的SI性能,需要在设计中重点关注。

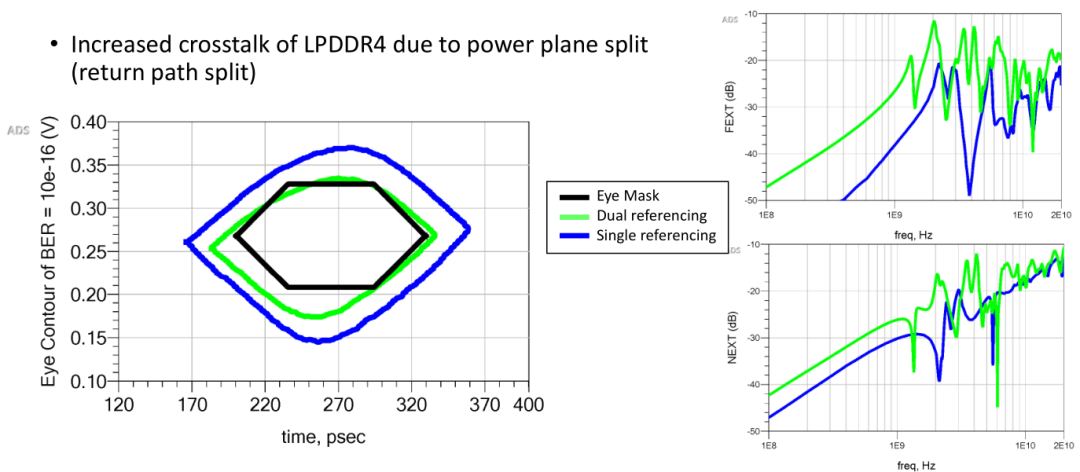

参考平面对DDR SI的影响

带状线布线受成本限制经常使用信号线参考层处理电源,会出现布线跨分割的情况, 这就会导致 LPDDR4的串扰增加。电源平面分割可能会破坏信号回流路径的完整性,使得信号之间的相互干扰加剧。

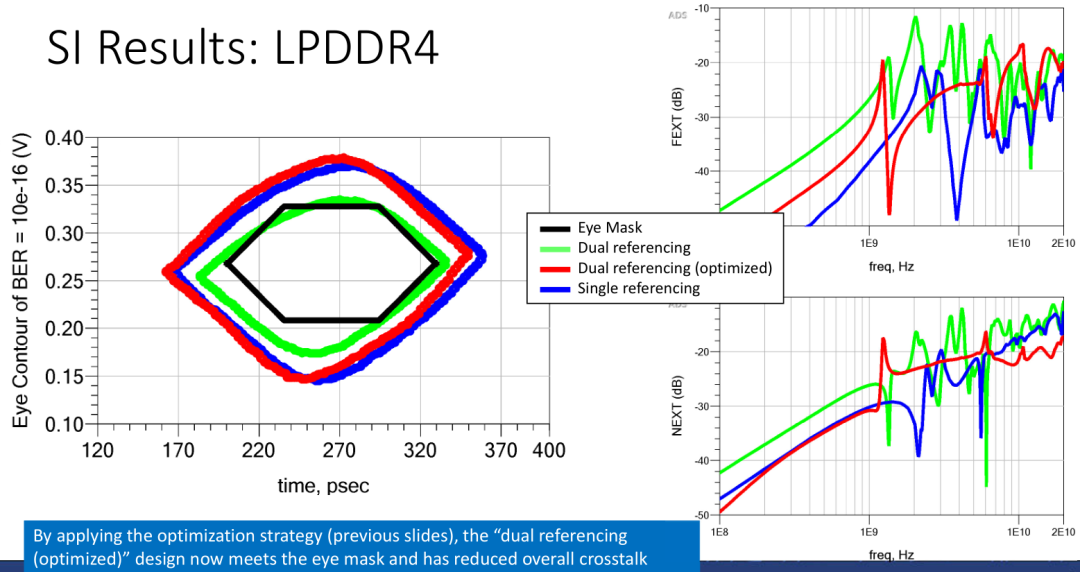

左侧眼图:展示了不同参考方式下的眼图。“Dual referencing”(绿色)表示带状线布线参考平面为不同网络(存在跨分割)情况下眼图,“Single referencing”(蓝色)表示两个参考平面均是Ground情况下的眼图。可以看到“Dual referencing”的情况眼图明显较“Single referencing”情况更差。

右侧图表:分别为远端串扰(FEXT)和近端串扰(NEXT)与频率的关系。绿色曲线代表“Dual referencing”下的串扰情况,蓝色曲线代表“Single referencing”下的串扰情况。可以看出,“Dual referencing”的串扰表现明显更差一些。这和眼图的仿真结果一致。

优化策略:在参考平面存在电源分割时,首先硬件尽量减少电源平面切割,并使其更靠近芯片bump。这样做可以显著改善串扰,同时可能对降低电磁干扰也有帮助。

换层过孔的优化策略

信号间的过孔串扰,是影响DDR等高速并行总线SI性能的管脚因素,这一节讨论过孔的串扰如何优化。

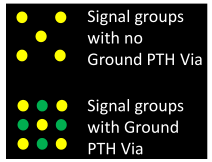

有无GND过孔的串扰对比:

上图两个过孔结构,上面是5个signal过孔(黄色)没有GND孔;下图5个signal孔并交错放置绿色GND孔。近端串扰和远端串扰的对比如下:

可以看到增加GND过孔后,远端串扰和近端串扰都降低了14dB,有非常大的改善。由此可见在DDR等高速并行信号过孔附近增加GND过孔是降低串扰的重要手段。

总结

通过前面的优化策略,最终在“Dual referencing”(存在跨分割)的情况下将LPDDR4优化到满足黑色mask的程度。

车规电子产品,包括更高的可靠性和温度要求、AEC - Q 认证以及更低的百万缺陷率(DPM)目标,给满足片上系统(SoC)设计中的信号和电源完整性需求带来了新的挑战。

由于市场上符合 AEC - Q200 标准的元器件有限,以及存在额外的热 / 机械应力(这需要板级底部填充、芯片侧去耦、厚封装基板芯板以及更多非关键功能的球栅阵列(BGA)),电源完整性面临挑战。

信号完整性面也临高速信号参考平面不完整、布线空间受限以及在split、void上布线的风险等挑战。

通过对封装层叠分配、芯片侧电容放置、合理的信号/地孔的放置以及其他布线优化进行战略性规划,才能够在满足车规要求的同时实现SI/PI的性能目标。

1027

1027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?