IWDG 简介

独立看门狗本质上是一个定时器,这个定时器有一个输出端,可以输出复位信号。该定时器是一个 12 位的递减计数器,当计数器的值减到 0 的时候,就会产生一个复位信号。如果在计数没减到 0 之前,重置计数器的值的话,那么就不会产生复位信号,这个动作我们称为喂狗。看门狗功能由 VDD 电压域供电,在停止模式和待机模式下仍然可以工作。

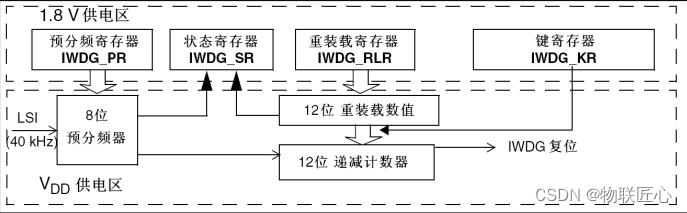

IWDG 框图

下面先来学习 IWDG 框图,通过学习 IWDG 框图会有一个很好的整体掌握,同时对之后的

编程也会有一个清晰的思路。

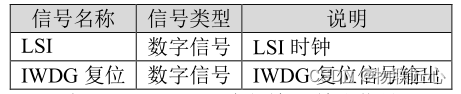

从 IWDG 框图整体认知就是,IWDG 有一个输入(时钟 LSI),经过一个 8 位的可编程预分频器提供时钟给一个 12 位递减计数器,满足条件就会输出一个复位信号。IWDG 内部输入/输出信号如下表:

STM32F103 的独立看门狗由内部专门的 40Khz 低速时钟(LSI)驱动,即使主时钟发生故障,它也仍然有效。这里需要注意独立看门狗的时钟是一个内部 RC 时钟,所以并不是准确的40Khz,而是在 30~60Khz 之间的一个可变化的时钟,只是我们在估算的时候,以 40Khz 的频率来计算,看门狗对时间的要求不是很精确,所以,时钟有些偏差,都是可以接受的。

IWDG 寄存器

IWDG 的框图很简单,用到的寄存器也不多。我们主要用到其中 3 个寄存器

键寄存器(IWDG_KR )

键寄存器可以看

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1506

1506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?