对SPI的理解

-

仔细看手册

(1) 框图

接收和发送只有一个移位寄存器,这是和UART不同的。所以单主机和单从机的接线如下所示,其实连接后是由两个移位寄存器组成的环形链路,收发可同时进行,才叫全双工。

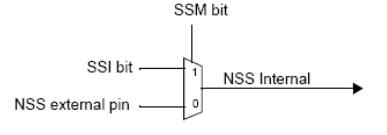

另外,要注意NSS的控制。NSS(Negative Slave Select),意为“低电平有效的从器件选择”信号。从SPI的结构框图中可以看到NSS也是外部引脚的名称,其实控制SPI收发数据时通过内部的NSS信号实现的,而这个内部的NSS信号源可以由SPI_CR1寄存器的SSM(Software slave management)位来配置:

SSM=1,被称为“软件模式”,内部NSS信号电平由SPI_CR1寄存器的SSI位决定。这种模式适合在SPI被配置为主机时使用,配置为主机时需要把SPI_CR1寄存器的MSTR和SPE置1,SSI也置1。

SSM=0,被称为“硬件模式”,内部NSS信号电平由NSS引脚电平决定。在这种“硬件模式”下要用SPI_CR2的SSOE(Software slave SS output enable)位来控制NSS作为输入还是输出,当SSOE=0时,NSS引脚被配置为输入;当SSOE=0时,NSS引脚被配置为输出。

(2) 功能描述

把SPI看做一个环形的数据链路是最好的理解方法,另外SPI的数据还可以通过DMA来管理。关于NSS的配置,网上有人说在主机模式下使用上述的“硬件模式”时NSS引脚无法根据发送数据的情况自动置高或拉低(主机发送数据时自动拉低NSS引脚选通从设备,发送数据结束时又自动置高NSS引脚)。

当SPI配置为“硬件模式”后,其实是通过检测NSS可以实现的是自身主机和从机模式的切换,而不是大多数人所认为的自动NSS。也就是说:在一个多SPI系统中,SPI通过NSS检测,一旦发现系统中无NSS低信号,自己就输出低,从而成为主机;当系统中有NSS低信号时(及已经有其它SPI宣布为主机),自己就配置为从机。 所谓的“硬件模式”的NSS,实际就是为了实现多机间通信的。所以在手册中关于SSOE的说明才是这样的:

Bit 2 SSOE: SS output enable

0: SS output is disabled in master mode and the cell can work in multimaster configuration

1: SS output is enabled in master mode and when the cell is enabled. The cell cannot work

in a multimaster environment.

其实所谓的“自动NSS”叫做“NSS Pulse Mode”,即NSS脉冲模式,这种模式才是网友们所需要的。目前为止我接触过的STM8S,M0,M3,M4中都没有这种功能。而在GD32F350和STM32F7xx中是有“NSS Pulse Mode”模式的。以下是STM32F7xx参考手册中的内容:Bit 3 NSSP: NSS pulse management

This bit is used in master mode only. it allows the SPI to generate an NSS pulse between two

consecutive data when doing continuous transfers. In the case of a single data transfer, it

forces the NSS pin high level after the transfer.

It has no meaning if CPHA = ’1’, or FRF = ’1’.

0: No NSS pulse

1: NSS pulse generated

Note: 1. This bit must be written only when the SPI is disabled (SPE=0).

2. This bit is not used in I2S mode and SPI TI mode.

949

949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?