Sigrity Aurora

1. 介绍

Cadence Sigrity Aurora为处于设计前期、中期以及后期布局的PCB设计提供了传统的信号和电源完整性(SI/PI)分析。继承了Cadence Allegro PCB编辑和布线技术,Sigrity Aurora用户可以在设计周期早期通过“假设”探索场景进行分析,以设置更为精确的设计约束并减少设计迭代。

2. 产品优势

- 通过设计中的SI/PI分析弥合设计和分析之间的差距

- 将Sigrity分析引擎与Allegro紧密结合实现设计画布

- 无需任何SI模型即可快速筛选SI问题的设计

- 使用最新的Allegro系统捕捉画布对假设的拓扑电路仿真

- 加快设计成功的时间,同时降低最终产品的成本

- 在约束驱动流中提供设计中的SI/PI分析

3. 产品特征

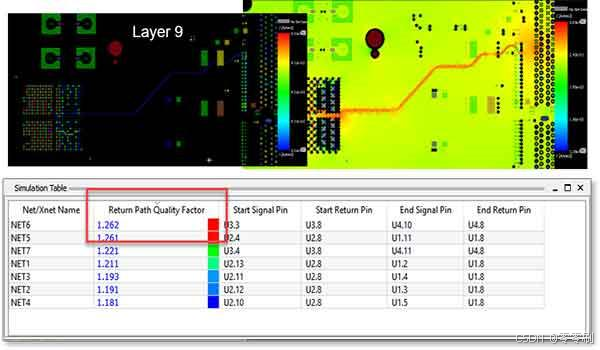

Sigrity Aurora直接对Allegro PCB的数据库进行读取和写入,快速准确地集成设计和分析结果。它提供了一个基于SPICE的模拟器和Sigrity为提取2D和3D结构的嵌入式混合场解算器。支持功率感知IBIS(行为)模型,如有必要,还可支持晶体管级模型。对所有相关信号进行全面分析可在布局前或布局后对高速信号进行探索,以比较备选方案。

DC PI分析对源级和汇级间的任何电压压降进行测量。其结果在设计画布上可视化为电压、电压压降或电流密度。设计师无需离开Allegro PCB执行画布即可更改设计并快速发现更改的影响。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1237

1237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?