FPGA 黑金开发平台学生版 2014 款正式发布了,此款开发平台是在前两款

学生版的基础上升级而来,型号为: AX301。虽然是一款入门级的 FPGA 开发

平台,但是我们不管是在 PCB 设计上,还是在整个构造上都花费了很多的心思,

真可谓“简约而不简单”。

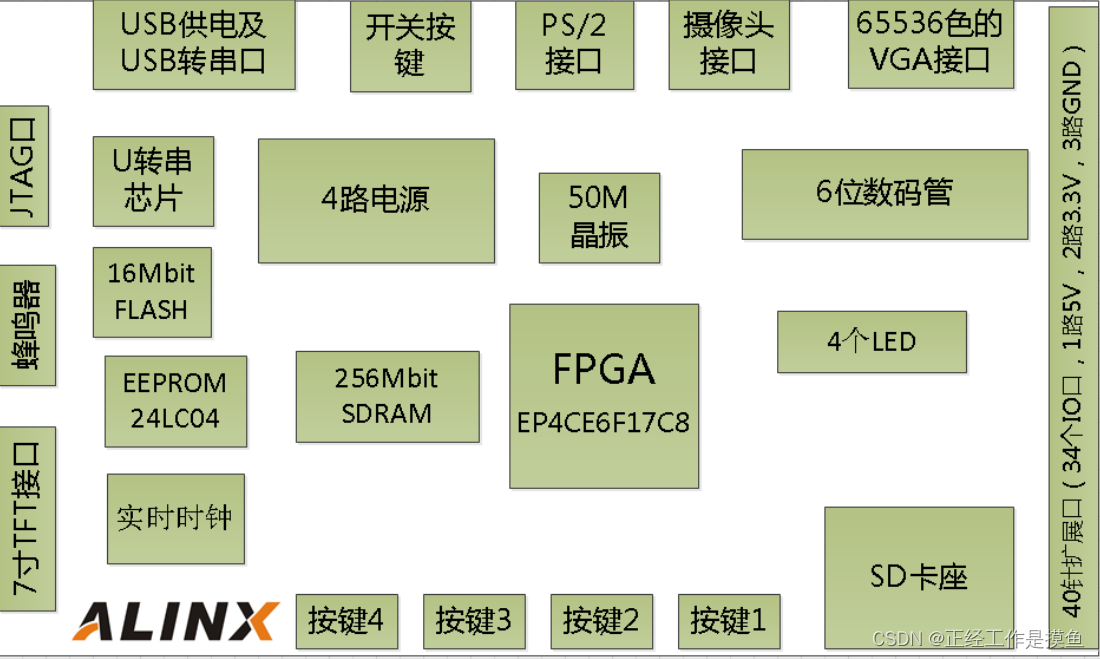

这个是系统整个的功能框图

本设计使用开发板上的FPGA与DS1302通信实现万年历的功能,可以利用按键进行修改ds1302的数值,设计一共有4个按键,功能分别如下

key1:修改选择按键,此键的功能是按动后,数码管显示的相应数据进行闪烁,并配和key2和key3按键进行数据修改。

key2:数据加按键。此键的功能是在正常时间显示模式下切换成日期和星期显示,在修改(年月时分秒周)状态下,对数据进行加一操作

key3:数据减按键。此键的功能是在正常时间显示模式下切换成12时或者24时,在修改(年月时分秒周)状态下,对数据进行减一操作。

key4:负责整个系统的复位。

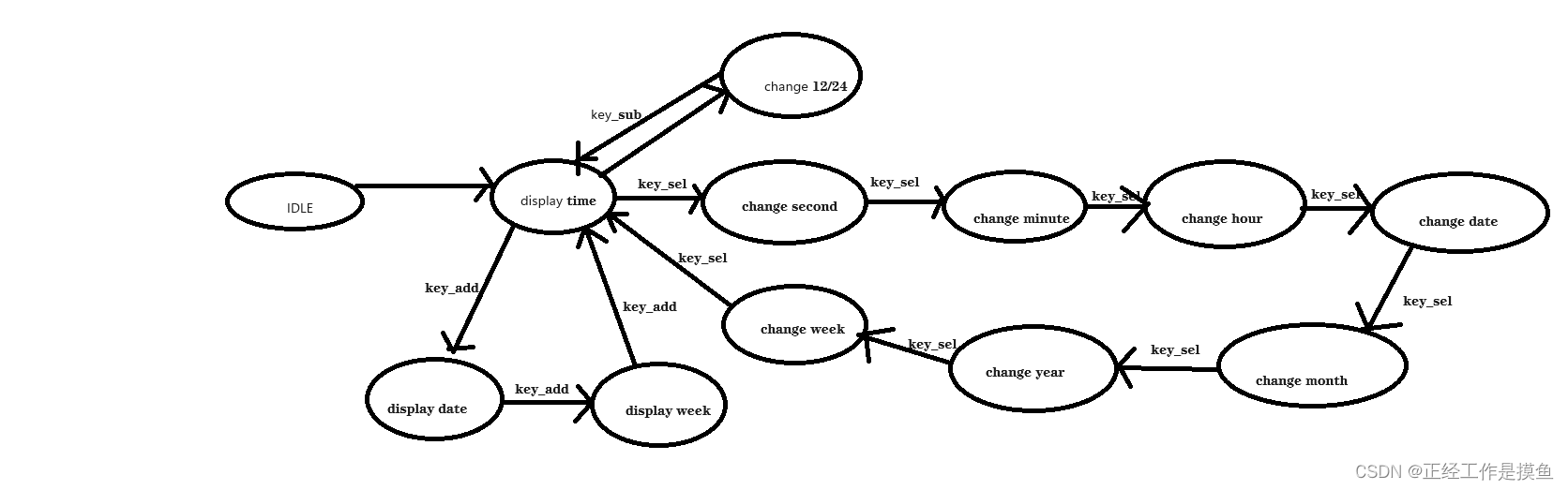

在功能切换时,使用了状态机的设计方法,利用按键按下作为状态转移条件,下面是状态转移图,

在修改时按动key_sel后就会把数据值写入ds1302

在读写ds1302时,需要进行仲裁,就是当读写请求都来临时,需要先做什么

我的思路时先进行读,读完一次时间数据,判断当前是不是有写入请求,如果有,执行相应的写入操作,如果没有,进行下一次读取

仲裁也是采用状态机设计,下面是状态定义

localparam IDLE = 4'd0 ;

localparam READ_REG = 4'd1 ;

localparam WAIT_READ_DONE = 4'd2 ;

localparam CHECK_REG_YEAR = 4'd3 ;

localparam CHECK_REG_MONTH = 4'd4 ;

localparam CHECK_REG_DATE = 4'd5 ;

localparam CHECK_REG_HOUR = 4'd6 ;

localparam CHECK_REG_MINUTE = 4'd7 ;

localparam CHECK_REG_SECOND = 4'd8 ;

localparam CHECK_REG_WEEK = 4'd9 ;

localparam WRITE_REG = 4'd10;

localparam WAIT_WRITE_DONE = 4'd11;

localparam WRITE_REG_DONE = 4'd12;

有这个状态机决定下一步操作时都还是写ds1302.

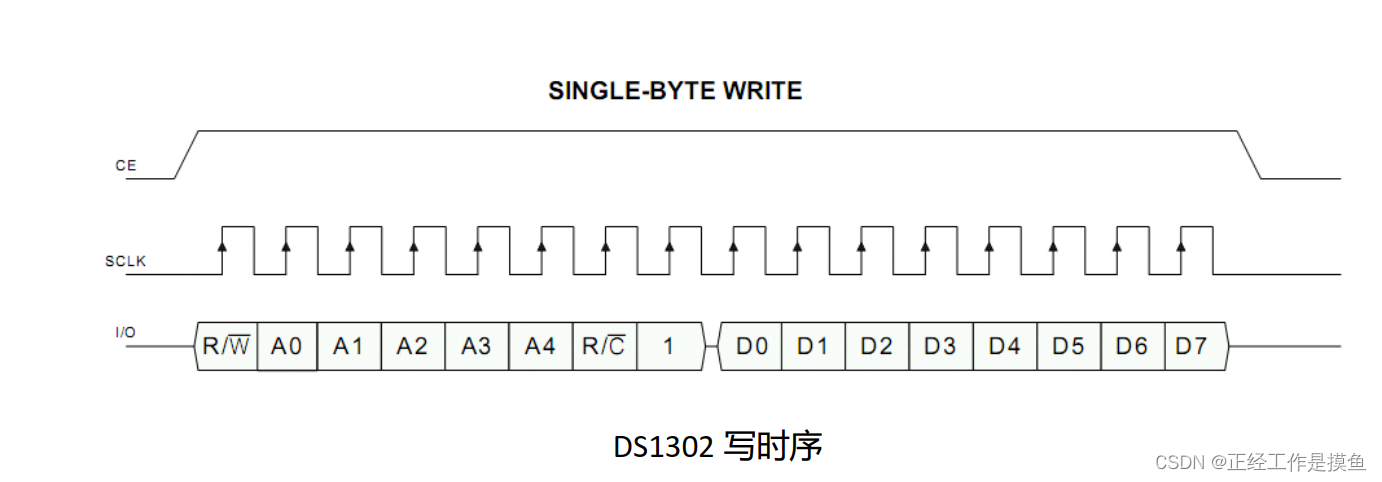

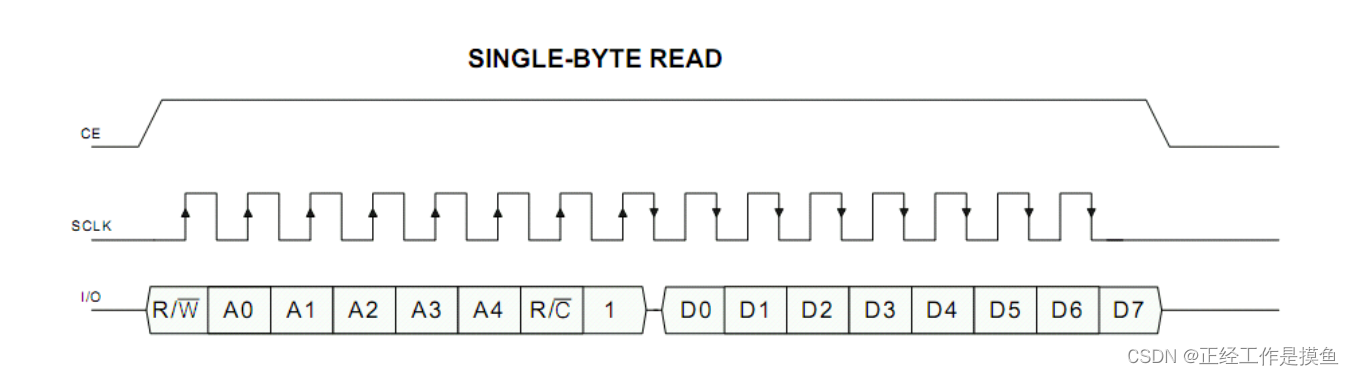

与ds1302进行数据通信时,由于通信协议非常类似于SPI总线,区别是MOSI和MISO分时复用,因此采取了一个线性序列机的写法,下面是ds1302通信时序图和线性序列机对应的操作。

写操作:

读操作

操作进程

| cnt | write | read | ||||||

| CE | SCLK | IO | IO_DIR | CE | SCLK | IO | IO_DIR | |

| 0 | 1'b1 | 1'b0 | io=addr[0] | O | 1'b1 | 1'b0 | io=addr[0] | O |

| 1 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 2 | 1'b1 | 1'b0 | io=addr[1] | O | 1'b1 | 1'b0 | io=addr[1] | O |

| 3 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 4 | 1'b1 | 1'b0 | io=addr[2] | O | 1'b1 | 1'b0 | io=addr[2] | O |

| 5 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 6 | 1'b1 | 1'b0 | io=addr[3] | O | 1'b1 | 1'b0 | io=addr[3] | O |

| 7 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 8 | 1'b1 | 1'b0 | io=addr[4] | O | 1'b1 | 1'b0 | io=addr[4] | O |

| 9 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 10 | 1'b1 | 1'b0 | io=addr[5] | O | 1'b1 | 1'b0 | io=addr[5] | O |

| 11 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 12 | 1'b1 | 1'b0 | io=addr[6] | O | 1'b1 | 1'b0 | io=addr[6] | O |

| 13 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 14 | 1'b1 | 1'b0 | io=addr[7] | O | 1'b1 | 1'b0 | io=addr[7] | O |

| 15 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | ||||

| 16 | 1'b1 | 1'b0 | io=data[0] | O | 1'b1 | 1'b0 | ||

| 17 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[0]=io | I | ||

| 18 | 1'b1 | 1'b0 | io=data[1] | O | 1'b1 | 1'b0 | ||

| 19 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[1]=io | I | ||

| 20 | 1'b1 | 1'b0 | io=data[2] | O | 1'b1 | 1'b0 | ||

| 21 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[2]=io | I | ||

| 22 | 1'b1 | 1'b0 | io=data[3] | O | 1'b1 | 1'b0 | ||

| 23 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[3]=io | I | ||

| 24 | 1'b1 | 1'b0 | io=data[4] | O | 1'b1 | 1'b0 | ||

| 25 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[4]=io | I | ||

| 26 | 1'b1 | 1'b0 | io=data[5] | O | 1'b1 | 1'b0 | ||

| 27 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[5]=io | I | ||

| 28 | 1'b1 | 1'b0 | io=data[6] | O | 1'b1 | 1'b0 | ||

| 29 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[6]=io | I | ||

| 30 | 1'b1 | 1'b0 | io=data[7] | O | 1'b1 | 1'b0 | ||

| 31 | 1'b1 | 1'b1 | 1'b1 | 1'b1 | data[7]=io | I | ||

| 32 | 1'b1 | 1'b1 | ||||||

| 33 | 1'b0 | 1'b0 | ||||||

DS1302_IO使用三态门做输入输出设置

assign DS1302_IO = (ds3202_dir)?ds3202_out:1'bz;

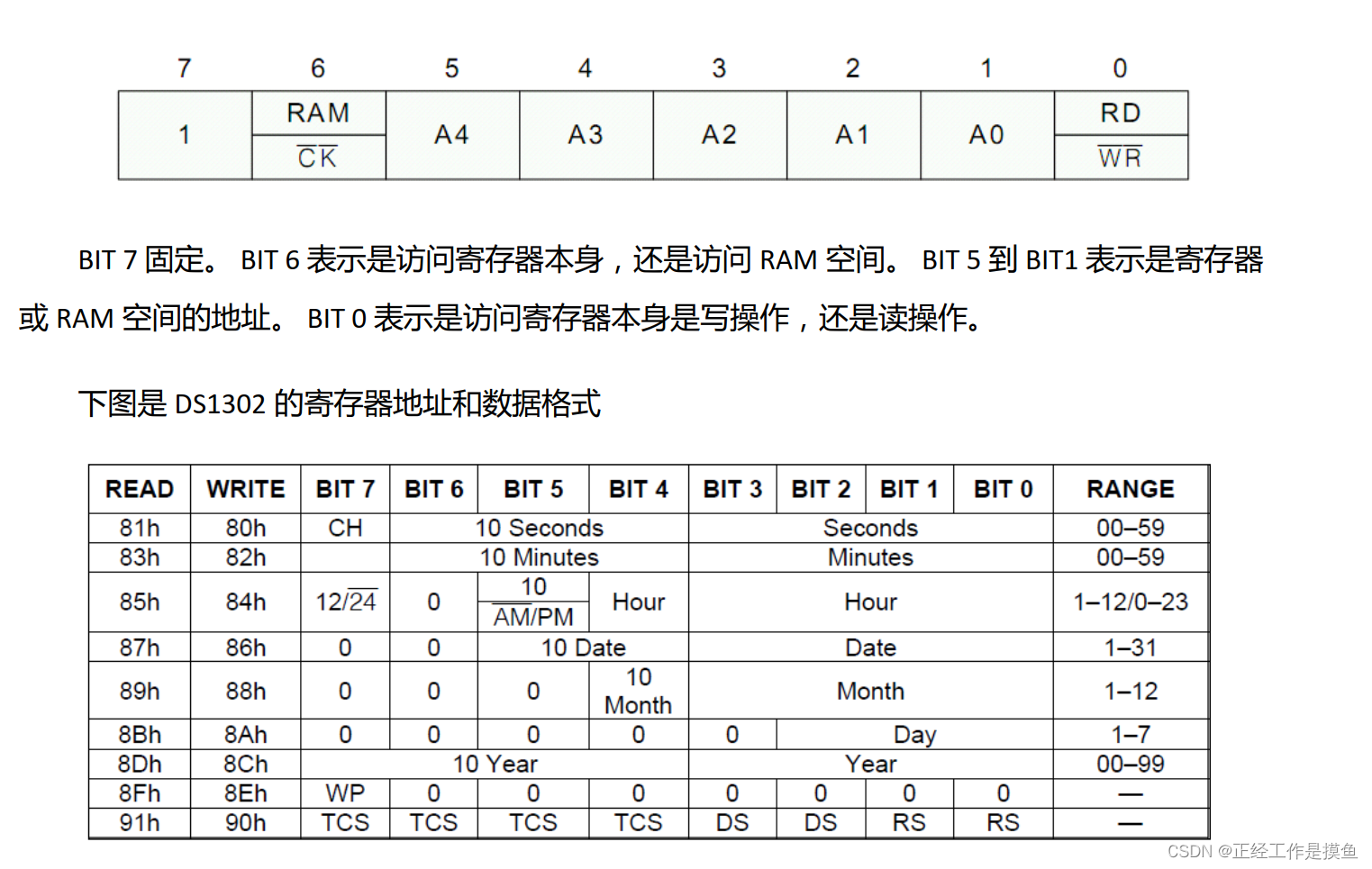

DS1302寄存器地址表格

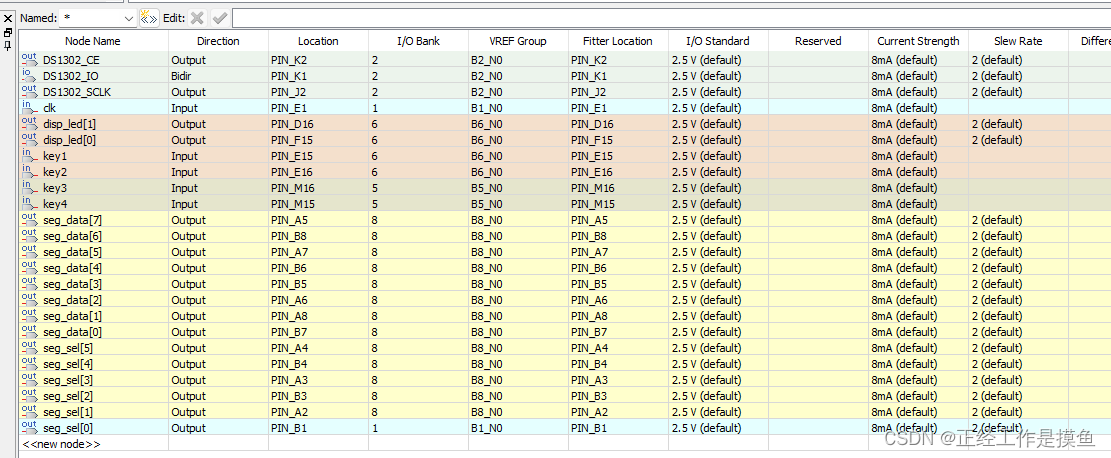

引脚绑定如下(其他版本的fpga同样可以使用,按照对应的引脚进行绑定即可)

下面是演示视频和工程文件

视频演示

资源下载

FPGA黑金开发平台学生版2014款AX301发布,虽为入门级但设计用心。该平台利用FPGA与DS1302通信实现万年历功能,通过4个按键修改数据,功能切换和仲裁采用状态机设计,与DS1302通信采取线性序列机写法,还给出引脚绑定、演示视频和工程文件。

FPGA黑金开发平台学生版2014款AX301发布,虽为入门级但设计用心。该平台利用FPGA与DS1302通信实现万年历功能,通过4个按键修改数据,功能切换和仲裁采用状态机设计,与DS1302通信采取线性序列机写法,还给出引脚绑定、演示视频和工程文件。

5010

5010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?