一、定义

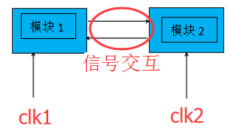

模块之间有数据交互但两个模块不是同一个时钟驱动。根据clk1与clk2是否为同步时钟,分为跨同步时钟域和跨异步时钟域。。根据信号是控制信号还是数据信号可以分为控制信号传输和数据信号的传输。

解释

同步时钟与异步时钟

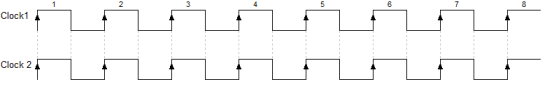

同步时钟:(1)同频同相位(2)同频不同相位,但相位固定(3)不同频,但存在整数倍的关系

异步时钟:两时钟信号完全没有关系。

二、单比特数据

1、跨同步时钟域:

(1) 同频同相:

该情况只要满足普通的同步电路设计的要求(建立和保持时间,信号的传输延时要在一定范围内)即可。一般不需要同步器。

(2) 同频不同相:

相位为固定值,允许的传输时间小于一个时钟周期。但是只要满足控制信号的输出是在clk1的控制下进行翻转的,因此只要满足同步设计的一般要求(满足建立时间和保持时间,控制信号的传输延时要在一定范围内),就可以满足时序,不会出生亚稳态,也不会出现数据丢失的情况,因此一般不需要同步器。

(3) 不同频:

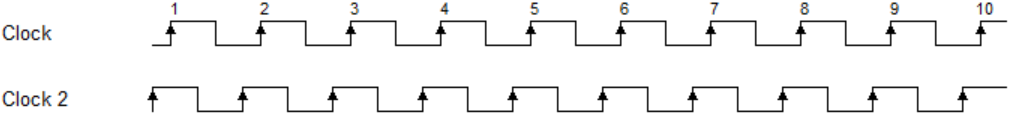

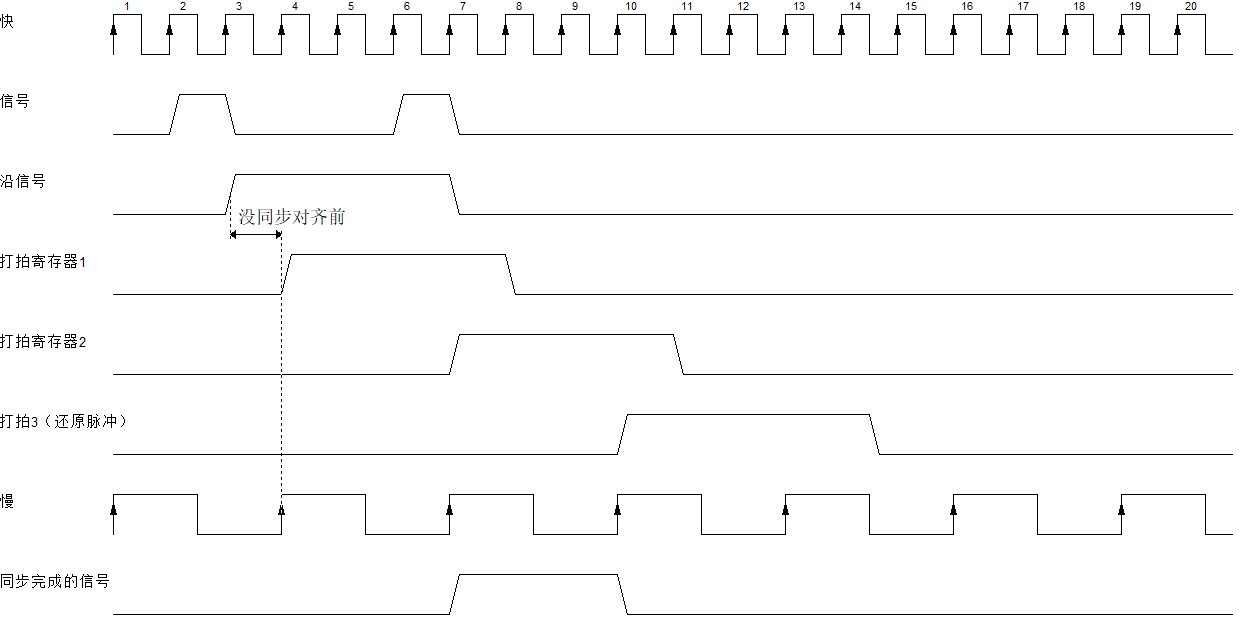

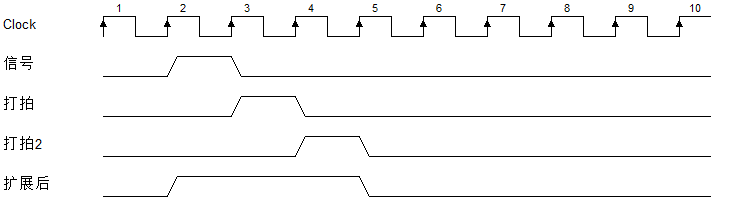

慢->快,打拍即可。快->慢,展宽后,打拍。(参考下文)

2、跨异步时钟域

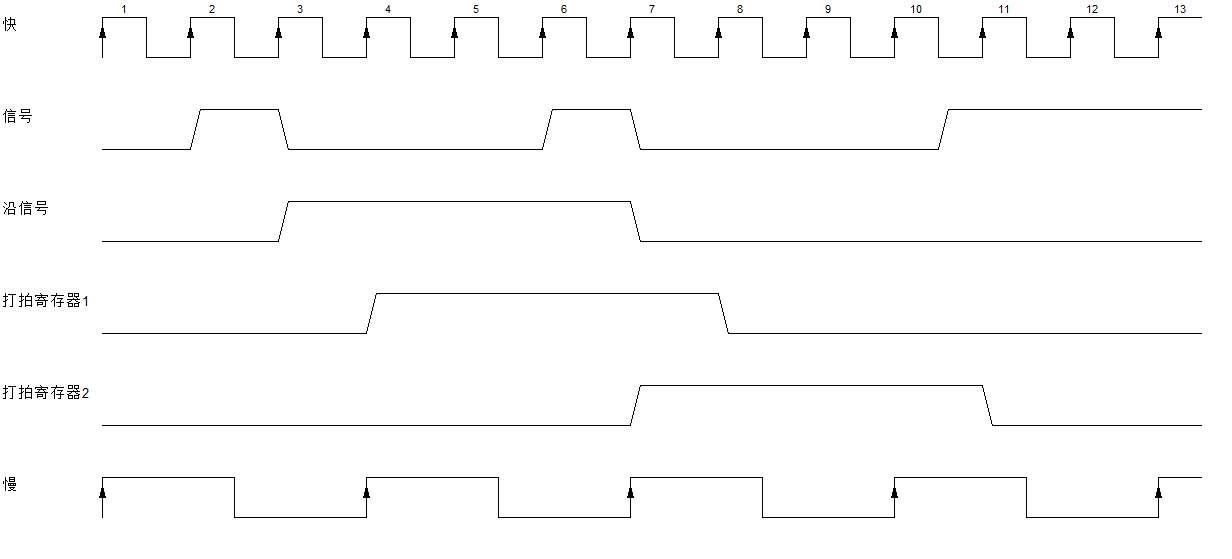

当从慢时钟域到快时钟域时,只需要打两拍防止亚稳态即可。

注:单比特信号从慢速时钟域同步到快速时钟域需要使用打两拍的方式消除亚稳态,第一级寄存器产生亚稳态并经过自身后可以稳定输出的概率为70%~80%左右,第二级寄存器可以稳定输出的概率为99%左右,再后面改善就不明显了,所以数据进来后一般选择打两拍即可。

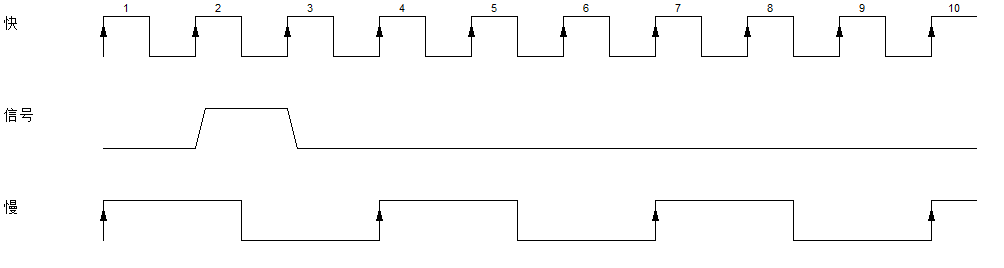

当从快时钟域到慢时钟域时,如图所示,慢时钟域可能根本就采集不到信号。

1、因此需要想办法将信号进行展宽,可以将脉冲信号转化为沿信号。当检验到信号电平为高时,就对沿信号进行取反,使得的第一个脉冲变为沿信号的上升沿,第二个脉变为沿信号的下降沿,后面如果信号还有脉冲依然是变为沿信号的上升沿和下降沿。

2、对沿信号进行打拍两次,获得稳定的信号。

3、最后,再将沿信号转化为脉冲信号。使用的方法为边沿检测。为了还原出脉冲,还需要再打一拍。

注:对于一个信号的展宽,也可以在快时钟域打拍,然后三信号相与。

三、多比特数据

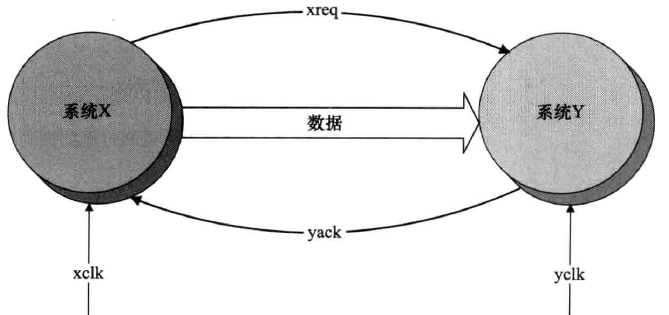

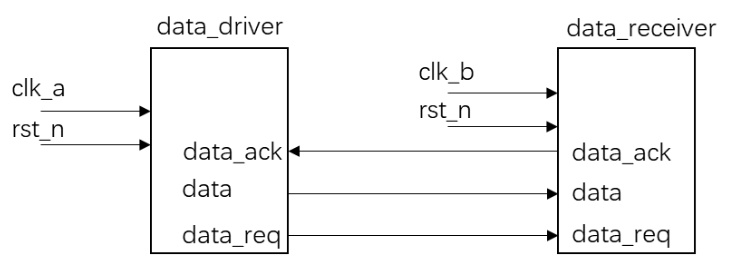

1、使用握手信号进行跨时钟域数据传输

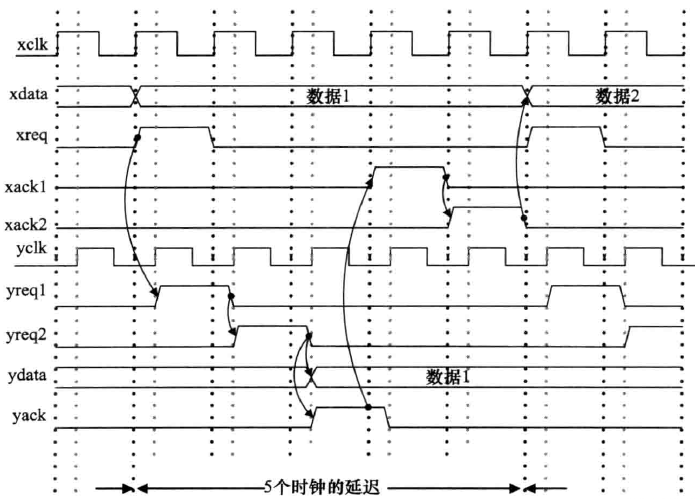

使用握手信号xack和yreq,系统X发给系统Y,下面是使用握手信号传输数据的例子:

1)发送器系统X将数据放到数据总线上并发出xreq请求信号,表示有效数据已经发送到接收器系统Y的数据总线上

2)把xreq信号同步到接收器的时钟域yclk上。

3)接收器在识别xreq同步信号yreq2后,锁存数据总线上的信号

4)接收器发出确认信号yack,表示其已经接受了数据

5)接收器发出的yack信号同步到发送时钟xclk上

6)发送器在识别同步的ack信号后,将下一个数据放到数据总线上

握手信号的时序图如下所示:

注:数据应该在发送时钟域内稳定至少两个时钟上升沿,请求信号xreq的宽度应该超过两个上升沿时钟,否则从高速时钟的低速时钟域传递可能无法捕捉到该信号。缺点是是延迟太大(相比于FIFO)。

2、FIFO

同步FIFO常用于同步时钟的数据缓存,异步FIFO常用于跨时钟域的数据信号的传递。

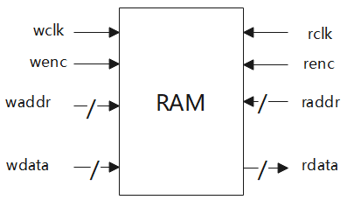

a、双端口RAM

b、FIFO地址设计

我们知道FIFO中是没有地址线的,地址靠自身计数器自加1来控制,那么我们很容易想到把外部输入信号wr_addr和rd_addr换成内部信号并用计数器来控制其自加,计数器加满之后直接清零,从0重新开始写/读,循环往复。由于写端和读端的时钟速率不同,就会有快慢的问题,那么就出现了一个问题,以地址3为例,写入的数据还没有被读出,又被新的数据覆盖了,造成数据丢失;或者写入的数据已经被读出,新的数据还没有写进来,地址3的老数据又被读了一遍,造成数据重复。

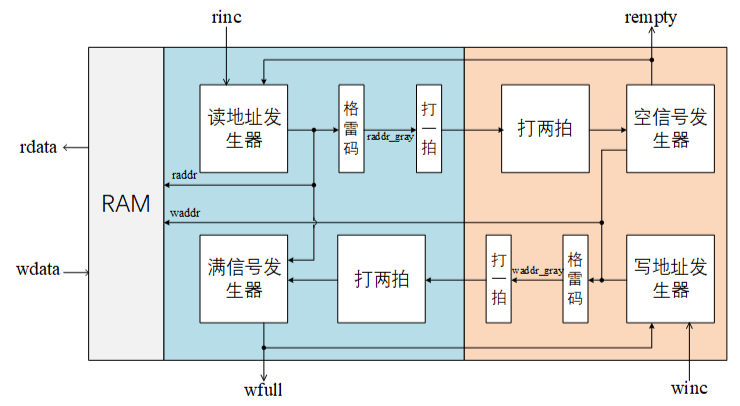

上图是本异步FIFO的结构示意图。蓝色区域是读时钟域,黄色部分是写时钟域。异步FIFO主要包含四部分:读写地址发生器、格雷码的产生与打拍、空满信号发生器以及RAM。

输入:winc, rcin, wdata

输出:rdata, wfull, rempty

读写使能:rcin\wcin,读写数据:rdata\wdata,空满信号:wfull\rempty。

当读使能rinc==1且FIFO非空rempty==0时,读地址在读时钟rclk下自增;当写使能winc==1且FIFO非满wfull==0时,写地址在写时钟wclk下自增。这两种地址可以直接传入RAM模块。

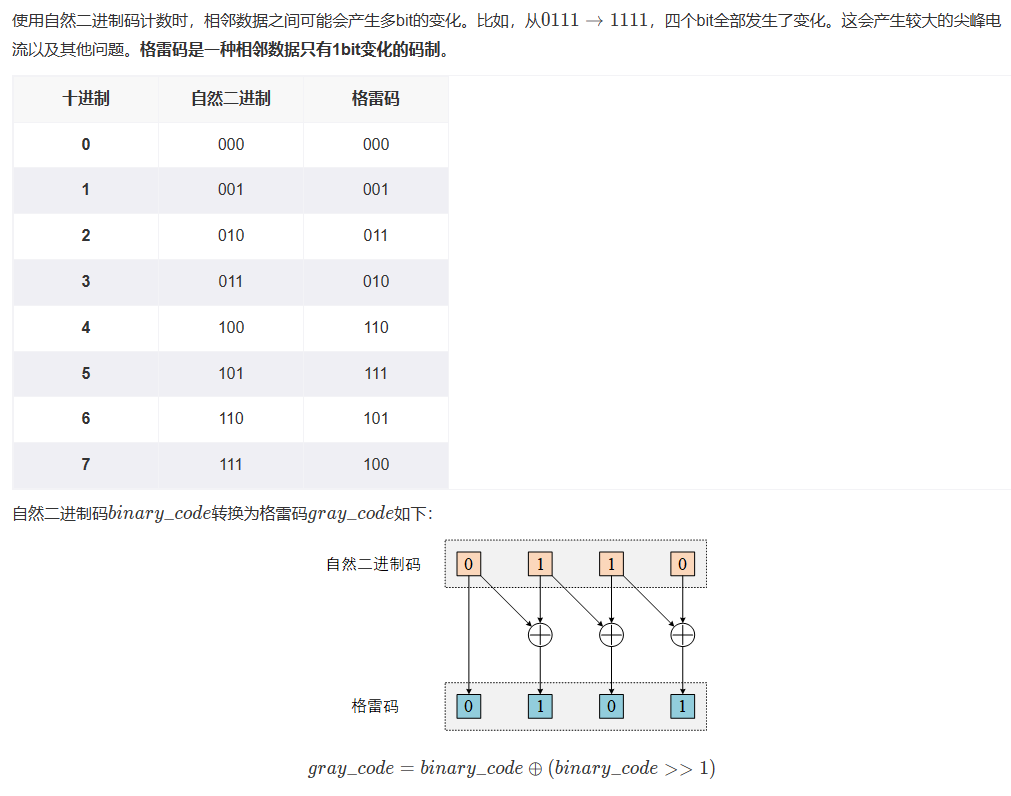

c、格雷码打拍

为了产生空满信号,需要比较读写地址的大小。但两个地址是由不同的时钟控制的,需要先做跨时钟域处理才能比较。所以使用了打两拍。又因为FIFO的读写地址是连续变化的,采用格雷码可以有效减少相邻地址的bit变化,进一步降低打拍过程产生亚稳态的可能性。

d、空满信号发生器

当读写地址的格雷码仅有最高的2bit不同时,FIFO满;当读写地址完全相同时,FIFO空。

格雷码地址比`waddr`和`raddr`多出1bit用于判断是否满。当读地址和写地址在不同圈时,格雷码的最高位也会不同。再根据格雷码的对称性,此时如果次高位不同而其他位相同,说明读写地址的自然二进制码是相通的。这体现出了格雷码的另一个优势,就是方便判断是否套圈和满信号。

参考:题解 | #异步FIFO#_牛客博客 (nowcoder.net)

文章详细阐述了跨时钟域数据传输的问题,包括同步时钟域和异步时钟域之间的差异。对于单比特数据,介绍了不同频率和相位下的处理方法,以及如何通过打拍消除亚稳态。对于多比特数据,提出了使用握手信号和FIFO(双端口RAM)作为解决方案,确保数据的正确传输。同时,文章提到了FIFO的设计,包括地址计数和空满信号的判断。

文章详细阐述了跨时钟域数据传输的问题,包括同步时钟域和异步时钟域之间的差异。对于单比特数据,介绍了不同频率和相位下的处理方法,以及如何通过打拍消除亚稳态。对于多比特数据,提出了使用握手信号和FIFO(双端口RAM)作为解决方案,确保数据的正确传输。同时,文章提到了FIFO的设计,包括地址计数和空满信号的判断。

639

639

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?