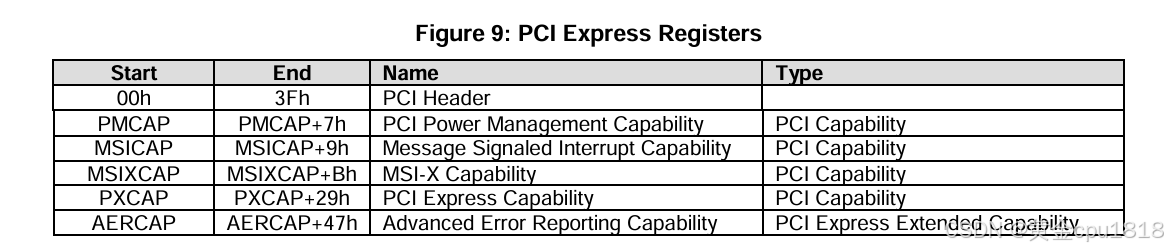

*2. System Bus (PCI Express) Registers (系统总线(PCI Express)寄存器)

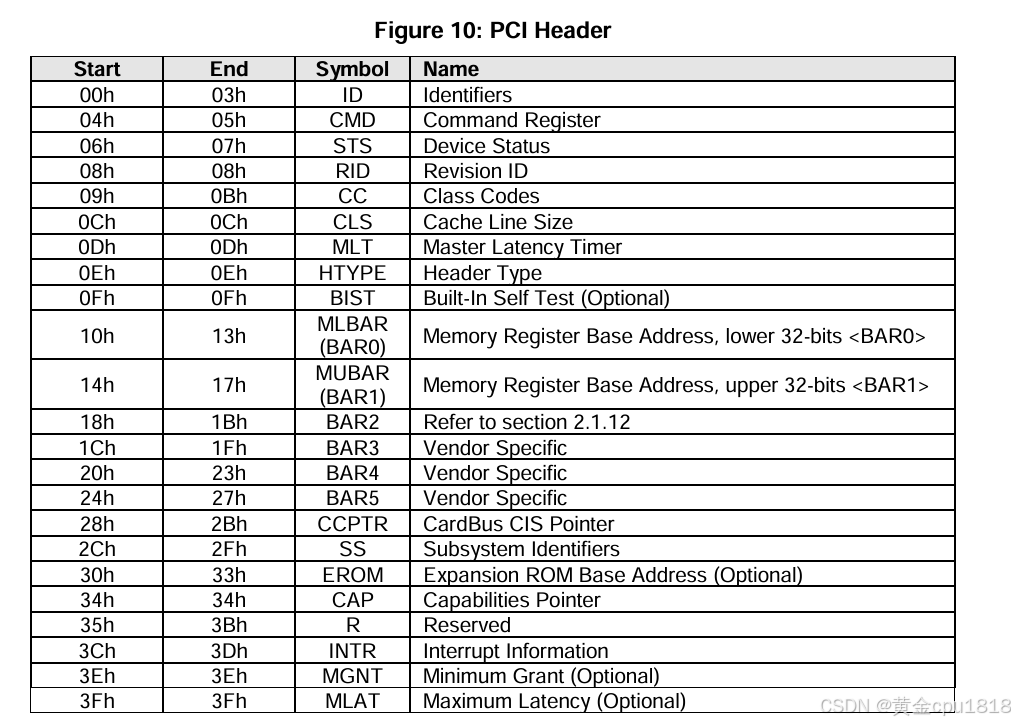

2.1 PCI Header

2.1.1 Offset 00h: ID - Identifiers

31:16 Device ID (DID): 厂商分配的设备号

15:00 Vendor ID (VID):由PCI SIG指定的公司供应商

2.1.2 Offset 04h: CMD - Command

I/O Space Enable (IOSE): 控制对控制器目标I/O空间的访问

Memory Space Enable (MSE):控制对控制器寄存器内存的访问的空间

Bus Master Enable (BME): 使能控制器充当数据传输的主机。当设置为“1”时,允许总线主活动。当清除为“0”时,控制器不允许发出任何 内存或IO请求

Parity Error Response Enable (PEE):设为“1”时,控制器生成当检测到数据奇偶校验错误,如果不支持奇偶校验,则此位为

只读‘0’。

SERR# Enable (SEE):控制错误报告

Interrupt Disable (ID):禁用控制器生成基于引脚的intx#中断。该位对MSI或MSI- x操作没有任何影响。

2.1.3 Offset 06h: STS - Device Status

Interrupt Status (IS):指示设备的中断状态 (‘1’ = 断言)

Capabilities List (CL)::指示存在功能列表。控制器应至少支持 PCI 电源管理功能

Master Data Parity Error Detected (DPD):设置为‘ 1 ’时,硬件控制器作为主机,要么检测到奇偶校验错误,要么看到奇偶校验错误线

断言,并且奇偶校验错误响应使能位(CMD.PEE)被设置为‘ 1 ’。

RTA (Received Target Abort):当控制器接收到它生成的一个周期的目标Abort时,由硬件设置为“1”。

Received Master-Abort (RMA):当控制器收到主中止到其生成的周期时,由硬件设置为“1”。

检测到奇偶校验错误 (DPE):当控制器在其接口上检测到奇偶校验错误时,由硬件设置为“1”。

2.1.4 Offset 08h: RID - Revision ID

Revision ID (RID):表示控制器硬件的步进。

2.1.5 Offset 09h: CC - Class Code

PI (Programming Interface):该字段指定控制器使用NVM Express编程接口。I/O控制器应报告02h和管理控制器应报告由PCI代码和ID分 配规范定义的03h。

子类代码 (SCC):将子类代码指示为非易失性存储器控制器。

基类代码 (BCC):将基类代码指示为大容量存储控制器

2.1.6 Offset 0Ch: CLS – Cache Line Size

Cache Line Size (CLS): 缓存行大小寄存器由系统固件或操作系统设置为系统缓存大小

2.1.7 Offset 0Dh: MLT – Master Latency Timer

Master Latency Timer (MLT):表示允许 controller 在 PCI 上充当 master 的 clocks 数。对于 PCI Express 器件,此寄存器不适用,应硬连线为 ‘0’。

2.1.8 Offset 0Eh: HTYPE – Header Type

Header Layout (HL):指示控制器使用目标设备布局

Multi-Function Device (MFD):显示该控制器是否属于多功能控制器设备

2.1.9 Offset 0Fh: BIST – Built-In Self Test (Optional)

以下 register 是可选的,但如果实现,则应如下所示。未实现时,应为只读 0h。

Completion Code (CC): 完成代码 (CC):指示 BIST 的完成代码状态。非零值表示失败

Start BIST (SB):主机软件将此位设置为“1”以调用 BIST。当 BIST 完成时,控制器将此位清零为 ‘0’

支持 BIST (BC):指示控制器是否具有 BIST 功能

2.1.10 Offset 10h: MLBAR (BAR0) – Memory Register Base Address, lower 32-bits

Resource Type Indicator (RTE):指示对寄存器内存空间的请求

Type (TP):指示可以映射此范围的位置。建议支持 64 位地址空间中任意位置的映射

Prefetchable (PF):表示此范围不可预取

Base Address (BA):寄存器内存空间的基址。对于支持大量 doorbell registers或在 doorbell registers之后具有供应商特定空间 controller, 允许更多的 bits 是 RO,从而消耗更多的内存空间。

2.1.11 Offset 14h: MUBAR (BAR1) – Memory Register Base Address, upper 32-bits

Base Address (BA):内存寄存器基址的 32 位高部 (位 63:32)。

2.1.12 Offset 18h: BAR2 – Index/Data Pair Register Base Address or Vendor Specific (Optional)

资源类型指示器 (RTE):表示对寄存器 I/O 空间的请求。

基址 (BA):索引/数据对寄存器的基址,大小为 8 字节

2.1.17 Offset 2Ch: SS - Subsystem Identifiers

子系统供应商 ID (SSVID):表示子系统供应商标识符

子系统 ID (SSID):表示子系统标识符

2.1.18 Offset 30h: EROM – Expansion ROM (Optional)

如果 register 未实现,则为只读 0h。

ROM Base Address (RBA):表示控制器扩展 ROM 的基址。不支持集成实施

2.1.19 Offset 34h: CAP – Capabilities Pointer

功能指针 (CP):指示第一个功能指针偏移量

2.1.20 Offset 3Ch: INTR - Interrupt Information

Interrupt Line (ILINE):主机软件写入的值,用于指示中断连接到哪个中断线(向量)。不会对此 register 执行任何硬件操作。

nterrupt Pin (IPIN):这表示控制器使用的中断引脚

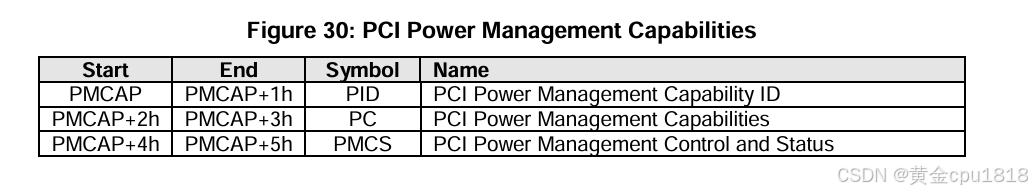

2.2 PCI Power Management Capabilities 电源管理功能

2.2.1 Offset PMCAP: PID - PCI Power Management Capability ID PCI 电源管理功能 ID

Cap ID (CID):指示此指针是 PCI 电源管理功能。

Next Capability (NEXT): 指示列表中下一个功能项的位置。这可能是功能指针(如 Message Signaled Interrupts),也可能是列表中的最后一项。

2.2.2 Offset PMCAP + 2h: PC – PCI Power Management Capabilities PCI 电源管理功能

Version (VS)::表示支持 PCI 电源管理规范的 1.2 版或更高版本

PME Clock (PMEC):指示不需要 PCI 时钟来生成 PME#

Device Specific Initialization (DSI):指示是否需要特定于设备的初始化

D1_Support (D1S):指示支持 D1 电源管理状态。不建议用于实施

D2_Support (D2S):指示支持 D2 电源管理状态。不建议用于实施

2.2.3 Offset PMCAP + 4h: PMCS – PCI Power Management Control and StatusPMCS – PCI 电源管理控制和状态

Power State (PS):此字段用于确定控制器的当前电源状态和设置新的电源状态。这些值为

00b – D0 state

01b – D1 state

10b – D2 state

11b – D3HOT state

当处于 D3HOT 状态时,控制器的配置空间可用,但寄存器 I/O 和内存空间不可用。此外,中断会被阻止

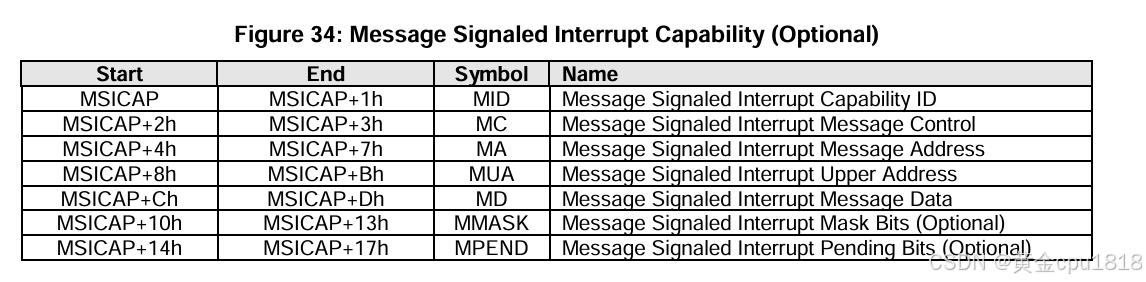

2.3 Message Signaled Interrupt Capability (Optional)消息信号中断功能(可选)

2.3.1 Offset MSICAP: MID – Message Signaled Interrupt Identifiers MID – 消息信号中断标识符

Capability ID (CID):功能 ID 指示这是消息信号中断 (MSI) 功能。

Next Pointer (NEXT):指示列表中的下一项。这可能是功能指针,也可能是列表中的最后一项

2.3.2 Offset MSICAP + 2h: MC – Message Signaled Interrupt Message Control MC – 消息信号中断消息控制

MSI Enable (MSIE):如果设置为 ‘1’,则启用 MSI。如果清除为 ‘0’,则禁用 MSI 操作。

Multiple Message Capable (MMC): 指示控制器请求的消息数。

Multiple Message Enable (MME):指示控制器应断言的消息数。仅支持单个消息 MSI 的控制器可以将此字段实现为只读。

64 Bit Address Capable (C64):指定控制器是否能够生成 64 位消息。NVM Express 控制器应支持 64 位

Per-Vector Masking Capable (PVM):指定控制器是否支持每个矢量遮罩的 MSI。

2.3.3 Offset MSICAP + 4h: MA – Message Signaled Interrupt Message Address。 Message Signaled Interrupt 消息地址

Address (ADDR):系统指定消息地址的低 32 位,始终双字对齐。

2.3.4 Offset MSICAP + 8h: MUA – Message Signaled Interrupt Upper Address 消息信号中断上限地址

Upper Address (UADDR):系统指定的消息地址的高 32 位。当控制器支持 MSI 功能时,需要此寄存器

2.3.5 Offset MSICAP + Ch: MD – Message Signaled Interrupt Message Data

Data (DATA):如果启用了 MSI,则此 16 位字段由系统软件编程。在 MSI 内存写入事务的数据阶段,它的内容被驱动到较低的字 (PCI AD[15:0])

2.3.6 Offset MSICAP + 10h: MMASK – Message Signaled Interrupt Mask Bits (Optional) 消息信号中断掩码位(可选)

Mask Bits (MASK): 对于每个设置为 ‘1’ 的 Mask 位,禁止该函数发送关联的消息。

2.3.7 Offset MSICAP + 14h: MPEND – Message Signaled Interrupt Pending Bits (Optional)

Pending Bits (PEND): 对于每个设置为 ‘1’ 的 Pending 位,该函数都有一个 pending associated 消息。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?