目前不止一次的听到小伙伴们在说,紫光同创的PDS开发软件时序约束好难收敛,老是有违例,好难用。为什么会这样呢?这个PDS软件和之前我们使用的小器件开发软件有何区别呢?为何PDS软件要做成这样?且听我慢慢道来。

首先,我们要理解FPGA开发为何要进行时序约束。个人理解,有两点:一是让工程师清楚的知道自己verilog工程是否可以在当前的时序环境下正常运行;二是在Place&Route阶段影响LUT、FF等资源的布局与走线,因为工具会优先照顾工程的关键路径。

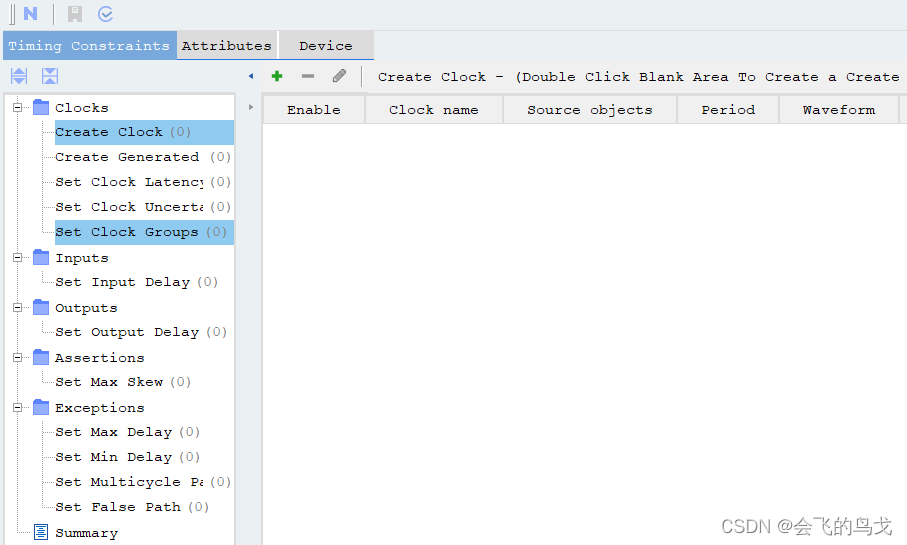

其次,FPGA设计一般要进行哪些时序约束呢,我们可以打开PDS的User Constant Edit(简称UCE)工具看一下:

上述时序约束,Create_clock用来说明程序设计中时钟的频率,一般对管脚进来的时钟进行约束,如果不约束的话,默认为1Mhz。

Create_Generated_Clock用来对衍生时钟进行约束,衍生时钟一般都是由“Create_clock”约束的时钟经过PLL或者分频之后产生的时钟。

Set_clock_latency、Set_clock_uncerty对时钟的延迟和抖动进行约束,一般情况的是不会进行约束的,这个约束意思就是告诉工具,我这个clock信号不好,抖动大还有延迟,让工具分析的时候包含这块,一起进行分析。

Set_Clock_group是对两个时钟进行异步约束,让工具完全不分

文章探讨了FPGA开发中紫光同创PDS软件的时序约束问题,解释了为何时序约束重要,包括创建时钟、衍生时钟、时钟延迟和抖动约束等。PDS与其它FPGA工具的区别在于异步时钟处理,需要用户手动约束。文章提到了时序分析的关键路径和违例处理,以及如何分析和解决P&R阶段的时序违例。建议了解基础概念并参考官方教程进行优化。

文章探讨了FPGA开发中紫光同创PDS软件的时序约束问题,解释了为何时序约束重要,包括创建时钟、衍生时钟、时钟延迟和抖动约束等。PDS与其它FPGA工具的区别在于异步时钟处理,需要用户手动约束。文章提到了时序分析的关键路径和违例处理,以及如何分析和解决P&R阶段的时序违例。建议了解基础概念并参考官方教程进行优化。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

448

448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?