74LV165与74HC595 使用

简介:

74LV165 应用于并行输入,串行输出的 场景;

74HC595应用于串行输入,并行输出的场景。

本文主要记录74lv165的使用,74HC595资料比较多,不做介绍。74HC595中文资料

74LV165说明:

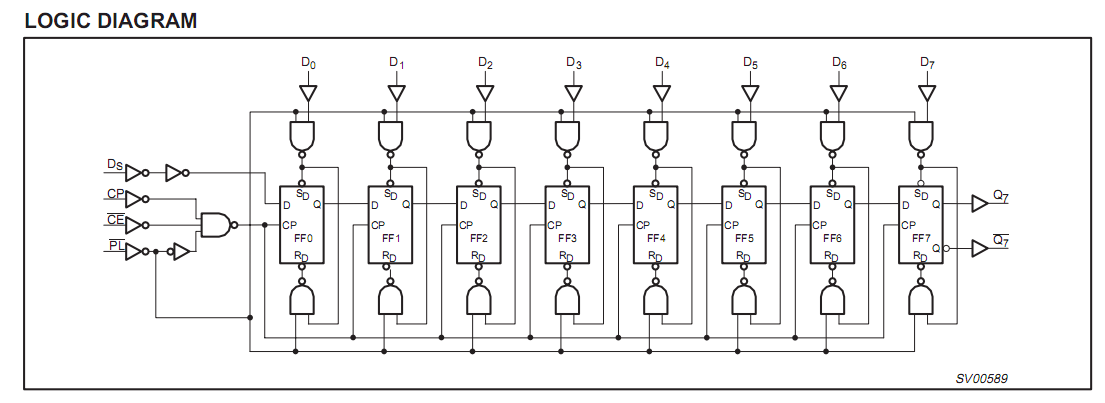

74LV165是8位并行负载或串行输入移位寄存器,末级提供互补串行输出(Q7和Q7)。并行负载(PL)输入为低电平时,来自D0至D7输入的并行数据会异步加载到寄存器中。输入PL为高电平时,数据在输入DS处串行输入寄存器。其随每次时钟正向跃迁向右移一位(Q0 → Q1 → Q2,以此类推)。通过将Q7输出连接到后一级的DS输入,该特性可实现并行到串行转换器扩展。

时钟输入为门控或结构,允许一个输入用作低电平有效时钟使能输入(CE)输入。CP和CE输入的针脚分配是任意的,为方便布局可颠倒。CE输入从低电平至高电平的跃迁应当仅在CP为高电平时发生,以便操作可预测。PL从低电平跃迁到高电平前CP或CE应当为高电平,以防激活PL时移位数据。

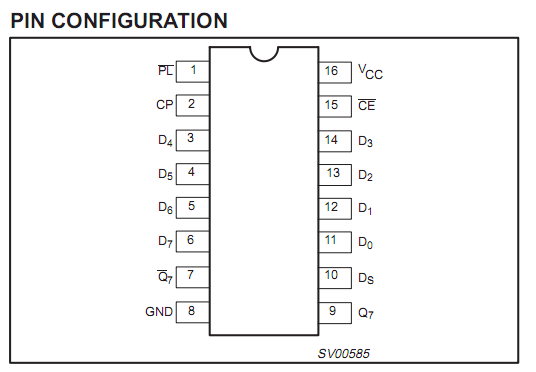

引脚图:

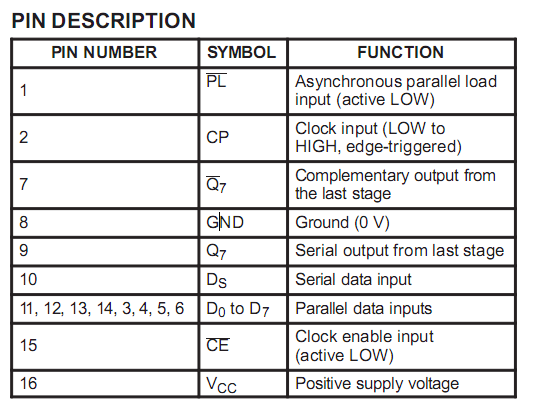

引脚说明:

逻辑框图:

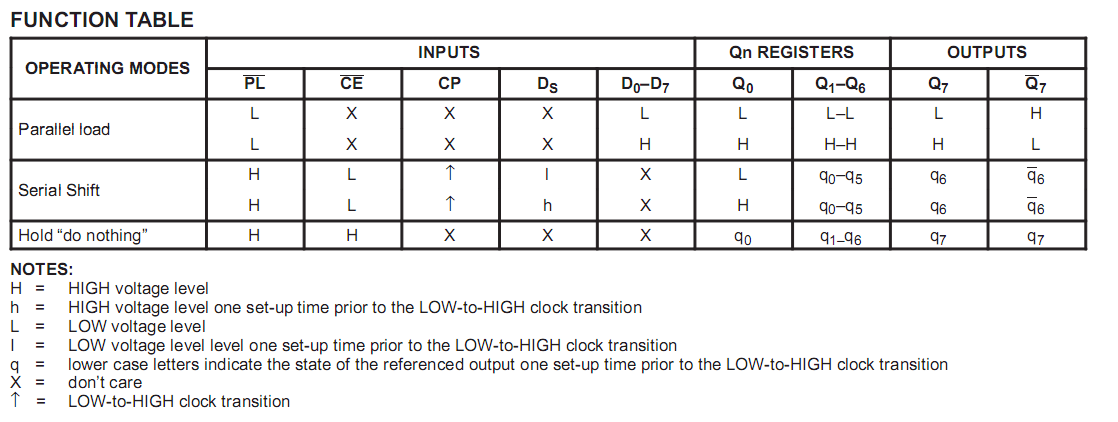

逻辑功能列表:

以上可知:

/PL 拉低,D0至D7输入的并行数据会异步加载到寄存器中;/PL 拉高,则Ds可以按CP上升沿串行输入数据至寄存器,同时寄存器中的8位数据通过7个CP上升沿从Q7输出。

当单片使用时,Ds一般不输入任何数据,用户通过/PL 拉低,加载D0-D7数据至寄存器(并行)。/PL 拉高,通过7个CP上升沿,从Q7获得8个数据。

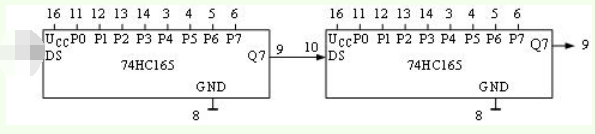

当多片级联(N)使用时,Ds连接上一片74LV165的Q7,作为Ds的输入数据,用户通过/PL 拉低,加载D0-D7数据至寄存器(并行)。/PL 拉高,通过 8 * N 个CP上升沿,从Q7获得8*N个数据。

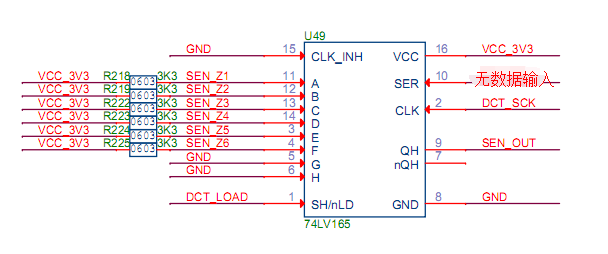

单片 原理图:

两片 级联原理图:

STM32 驱动 74lv165 代码

/*

读数据

*/

u8 OC_Read_Byte(void)

{

u8 n=0;

u8 ocdata=0;

SEL1_L;

delay(10);

ocdata |= GPIO_ReadInputDataBit(GPIOB,SPI_SDO)<<7;

for(n=0;n<7;n++) //7个 时钟沿

{

SCL_L;

delay(10);

SCL_H;

ocdata |= GPIO_ReadInputDataBit(GPIOB,SPI_SDO)<<(6-n);

delay(10);

}

SEL1_H;

return ocdata;

}以上,,,,

1963

1963

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?