DDS 信号发生器

DDS 是直接数字式频率合成器( Direct Digital Synthesizer)的英文缩写,是一项关键

的数字化技术。与传统的频率合成器相比, DDS 具有低成本、低功耗、高分辨率和快速转

换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

作为设计人员,我们习惯称它为信号发生器,一般用它产生正弦、锯齿、方波等不同波形

或不同频率的信号波形,在电子设计和测试中得到广泛应用。

基本结构

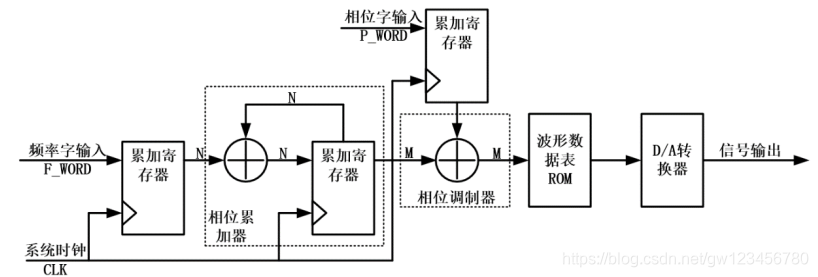

了解dds,下面的dds基本的结构需要了解清楚。

DDS,无非就是输出一个波形,而这个波形携带一些参数就是频率和相位。

输出波形,首先就需要如何产生波形,如下图的波形数据表ROM就是储存波形的数据,在FPGA中可以调用ROM的IP核,用mif文件来记录波形的数据加载到ROM中即可。mif文件可以用matlab来产生。

波形有了,那么就是如何改变波形的频率以及相位,这个其实也很简单,假设我们产生出的波形有4096个采样点,每个波形输出4096个点,这是固定的,所以改变频率不就是一个点我们多读或者少读几次不就达到波形周期的变化,这也就改变了频率。相位改变就比较简单,就是从第几个采样点开始输出波形。

下面DDS最核心的地方就是***相位累加器***,N取的是32位,频率字K每来一个时钟就与累加器的初值累加一次。这个作用就是用来改变频率,主要通过低20位[19:0]的溢出来控制高12位[31:20]的数据变化。

***相位调制器***就是截取从相位累加器值的高12位来对ROM表的寻址。假设ROM表中存储4096个点,那么地址位宽就是12位的,所以M的位宽就是12位的。

相位字P就是控制ROM表中的0~4095个采样点是从哪个开始。

K = 2^N * fOUT / fCLK

上面的公式就是频率计算公式。

- 系统时钟 CLK 为整个系统的工作时钟,频率为 fCLK;

- 频率字输入 F_WORD,一般为整数,数值大小控制输出信号的频率大小,数值越大输出信号频率越高,反之,输出信号频率越低,后文中用 K 表示;

- 相位字输入P_WORD,为整数,数值大小控制输出信号的相位偏移,主要用于相位的信号调制,后文用 P 表示;

- 设输出信号为CLK_OUT

DDS(直接数字式频率合成器)是一种数字化技术,以其低成本、低功耗、高分辨率和快速转换时间等特点广泛应用于电信和电子仪器。核心组件包括相位累加器和相位调制器,用于生成不同频率和相位的信号。MATLAB可用于生成MIF文件,该文件包含波形数据,用于在FPGA中构建波形存储。频率计算公式为K=2^N*fOUT/fCLK,MATLAB代码可生成正弦波形的MIF文件,用于DDS信号发生器的波形数据存储。

DDS(直接数字式频率合成器)是一种数字化技术,以其低成本、低功耗、高分辨率和快速转换时间等特点广泛应用于电信和电子仪器。核心组件包括相位累加器和相位调制器,用于生成不同频率和相位的信号。MATLAB可用于生成MIF文件,该文件包含波形数据,用于在FPGA中构建波形存储。频率计算公式为K=2^N*fOUT/fCLK,MATLAB代码可生成正弦波形的MIF文件,用于DDS信号发生器的波形数据存储。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1495

1495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?