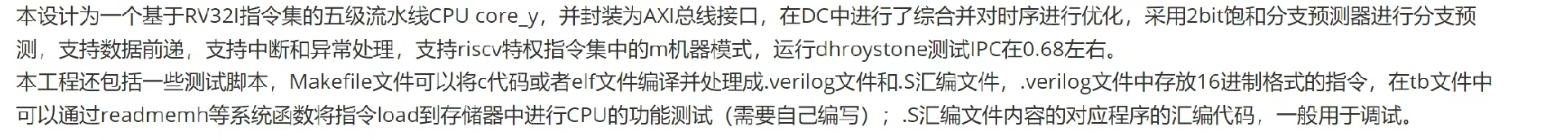

Riscv五级流水线32位cpu,systemverilog编写,指令集rv32i,支持数据前递,csr寄存器与中断控制器,可跑通dhrystone测试。

支持2bit饱和分支预测

本包括:

1.rv32五级流水线cpu代码

2.可以选择拓展的axi4总线接口代码

3.一份五级流水线cpu的详细说明文档

适合新手学习

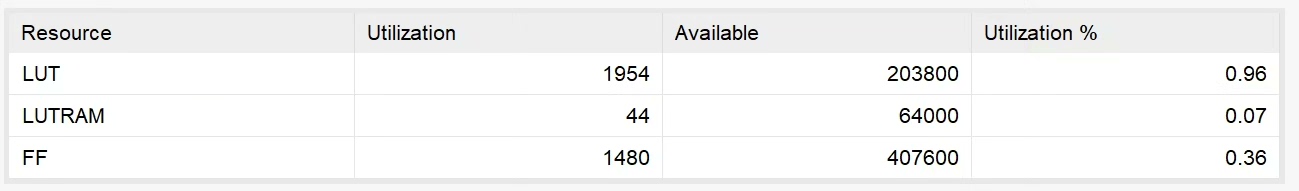

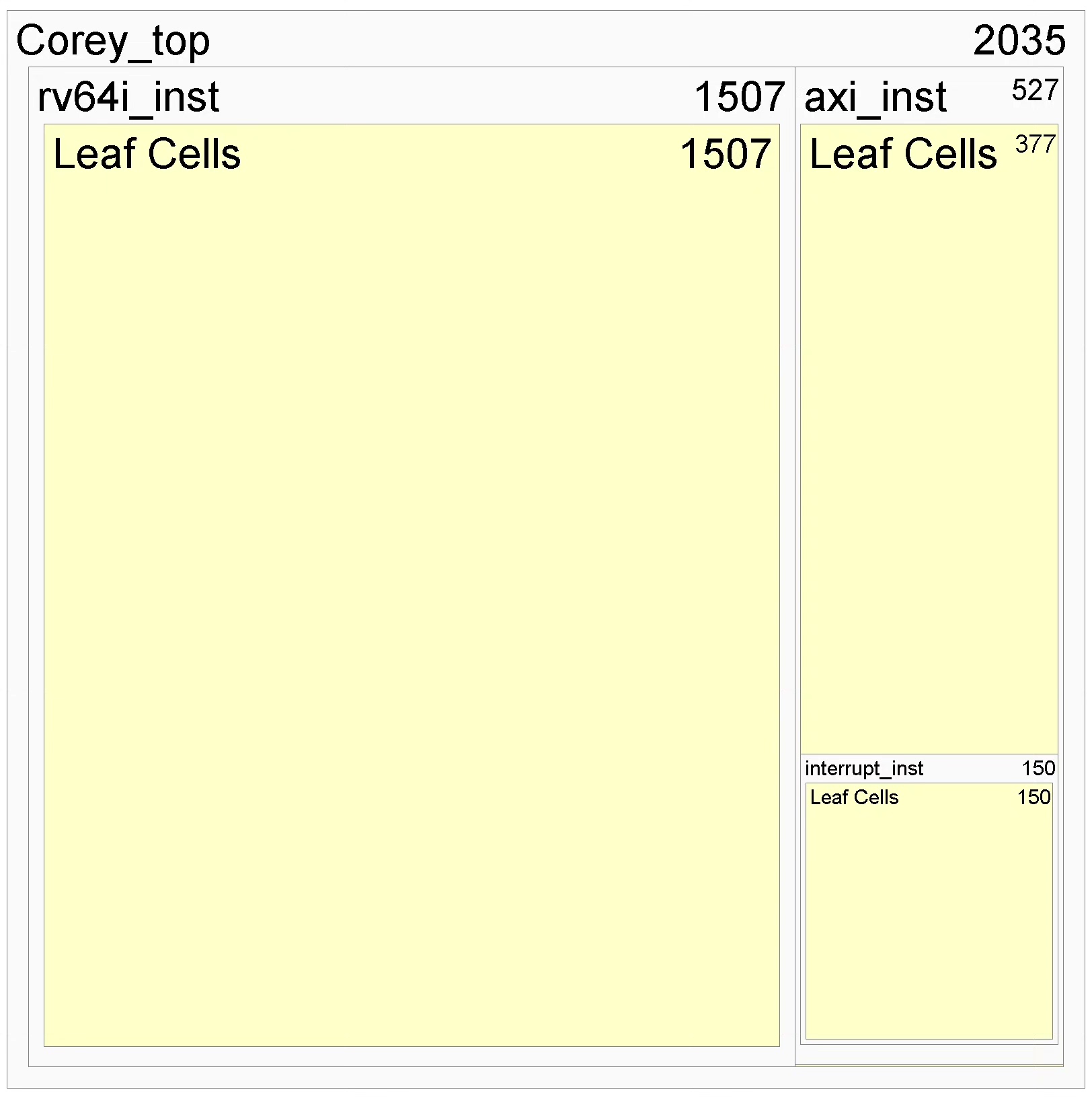

图中展示了资源消耗情况

ID:31300695744313122

云赐记

Riscv五级流水线32位cpu是一种基于RISC-V指令集的处理器架构,采用systemverilog编写,指令集为rv32i。它具备了一些先进的特性,如支持数据前递、csr寄存器与中断控制器,以及可运行dhrystone测试等。

其中,数据前递是一种常见的解决数据冒险(data hazard)的方法。在数据依赖关系导致的冒险情况下,数据前递可以将结果直接传递给需要使用该结果的指令,无需等待结果写回到寄存器,从而提高了处理器的性能。

另外,csr寄存器(Control and Status Register)和中断控制器是RISC-V体系结构中的重要组成部分。csr寄存器用于存储控制和状态信息,如异常处理、中断控制等。中断控制器则负责处理外部中断信号,并进行相应的处理。

此外,该Riscv五级流水线32位cpu还支持了2bit饱和分支预测。分支预测是一种在流水线处理器中提高分支指令执行效率的技术。通过预测分支指令的执行方向,可以在预测正确时减少流水线停顿,从而提高处理器的性能。

该Riscv五级流水线32位cpu还附带了一些相关的代码和文档。其中,五级流水线cpu代码是该处理器的核心代码,详细说明了处理器的各个阶段和功能实现。此外,还提供了可选择拓展的axi4总线接口代码,以便与其他外部设备进行通信。最后,还有一份五级流水线cpu的详细说明文档,适合新手学习。这份文档详细解释了各个阶段的实现原理和功能,帮助读者更好地理解该处理器的工作原理和使用方法。

下图展示了该Riscv五级流水线32位cpu的资源消耗情况。从图中可以看出,该处理器在实现和运行过程中所需的资源相对较少,适合于在嵌入式系统等资源受限的环境中使用。

综上所述,Riscv五级流水线32位cpu是一款采用RISC-V指令集的处理器架构,具备了一些先进的特性,如数据前递、csr寄存器与中断控制器等。它还支持2bit饱和分支预测,并附带了相应的代码和文档,适合新手学习。该处理器的资源消耗相对较低,非常适合运行在资源受限的环境中。通过学习和使用该处理器,开发者可以更深入地了解并应用RISC-V架构的相关知识。

希望以上内容对您有所帮助,谢谢阅读。

相关的代码,程序地址如下:http://nodep.cn/695744313122.html

1199

1199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?