Riscv五级流水线32位cpu,systemverilog编写,指令集rv32i,支持数据前递,csr寄存器与中断控制器,可跑通dhrystone测试。

支持2bit饱和分支预测

本包括:

1.rv32五级流水线cpu代码

2.可以选择拓展的axi4总线接口代码

3.一份五级流水线cpu的详细说明文档

适合新手学习

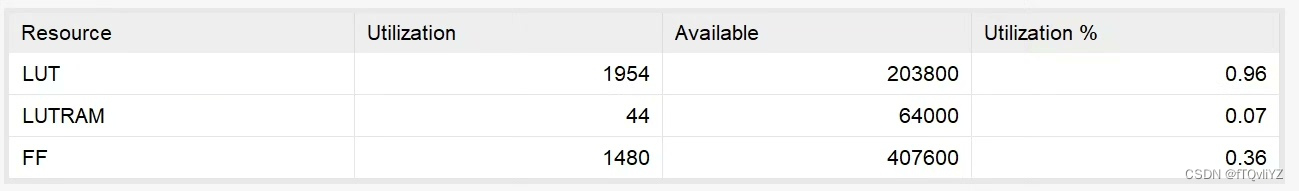

图中展示了资源消耗情况

Riscv五级流水线32位CPU:支持数据前递、csr寄存器与中断控制器,可跑通dhrystone测试

Riscv是近年来备受关注的开源指令集架构,它具有简洁、清晰的设计、极高的灵活性和可扩展性,已成为开源处理器设计的新生代标准之一。本文将重点介绍Riscv五级流水线32位CPU,该CPU的指令集为rv32i,支持数据前递、csr寄存器与中断控制器,并可成功跑通dhrystone测试。

五级流水线是一种比较经典的指令流水线设计,在本CPU中也得到了很好的应用。五级流水线包括取指(IF)、译码(ID)、执行(EX)、访存(MEM)和写回(WB)五个阶段,每个阶段都有其特定的功能。

在取指阶段,CPU从存储器中获取即将要执行的指令,然后转化成可以供下一步骤使用的格式。一般情况下,CPU可以通过分支预测来提高CPU效率,而这里的CPU支持了2bit饱和分支预测,更进一步地提高了CPU运行效率。

在译码阶段,CPU将刚才取到的指令进行分析,并识别出要使用的寄存器等操作数。在执行阶段,通过算术逻辑单元(ALU)进行指令的运算操作。在访存阶段,CPU将数据进行存储或读取操作,同时也负责处理中断请求。在写回阶段,CPU将执行得到的结果写回到寄存器中。

本CPU还支持数据前递,这是一种比较常见的技术,在CPU的结果还没有被写回到寄存器中时,可以直接从执行阶段将其结果传递到下一阶段使用,提高了CPU的效率。此外,CPU也集成了csr寄存器与中断控制器,可以对CPU的状态进行方便地控制与管理。

本CPU的设计使用SystemVerilog完成,这是一种常用的硬件描述语言,其拥有的高级语言特性可以很方便地实现各种硬件逻辑设计,并且还可以方便地进行模拟、仿真以及调试。同时,CPU也提供了选择拓展的Axi4总线接口代码,使得CPU可以方便地进行与其他硬件模块的连接。

针对本CPU的设计,我们还提供了一份详细的说明文档,这样即使是新手也可以方便地进行学习和调试。如图所示,我们也展示了本CPU的资源消耗情况,可以看出其所需资源总体较少,性能方面也十分优秀,可以满足各种需求。

总之,Riscv五级流水线32位CPU是一种经典的指令流水线设计,支持数据前递、csr寄存器与中断控制器,可以成功跑通dhrystone测试。同时,我们还提供了说明文档以及拓展的Axi4总线接口代码,方便各种硬件模块的连接。对于初学者来说,本CPU也是一个很好的学习对象。

相关代码,程序地址:http://lanzouw.top/695744313122.html

269

269

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?