原文截取自PPC750CL,IBM技术文档。

PowerPC 750 实现了分开的指令Cache和数据Cache。每个Cache打开是32KB,8路组相连。根据PowerPC的体系结构定义,他们是被物理索引的。每个Cache块包含了8字对齐的内存内容。因此,一个Cache块永远也不会跨越一个页面边界。对于一个非对齐的访问(也就是跨越了页边界)可能会导致性能下降。Cache是非阻塞的回写cache,在cache产生miss的时候由硬件支持进行重载。

The critical double word is transferred on the first beat and is simultaneously written to the

cache and forwarded to the requesting unit, minimizing stalls due to load delays. The cache being loaded is not blocked to internal accesses while the load completes.

临界双字在第一拍被传输和同时写入到缓存,并转发给请求单元,使load delays带来的延迟最小化。加载缓存对于内部存取来说是非阻塞的(这句话没看懂)。

在一个CPU工作周期内,数据缓存可以给LSU提供2字的存取。和指令Cache(I-Cache)一样,数据Cache(D-Cache)可以做全局无效化或者以cache块为单位进行无效化操作。D-Cache可以通过清零HID0[DCE]位被禁能,同时通过设置HID0[DCFI]位进行无效化。D-Cache可以通过设置HID0[DLOCK]位来进行锁定。为了保证Cache一致性,D-Cache遵循三状态MEI协议。D-Cache的tags是单端口的,所以同时进行load和store操作和一个探测存取(snoop access)资源会发生冲突。

If a snoop hit occurs, the LSU is blocked internally for one cycle to allow theeight-word block of data to be copied to the write-back buffer

如果一个snoop hit发生了,LSU会阻塞一个周期来让8字的块的数据被复制到回写缓冲里。

在每一个CPU周期内,I-cache可以提供多达4条指令到指令队列内。I-Cache可以被一次性全局无效化或者以cache块为单位进行无效化。I-Cache可以通过清零HID0[ICE]位被禁能,同时通过设置HID0[ICFI]位进行无效化。I-Cache可以通过设置HID0[ILOCK]位来进行锁定。指令Cache只支持valid和invalid状态,也即他没有D-cache的modified以及exclusive状态。

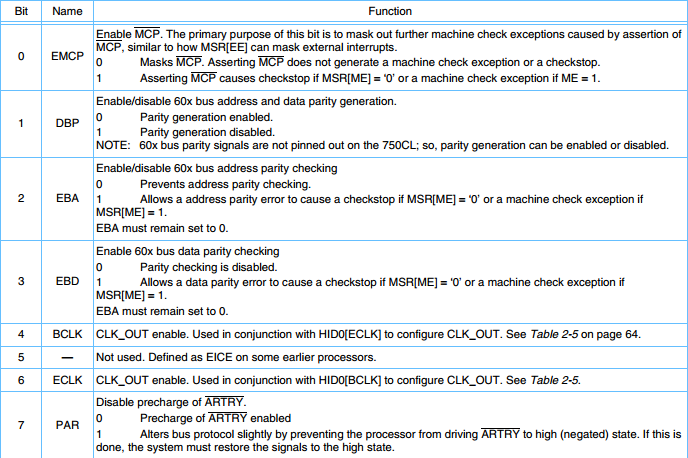

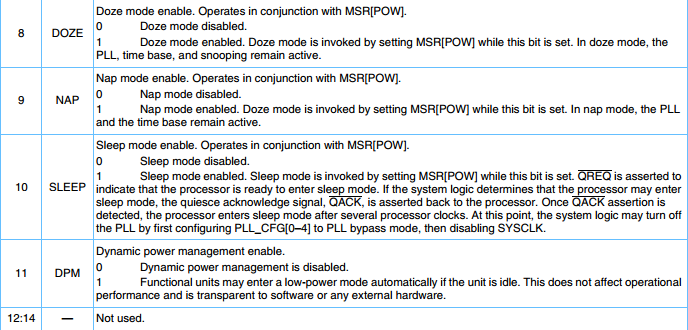

硬件实现相关处理器0(hardware implementation-dependent register 0 (HID0) )是一个跟硬件相关的寄存器(750系列应该是有4个),控制了许多的功能状态,其中就包括cache的使能等。他的具体各位情况如果上图 Figure 2-3.所示。

各个位的含义如下表所示:

其中和cache相关的几位如下:

16:ICE instructioncache enable

为0时禁能ICache(instructioncache,指令缓存)。为1时使能ICache。

当为0时,Icache既不能读取也不能更新。所有的页都视作他们的存取被标记为cache-inhibited(WIM=X1X)。潜在的从其他核的总线(bus)cache存取(snoop或者cache 操作)也被忽略。当L1 caches在禁止状态时,cache tag的状态位都被忽略,并且所有的存取都被视作单一节拍的事务传递给L2 cache或者总线。但是对于这些事务,CI(Cache Inhibit (CI)信号)反映的是地址转换决定的初始状态,是不管cache的禁止状态的。

ICE在上电的时候是0.

17:DCE data cacheenable

为0时禁能dcache(data cache,数据缓存),为1时使能dcache。

当为0时,dcache既不能读取也不能更新。所有的页都视作他们的存取被标记为cache-inhibited(WIM=X1X)。潜在的从其他核的总线(bus)cache存取(snoop或者cache 操作)也被忽略。当L1 caches在禁止状态时,cache tag的状态位都被忽略,并且所有的存取都被视作单一节拍的事务传递给L2 cache或者总线。但是对于这些事务,CI(Cache Inhibit (CI)信号)反映的是地址转换决定的初始状态,是不管cache的禁止状态的。

DCE在上电的时候是0.

18:ILOCK Instructioncache lock

为0时表示一切如常。

为1使,icache被锁定。一个锁定的cache在命中的时候会如常的提供数据,但是在未命中的时候会被视作cache-inhibited事务。在未命中时,这个事务提交给总线或者L2 cache的时候是单节拍的,但是CI(Cache Inhibit (CI)信号)反映的是地址转换决定的原始状态,是不管cache的锁定状态的。

为了阻止在cache存取的锁定操作,在设置ILOCK之前必须先有一条isync指令。

19:DLOCK Data cache lock.

为0时表示一切如常。

为1使,Dcache被锁定。一个锁定的cache在命中的时候会如常的提供数据,但是在未命中的时候会被视作cache-inhibited事务。在未命中时,这个事务提交给总线或者L2 cache的时候是单节拍的,但是CI(Cache Inhibit (CI)信号)反映的是地址转换决定的原始状态,是不管cache的锁定状态的。一次对于锁定状态的L1 data cache的snoop命中会如同没有锁定一样正常运作。一个被snoop无效化的cache块会保持在无效状态直到cache解锁。

为了阻止在cache存取的锁定操作,在设置DLOCK之前必须先有一条sync指令。

20:ICFI Instruction cache flash invalidate

为0时,指令缓存没有被无效化。这个位会在无效化操作开始的时候清零(通常是在写入寄存器操作的下一个周期),为了无效化能够发生,指令缓存必须为使能状态。(这句话有点问题,但是原话如此)

0 Theinstruction cache is not invalidated. The bit is cleared when the invalidationoperation begins (usually the

next cycle after the write operation to the register). The instruction cachemust be enabled for the invalidation to

occur.

为1时,一个无效化操作被提交并且会在不回写修改过的cache到内存的情况下标记每个指令缓存块为无效。Cache的存取在这段时间会被阻塞。总线的cache存取在这段无效所有cache操作时被视作不命中。设置ICFI清除所有的块的有效位,并且,PLRU位会指向每组的第L0路。一旦L1快速无效位被mtspr设置,硬件会自动在下一个周期复位这些位(相应的cache enable位也会在HID0中被设置)

注意:在PowerPC603和603e处理器中,ICFI和DCFI位的正确使用是要连续使用两条mtspr操作设置他们并且清零他们。运行在750cl中的软件如果有这系列操作也不需要更改。

21:DCFI Data cache flash invalidate

同上,只是针对Data cache的。

另外还有

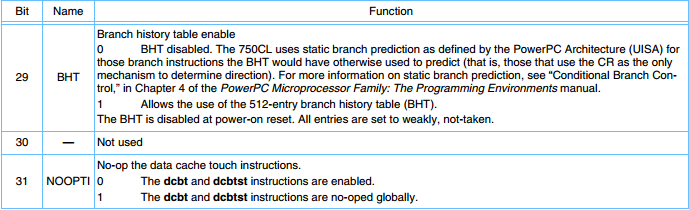

26:BTIC Branch Target Instruction Cache enable

被用来是使能64条分支指令cache的。0表示disabled,内容无效,BTIC表现为内容为空。新的条目无法被添加知道使能。

1表示使能,新条目可以被添加。

31:NOOPTI No-op the data cache touch instructions.

0 The dcbt and dcbtst instructionsare enabled.

1 The dcbt and dcbtst instructionsare no-oped globally.

6500

6500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?