Media Independent Interface

Media Independent Interface ( MII ),介质独立接口,起初是定义100M以太网(Fast Ethernet)的 MAC 层与 PHY 芯片之间的传输标准(802.3u)。介质独立的意思是指,MAC与PHY之间的通信不受具体传输介质(双绞线或光纤等)的影响,任何MAC和PHY都可以通过MII接口互连。

MAC与PHY之间的MII连接可以是可插拔的连接器,也可以是同一块PCB上MAC与PHY之间的走线。

MDIO 是MII接口的一部分,用于在MAC和PHY之间传递配置信息。在系统上电瞬间,PHY芯片通过管脚的电平状态确定原始设置,进而通过MDIO更改配置。

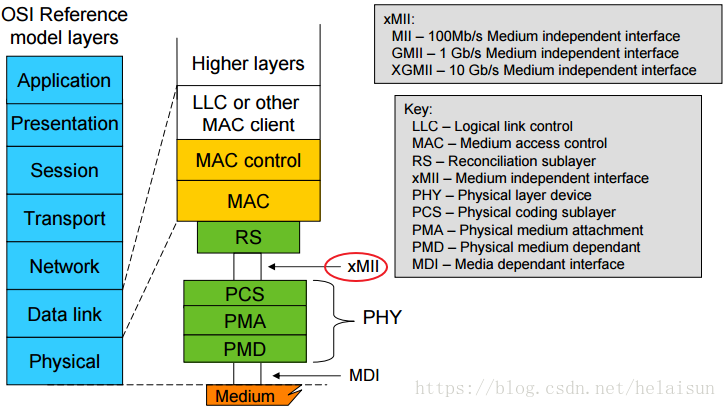

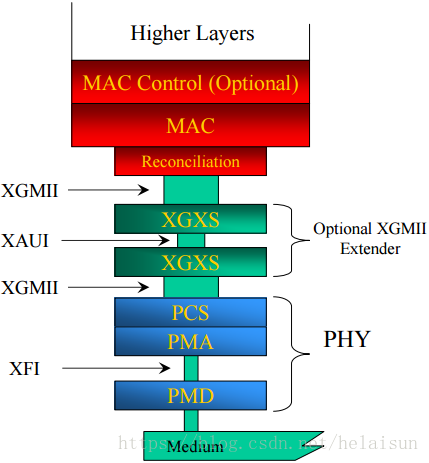

最初MII定义数据 4 bit 发送+ 4 bit 接收,每位数据速率 25MHz ,总数据速率 100Mbps 。其它 MII 标准的变种,包括 RMII,GMII,RGMII,XGMII,SGMII,基本上都是定位于更高速率或者更少的信号数的目标,图1表示在以太网通信层次模型中MII接口的位置。

图1. IEEE 802.3 标准(100Mbps +)

MII: Media Independent Interface

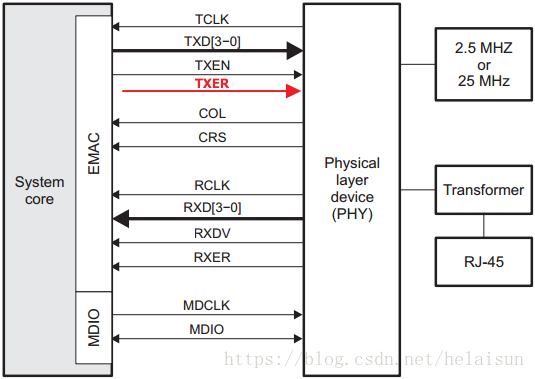

MII接口信号包括三类,分别为:

- 发送端信号:TXCLK, TXD[0-3], TXEN, TXER

- 接收端信号:RXCLK, RXD[0-3], RXDV, RXER, CRS, COL

- 配置信号:MDIO, MDC

信号方向如下图所示,其中 TXER 为选配。MII 共计 18 根信号线,只有 MDIO/MDC 信号可以在不同PHY间级联。假定系统中有 8 个PHY,则MII信号总数为 8*16 + 2 = 130 根!为减少信号数,RMII接口应运而生。

图2. MII Interface

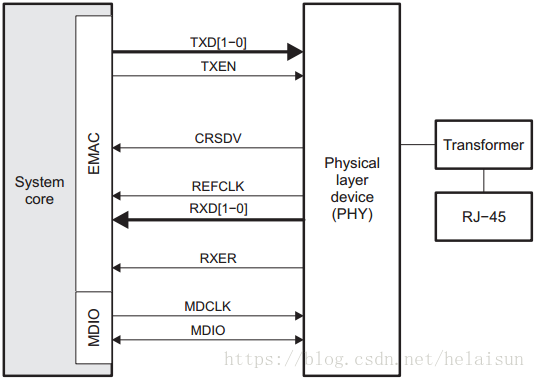

RMII: Reduced Media Independent Interface

相比于MII接口,RMII有以下四处变化:

- TXCLK 和 RXCLK 两个时钟信号,合并为一个时钟 REFCLK

- 时钟速率由 25MHz 上升到 50MHz,单向数据由 4 bits 变为 2 bits

- CRS 和 RXDV 合并为一个信号 CRSDV

- 取消了 COL 信号

RMII信号如下图所示。RMII只要 9 根信号线,相比于MII的 18 根信号可谓有不少的删减,在同一个系统中的多个设备可以共享 MDIO, MDC 和 REFCLK 信号线。

图3. RMII Interface

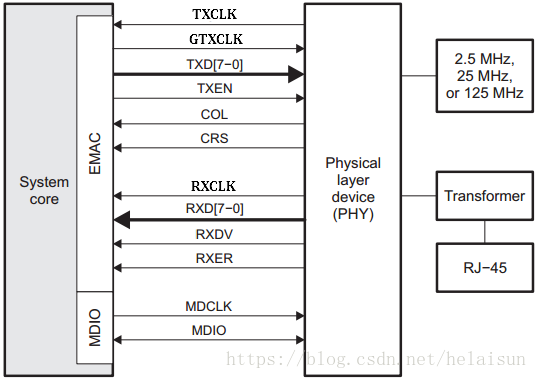

GMII: Gigabit Media Independent Interface

GMII接口的数据速率可达 1000Mbps,其时钟频率为 125MHz ,单向数据位宽 8 bits。GMII向下兼容MII,可以像MII一样工作在 100Mbps 和 10Mbps 的数据速率。

GMII接口信号包括三类,分别为:

- 发送端信号:GTXCLK, TXCLK, TXD[0-7], TXEN, TXER

- 接收端信号:RXCLK, RXD[0-7], RXDV, RXER, CRS, COL

- 配置信号:MDIO, MDC

发送端包括两个时钟信号 GTXCLK 和 TXCLK,当设备工作于 1000Mbps 模式时,TXD, TXEN, TXER 是与 GTXCLK (125MHz)同步的,而在 10/100Mbps 工作模式时,以上数据信号是同步于由PHY提供的TXCLK 的,其中 100Mbps 时是 25MHz,10Mbps 时是 2.5MHz。接收端时钟只有一个时钟信号 RXCLK,它是从接收数据中恢复的时钟。

图4. GMII Interface

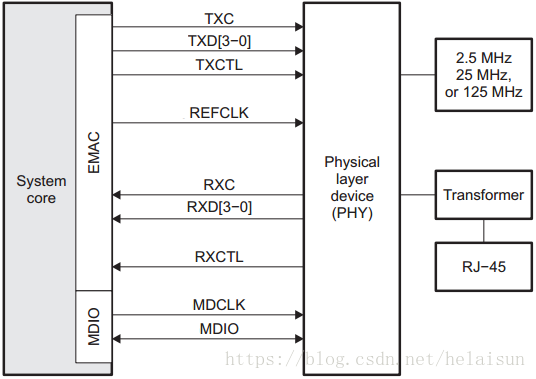

RGMII: Reduced Gigabit Media Independent Interface

RGMII相比于GMII减小将近一半的管脚数(24 → 12),通过以下两种方式:

- 1000Mbps模式下,在时钟的上/下边沿均采样数据

- 取消不重要的如 CRS, COL 等信号

在RGMII接口中 MAC 在 TXC 上一直提供时钟信号,而不像在GMII接口中那样,10/100Mbps 模式下时钟是由 PHY 提供(TXCLK),而 1000Mbps 模式下时钟是由 MAC 提供(GTXCLK)。在RGMII中应用到源同步时钟,即数据与时钟信号是同步的。这要求在PCB设计中,要对时钟信号额外增加 1.5~2 ns 的延迟以保证接收端的建立/保持时间满足要求。在 RGMII v2.0 规范中有定义MAC/PHY内部延迟(RGMII-ID),由此避免PCB设计中再要增加这个延迟。

在RGMII接口中:

- 1000Mbps 模式,数据在时钟的上/下边沿均采样

- 10/100Mbps 模式,数据仅在时钟上升沿采样

RXCTL 和 TXCLT 为复用的传输控制信号。RXCTL 在时钟的上升沿代表 RXDV,在时钟的下降沿代表(RXDV xor RXER);TXCTL 在时钟的上升沿代表 TXEN,在时钟的下降沿代表(TXEN xor TXER)。

RGMII v1.3 采用 2.5V CMOS 电平,RGMII v2 采用 1.5V HSTL 电平。

图5. RGMII Interface

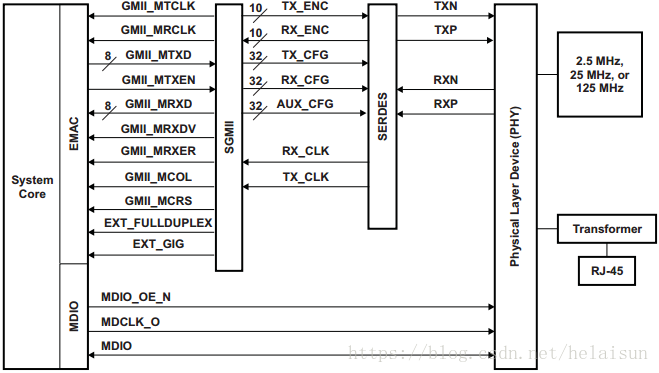

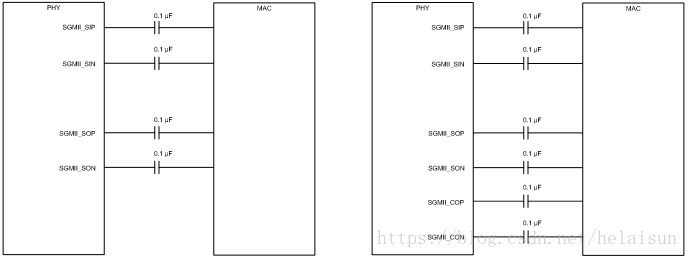

SGMII: Serial Gigabit Media Independent Interface

SGMII发送和接收时钟频率均为 625MHz,采用 DDR 模式,因此数据速率为1.25Gbps。SGMII相比于GMII,功耗更低,采用 SerDes 接口后管脚数更少。SGMII发送和接受数据各 1 对差分信号(LVDS),另外还有 1 对差分时钟,共 6 根线。对于 MAC/PHY 中包括时钟恢复电路(CDR, Clock and Data Recovery circuitry )的系统,TXCLK 可以省略,SGMII接口只需要 4 根线,相比于GMII( 24 根)和RGMII( 12 根)信号线大大减少!

TX/RX在数据发送端必须同时产生时钟,而接收端的时钟是可选的,因为可以通过 CDR 恢复时钟。在 10/100Mbps 工作模式下,数据分别重复发送 100/10 次,因此时钟always是 625MHz。

图6. SGMII Interface

图7. 4-Wire/6-Wire SGMII

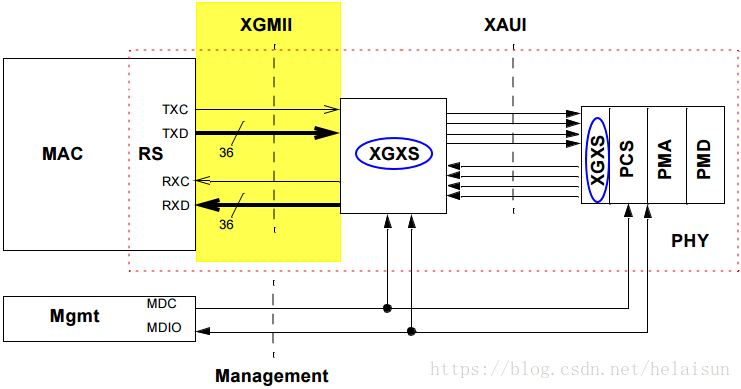

XGMII: 10 Gigabit Media Independent Interface

XGMII 是用于10G以太网的MAC与PHY设备间通信的接口标准,它包括 32 bits 的数据通道(RXD & TXD),两组 4 bits 的控制通道(RXC & TXC)和两组时钟(收/发),时钟频率 156.25 MHz ,工作在 DDR 模式。图8表示XGMII接口的连接示意图,注意 RXD/TXD 信号上的 36 表示 32 bits 数据 + 4 bits 控制信号,其中每 8 bits 数据称为 1 个Lane,共用 1 路控制信号。

- 10 Gbps = 156.25 MHz * 32 bits * 2

XGMII信号数目(74 根)较多,通常用于芯片内的连接,不适合作为芯片间通信的接口,因此协议定义XGXS(XGMII eXtender Sublayer)子层以缩减信号数目,简化硬件设计。XGXS 子层主要完成 8b/10b 编码和不同Lane之间的去偏斜等功能。如图8所示,在信号链的两端,MAC和PHY 都包括XGXS子层,XAUI 是 XGXS 之间通信的接口。

XAUI 接口包括4组发送差分对和4 组接收差分对,共 16 根信号。每组差分对(Lane)的数据速率为 3.125 Gbps,因此总的数据速率为 4 * 3.125 Gbps = 12.5 Gbps,考虑到8b/10b的效率为80%,因此实际数据速率为 12.5Gbps * 80% = 10 Gbps。

图8. XGMII Interface

XFI/XFP

XFI 是10G以太网 PMA(Physical Medium Attachment)和 PMD(Physical Medium Dependent)之间的接口标准,它只有两对差分线(收/发),共 4 根线,如图9所示。XFI 接口速度达到 10.3125 Gbps,采用 64B/66B 编码,在XAUI与XFI之间使用到 SerDes 以减小信号数。

图9. 10GbE Layer & Interface

XFP(10 Gigabit Small Form Factor Pluggable)是指应用XFI接口的光模块,应用于10G以太网的光传输。XFP光模块的尺寸略大于 SFP 和 SFP+ 光模块,三种光模块的详细对比见链接文章,在此不再赘述。

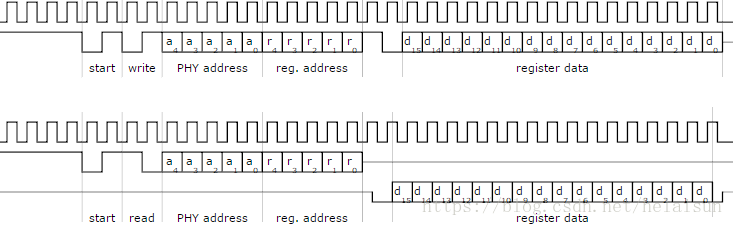

MDIO

如上文所述,MDIO用于上层(MAC)配置底层(PHY)的参数,它包括时钟信号 MDC 和数据信号 MDIO 。如果系统中不止一个PHY,在使用同一组MDIO信号以级联方式配置PHY时,需要通过PHY芯片管脚的 Strap 来寻址不同芯片。PHY芯片的物理地址Strap管脚一般与 RXD 管脚复用。在MDIO规范中定义PHY地址为 5 bit,即同一组MDIO最多可配置 2^5 = 32 个PHY。图10表示MDIO配置的时序图。

注意,这里提到的PHY芯片Strap的物理地址仅与MDIO的配置过程寻址有关,和通常意义上的 MAC 地址没有任何关系。

图10. MIIM Timing

参考资料

- Media-independent interface -Wikipedia

- IEEE 802.3 Ethernet Presentation

- Ethernet Media Access Controller (EMAC)/ Management Data Input/Output (MDIO) Module -TI

- DP83867E/IS/CS Robust, High Immunity, Small Form Factor 10/100/1000 Ethernet Physical 5. Layer Transceiver -TI

- XGMII Update -IEEE 802

- XAUI/XGXS Proposal -IEEE 802

- Overview of 10G Ethernet Family -IEEE 802

文章转载自:第22条军规:Media Independent Interface,很不错的作者,写了很多技术类的文章。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?