FPGA至简设计实例

前言

一、项目背景

上一章节中详细的讲解了数码管的显示原理和控制方式,本章不再进行赘述。通过相关原理可知 FPGA通过控制数码管的对应管脚,从而实现数码管显示的控制。在这一结论的基础上,本章将进行 更深一步的数码管显示设计。

二、设计目标

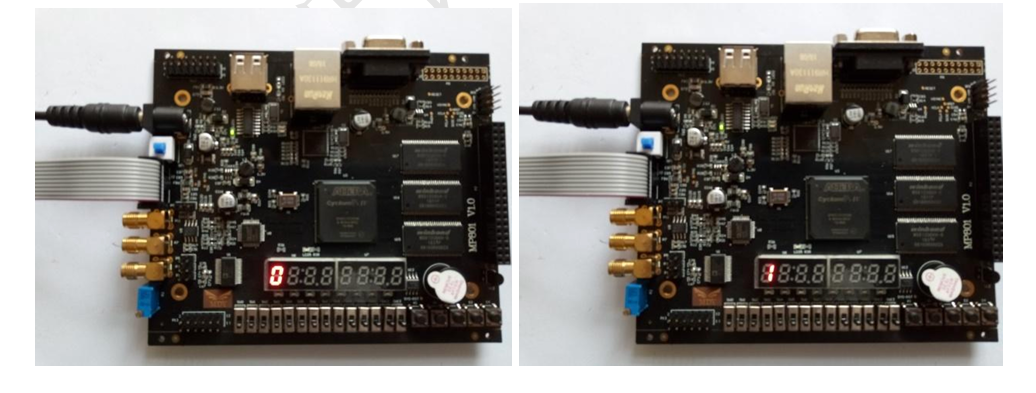

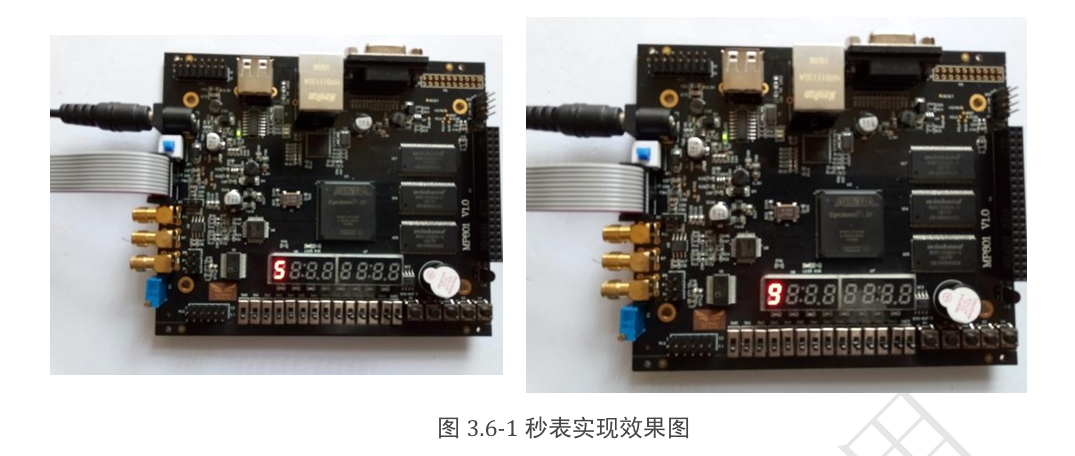

开发板上有 8 位数码管,在本次设计中只需要使用1个数码管(数码管0)来实现秒表功能, 其具体设计效果为:复位后,数码管0显示数字0并持续1秒;随后显示数字1并持续2秒;然后 显示数字2并持续3秒;以此类推,最后显示数字9并持续10秒。之后再次回到显示数字0并持续 1 秒的循环中。

三、设计实现

1. 顶层信号

新建目录:D:\mdy_book\my_time,并在此目录中,新建一个名为 my_time.v 的文件。用 GVI M打开后开始编写代码。在这里建议初学者按照本书提供的路径名以及文件名进行设置,不要自行进 行修改。因为在更改后可能会出现中文路径、空格路径等非法路径的问题,也可能会出现文件名更改 后报错的现象。而对于初学者来说,并不能很好的发现并解决问题。因此建议初学者先按照要求更名 保存,在进行多个工程设计,熟悉了各个步骤后再进行更名的操作。在此不要想当然,一时的细心可 以避免后续问题的出现。

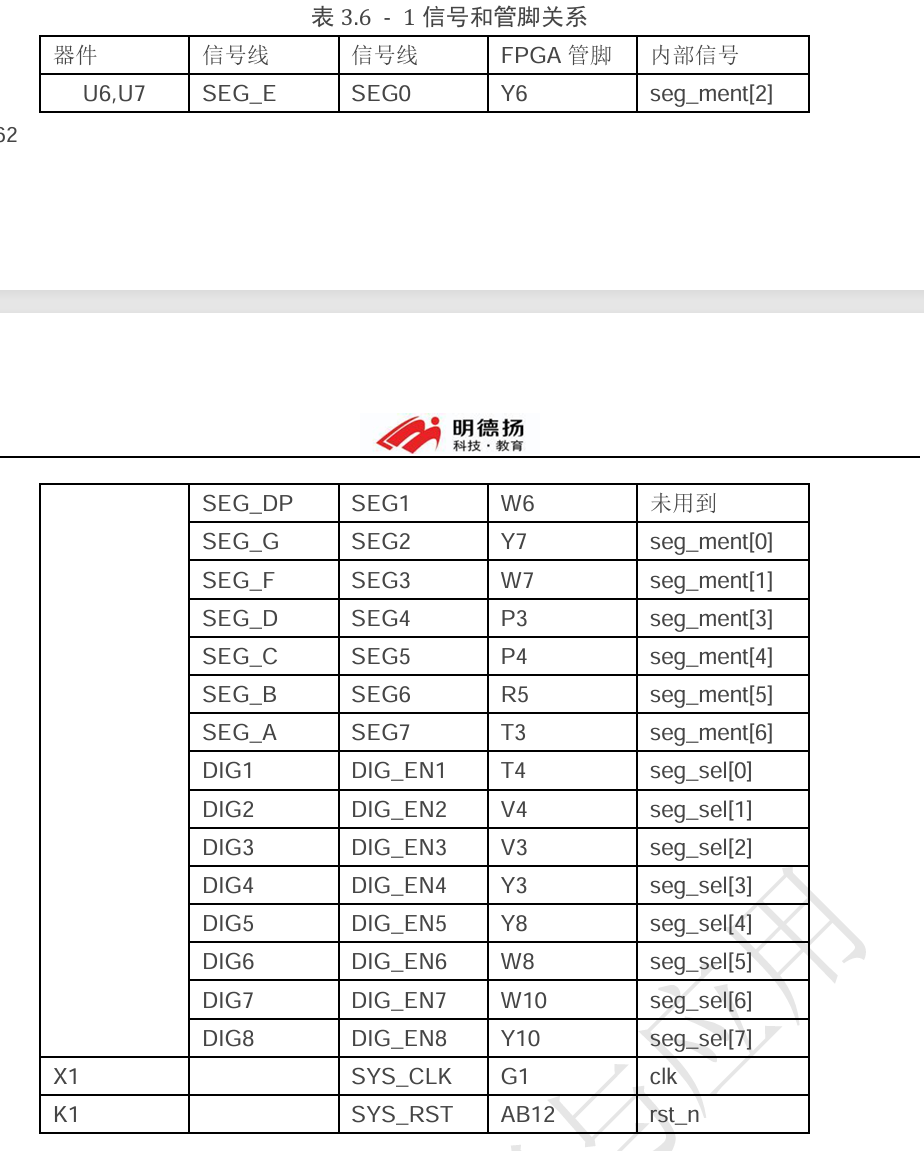

分析设计目标可知,本次设计要实现的功能是控制数码管 0 根据不同时间显示不同的数字并持 续一定的时间。在这个过程中,8个数码管中只有数码管0进行显示变换,其他数码管不亮。上一章 中对数码管的控制方法进行了讲解,如果有需要可以回到上一章复习。FPGA通过控制位选信号来控 制8个数码管,即应输出一个8位的位选信号,将其设定为seg_sel。其中seg_sel[0]对应数码管0, seg_sel[1]对应数码管1,以此类推,seg_sel[7]对应数码管7。而实现数码管上的不同数字显示则需 控制每个数码管上的7个子段,即控制段选信号使数码管上显示相应的数字。本设计中不需要用到h 子段,共需要7个子段,因此FPGA要输出一个7位的段选信号来控制数码管显示,将段选信号设 为seg_ment。其中seg_ment[6]~segm_ment[0]分别对应数码管的abcdefg(注意对应顺序)。当然, 除位选信号和段选信号外,设计中进行工程控制的时钟信号和复位信号也同样必不可少。

综上所述,本设计一共需要4个信号:时钟信号clk,复位信号rst_n,输出的位选信号seg_sel 和输出的段选信号seg_ment。信号和硬件的对应关系如下表所示。

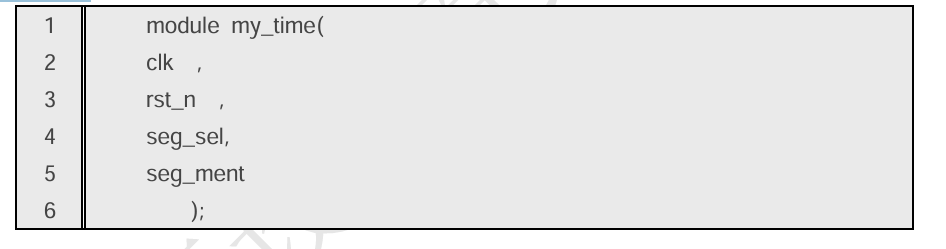

将module的名称定义为my_time,已知该模块有4个信号:clk、rst_n、seg_sel和seg_ment。 在顶层信号代码中需要将与外部相连接的输入/输出信号列出,从而实现信号与管脚的连接,其具体 代码如下:

随后对信号输入输出属性进行声明,指出这一信号对于FPGA来说属于输入信号还是输出信号, 若为输入信号则声明其为input,若为输出信号则声明其为output。在本设计中,由于clk是外部的晶 振输送给FPGA,因此在FPGA中clk为1位的输入信号input;同样地,rs

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?