一、基础概念与工作原理对比

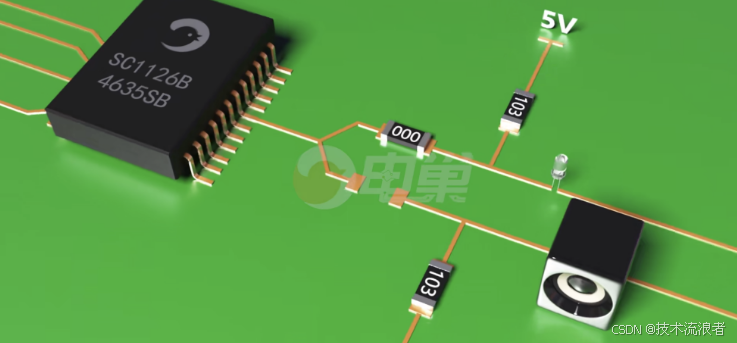

在混合信号电路设计中,数字地与模拟地的隔离是抑制噪声干扰的关键技术手段。0欧电阻与磁珠作为两种常见隔离元件,其原理和应用场景差异显著。

1. 0欧电阻的核心特性

0欧电阻并非理论上的零阻抗器件,其实际阻值在毫欧级(如50mΩ以内),且具有寄生电感(约几nH)。它的核心作用包括:

- 单点接地:通过狭窄电流路径限制地回路面积,减少数字噪声耦合至模拟区域。

- 全频段衰减:所有频段的信号均会因微小阻抗产生压降,综合抑制高低频干扰。

- 灵活跳线功能:替代飞线优化PCB布局,同时支持调试阶段参数调整。

2. 磁珠的核心特性

磁珠由铁氧体材料构成,等效于电阻与电感串联的频变器件。其特性表现为:

- 高频带阻滤波:在特定频率点(如100MHz)呈现高阻抗,吸收噪声能量。

- 频段选择性:需预判噪声频点选择型号,低频段阻抗接近于导线。

- EMI专项抑制:广泛应用于射频、时钟信号等高频干扰场景。

二、性能参数与适用场景对比

1. 噪声抑制机制

- 0欧电阻:通过微小阻抗限制地环路电流,降低共模干扰。例如,在低速ADC电路中,可阻断数字开关噪声通过地平面耦合至模拟前端。

- 磁珠:针对高频噪声(如DDR时钟谐波)形成阻性衰减,如选用100Ω@100MHz型号可滤除数字电源中的开关噪声。

2. 频率响应特性

- 0欧电阻:阻抗随频率线性上升(Z≈jωL),但对全频段均有衰减,适用于宽频噪声场景。

- 磁珠:阻抗曲线呈谐振特性,最佳抑制频段需匹配噪声频谱。如在蓝牙模块中选用2.4GHz专用磁珠可显著降低射频干扰。

3. 电流承载能力

- 0欧电阻:额定电流由封装尺寸决定(如0805封装支持2A),需避免过流熔断风险。

- 磁珠:直流阻抗低(<0.1Ω),适合大电流电源隔离,如FPGA的模拟供电模块中可承载3A以上电流。

4. 物理特性与成本

- 0欧电阻:体积小(0402封装常见)、成本极低(约0.001美元/片),适合高密度PCB设计。

- 磁珠:体积较大(如0805封装)、单价较高(约0.05美元/片),需预留更多布局空间。

三、典型应用场景与选型指南

1. 优先选择0欧电阻的场景

- 低频混合信号系统:如温度传感器信号链(<1MHz),数字MCU与模拟放大电路间的地隔离。

- 调试与兼容设计:预留位置便于后期更换为磁珠或电感,或在量产时统一焊接降低成本。

- 紧凑型PCB布局:手机主板等空间受限场景,使用0402封装0欧电阻实现微型化设计。

2. 优先选择磁珠的场景

- 高频数字电路:如DDR4内存接口(>1GHz),抑制数据线串扰至模拟视频输出。

- 射频前端模块:在Wi-Fi/BT模块的电源入口串联磁珠,阻断PA噪声回灌至数字电源。

- 多级电源隔离:FPGA系统中对1.0V核电源与3.3V IO电源进行分层滤波。

四、进阶设计技巧与风险规避

1. 混合使用策略

- 级联滤波架构:在开关电源输出端先串联磁珠(滤除高频纹波),再并联0欧电阻提供直流路径,兼顾高频抑制与故障保护。

- 分割地平面设计:使用多个0欧电阻构成星型接地拓扑,避免单点失效导致地电位飘移。

2. 参数量化选型方法

- 磁珠选型公式:依据噪声频率f与目标阻抗Z,计算所需磁珠型号。例如,抑制200MHz噪声需选Z=150Ω@200MHz的磁珠。

- 0欧电阻电流校验:根据I²·R计算温升,如0805封装0欧电阻在2A电流下功耗为0.1W,需确保PCB散热设计。

3. 常见设计误区

- 磁珠滥用:在DC-DC电源低频纹波(<1MHz)场景使用磁珠,反而因低频阻抗不足导致滤波失效。

- 0欧电阻过载:电机驱动电路中使用0603封装0欧电阻承载5A电流,引发烧毁故障。

五、扩展应用与未来趋势

1. 高频化场景的复合方案

在5G毫米波电路中,采用LTCC(低温共烧陶瓷)磁珠与薄膜0欧电阻集成模块,实现24GHz频段的噪声隔离与阻抗匹配。

2. 智能化可调器件

数字可调磁珠(如TDK ZJYS81系列)通过I²C接口动态调节阻抗特性,适应多频段噪声环境。

3. 三维封装技术

将0欧电阻与磁珠垂直堆叠于HDI板内层,减少表面贴装面积,适用于AR眼镜等微型设备。

通过系统性对比可见,0欧电阻与磁珠在PCB地隔离设计中各具优势。工程师需综合噪声频谱、电流需求、成本及布局空间等因素,选择最优方案或组合策略,并结合仿真工具(如ANSYS SIwave)验证设计效果,方能实现高可靠性的混合信号系统设计。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?