Code density

- The Xtensa core ISA is implemented as 24-bit instructions

- This instruction width pro- vides a direct 25% reduction in code size compared with 32-bit ISAs

Xtensa ISA provides a Windowed Registers Option. Xtensa windowed registers re- duce code size by:

- Eliminating register saves and restores at procedure entry and exit

- Reducing argument shuffling

- Allowing more local variables to live permanently in registers

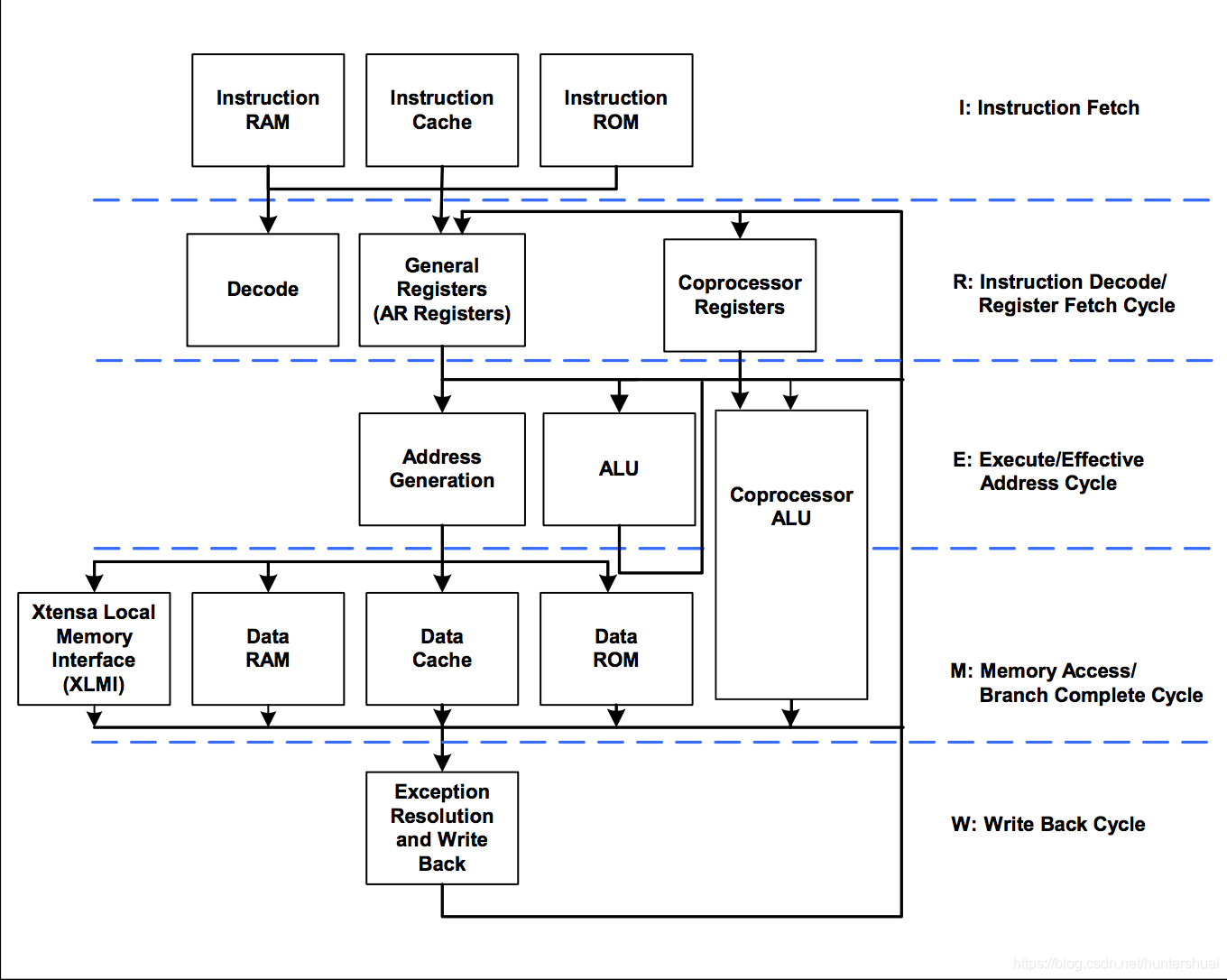

Pipeline

multi-core support

break-in/break-out

atomic operation:

- L32EX, S32EX,and GETEX instructions

- A load exclusive instruction loads data from a memory location.

- Some computation on the loaded data is performed.

- An exclusive store with the updated value is stored to the same memory location.

- The exclusive store succeeds if no other master has performed a store to that location.

- The exclusive store fails if the location was updated by another master since it was read.

An Xtensa processor can issue exclusive operations on its outbound AXI master port to perform atomic access on a remote address.

ref:

- Memory Consistency and Event Ordering in Scalable Shared-Memory Multiprocessors

xtensa windowed register

The Xtensa Windowed Registers Option saves power by reducing the number of dynamic data-memory references and increasing the opportunities for variables to reside in registers, where accesses require less power than memory accesses.

The WAITI (Wait for Interrupt) instruction, which is a part of the Interrupt Option, saves power by setting the current interrupt level, powering down the processor’s logic, and waiting for an interrupt.

本文探讨了Xtensa处理器的ISA实现及其如何通过24位指令宽度减少代码大小25%,与32位ISA相比。Xtensa的窗格寄存器选项减少了动态数据内存引用,增加了变量存储在寄存器的机会,从而节省了电力。文章还介绍了原子操作,如L32EX、S32EX和GETEX指令,以及它们在远程地址上执行原子访问的能力。

本文探讨了Xtensa处理器的ISA实现及其如何通过24位指令宽度减少代码大小25%,与32位ISA相比。Xtensa的窗格寄存器选项减少了动态数据内存引用,增加了变量存储在寄存器的机会,从而节省了电力。文章还介绍了原子操作,如L32EX、S32EX和GETEX指令,以及它们在远程地址上执行原子访问的能力。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?