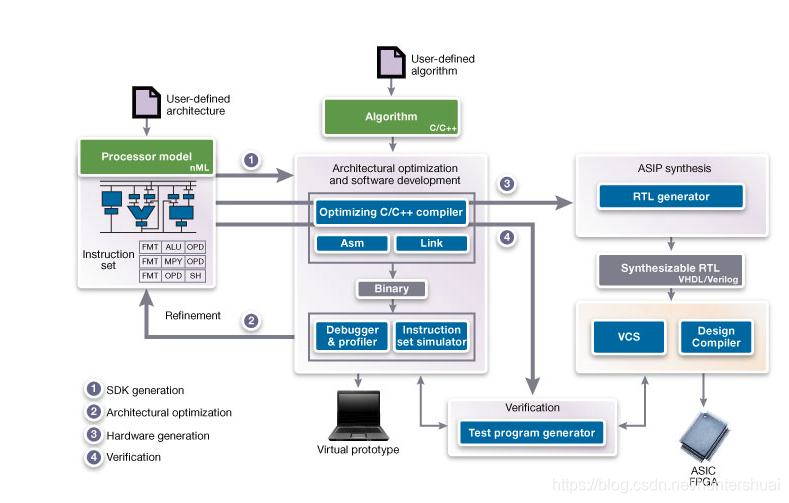

- using nML description language, it can generate the core processor instruction, and it will used as input to whole sdk

- using sdk, the target algorithm written with

clanguage can compile and linked to a target binary

- debug use debugger and profiler

- simulate in instruction simulator

- according to the profile and debug result, refine the nML - when the nML model is ready, it will serve as input the RTL generator, and output RTL code

- Assembly-level test programs with high fault coverage are generated, to verify the

correctness of the RTL implementation in its environment. These test programs can be executed

both in the RTL model (RTL simulator) and in the instruction-set simulator, and simulation results

are automatically compared.

ASIP Designer’s patented technology supports the following features:

-

Modeling of ASIP instruction-set architectures in the nML processor description language. nML is a high-level definition language for describing a processor architecture and instruction set (ISA). nML offers designers the abstraction level of a programmer’s manual of a processor. Also, with nML the ASIP’s periphery can be modeled in a cycle- and bit-accurate way. nML offers unprecedented architectural breadth, enabling IP development for almost any vertical market.

-

Unique compiler-in-the-loop technology, enabled by the automatic generation of a comprehensive software development kit (SDK) for each ASIP modeled in nML, containing the following components:

An optimizing compiler, recognized for its efficient code generation and quick and automatic retargetability to new ASIP architectures. The compiler supports C (optionally extended with user-defined data types and operators using C++ classes and function overloading), C++, and OpenCL C (OpenCL kernel language). The compiler can cope well with architectural peculiarities of DSP cores. It supports instruction-level and data-level parallelism, deeply pipelined instructions, specialized arithmetic functions, custom data-types, specialized address generation units, heterogeneous register structures, and various degrees of instruction encoding (ranging from VLIW to highly encoded instruction sets).

A linker that builds an executable file from separately compiled Elf/Dwarf object files for different C functions.

An assembler and disassembler that translates machine code from assembly into binary format and back.

A fast instruction-set simulator, offering both cycle-accurate and instruction-accurate abstraction levels generated from the same nML model, and easy integration into cycle-accurate and transaction-level virtual prototypes. -

A flexible (multicore) debugger, which can be used in connection to both instruction-set simulators and on-chip debug hardware (via JTAG).

-

Multi-faceted profiling capabilities to analyze the instruction-set architecture for hot-spots and to drive the architectural optimization process.

-

Automatic generation of a power and area efficient hardware implementation of each ASIP, in synthesizable Verilog or VHDL. A JTAG interface and a debug controller can optionally be generated, to support on-chip debugging.

-

Multi-faceted verification capabilities, including the automatic generation of ASIP-specific test programs in C and assembly code.

Reference:

本文介绍了使用nML描述语言生成核心处理器指令,作为SDK输入,经编译链接生成目标二进制。可进行调试、模拟并优化nML,最终生成RTL代码。还阐述了ASIP Designer的专利技术,包括nML建模、编译器循环技术等,具备多方面功能。

本文介绍了使用nML描述语言生成核心处理器指令,作为SDK输入,经编译链接生成目标二进制。可进行调试、模拟并优化nML,最终生成RTL代码。还阐述了ASIP Designer的专利技术,包括nML建模、编译器循环技术等,具备多方面功能。

1195

1195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?