1、梳理概念:sp,sm,thread,block,grid,warp

(1)硬件上, SP(streamingProcess),SM(streaming multiprocessor)。

SP:最基本的处理单元,也称为CUDA core。CUDA Core是NVIDIA在推出全新的Fermi架构后才出现的一个名词。简单的说,CUDACore就是以前所说的流处理器,是类似的东西,只是名字上的叫法不同而已,不过还是有区别的,具体区别查阅相关资料。最后具体的指令和任务都是在SP上处理的。GPU进行并行计算,也就是很多个SP同时做处理。

SM:多个SP加上其他的一些资源组成一个SM。也叫GPU大核,其他资源如:warpscheduler,register,sharedmemory等。SM可以看做GPU的心脏(对比CPU核心),register和sharedmemory是SM的稀缺资源。CUDA将这些资源分配给所有驻留在SM中的threads。因此,这些有限的资源就使每个SM中active warps有非常严格的限制,也就限制了并行能力。

需要指出:每个SM包含的SP数量依据GPU架构而不同,Fermi架构GF100是32个,GF10X是48个,Kepler架构都是192个,Maxwell都是128个。相同架构的GPU包含的SM数量则根据GPU的中高低端来定。

(2)软件上,hread,block,grid,warp。

thread:一个CUDA的并行程序会被以许多个threads来执行。

block:数个threads会被群组成一个block,同一个block中的threads可以同步,也可以通过sharedmemory通信。

grid:多个blocks则会再构成grid。

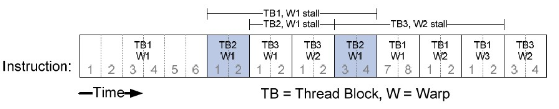

warp: GPU 执行程序时的调度单位,目前 cuda 的 warp 的大小为 32 ,同在一个 warp 的线程,以不同数据资源执行相同的指令 , 这就是所谓 SIMT-- Single InstructionMultiple Thread 。

2、硬件映射

Nvidia把32个threads组成一个warp,warp是调度和运行的基本单元。warp中所有threads并行的执行相同的指令,warp具有挂起,就绪,执行四种状态,由SM的硬件warpscheduler负责调度,达到隐藏延迟的作用。容忍长延迟操作,例如浮点算术及分支指令,大量的warp使得硬件可以在任意时间点找到一个可调度的warp。

由于每个SM上的硬件资源是有限的,所以每个SM上可以同时驻扎的block数量和thread数量是有限制的,相关限制可以在相关的手册中查询。例如:对于GT200,SM上最多驻扎8个block,每个SM最多驻扎1024个thread,GT200至多驻留30720线程。

好的执行配置:每个SM中的线程数达到容量最大值且对于长延迟操作可调度最大数量的warps.

一个SP可以执行一个thread,在GPU中可以同时(同一时钟周期内)执行的thread数量为总的sp数量,也就是总的CUDA核数量(个人理解,不一定正确,这个对性能提升没有太大的作用)。

411

411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?