基于FPGA的iic主从机驱动实现

Verilog实现iic slave和iic master

顶层模块实现master对slave自定义的寄存器读取

带仿真模块

基于FPGA的IIC主从机驱动实现

摘要:本文基于FPGA设计了一种IIC主从机驱动方案,通过Verilog语言实现了IIC从机和IIC主机的功能,并在顶层模块中实现了主机对从机自定义寄存器的读取。同时,我们还设计了仿真模块进行功能验证和性能评估。本文将详细介绍整个系统的设计思路、Verilog编程技巧以及仿真测试结果。

1. 引言

随着现代电子设备的发展,IIC(Inter-Integrated Circuit)总线作为一种常用的串行通信协议,被广泛应用于各种领域。FPGA作为可编程逻辑器件,具有可实现高度定制化的特点,因此被广泛用于IIC主从机的设计与实现。

2. 系统设计

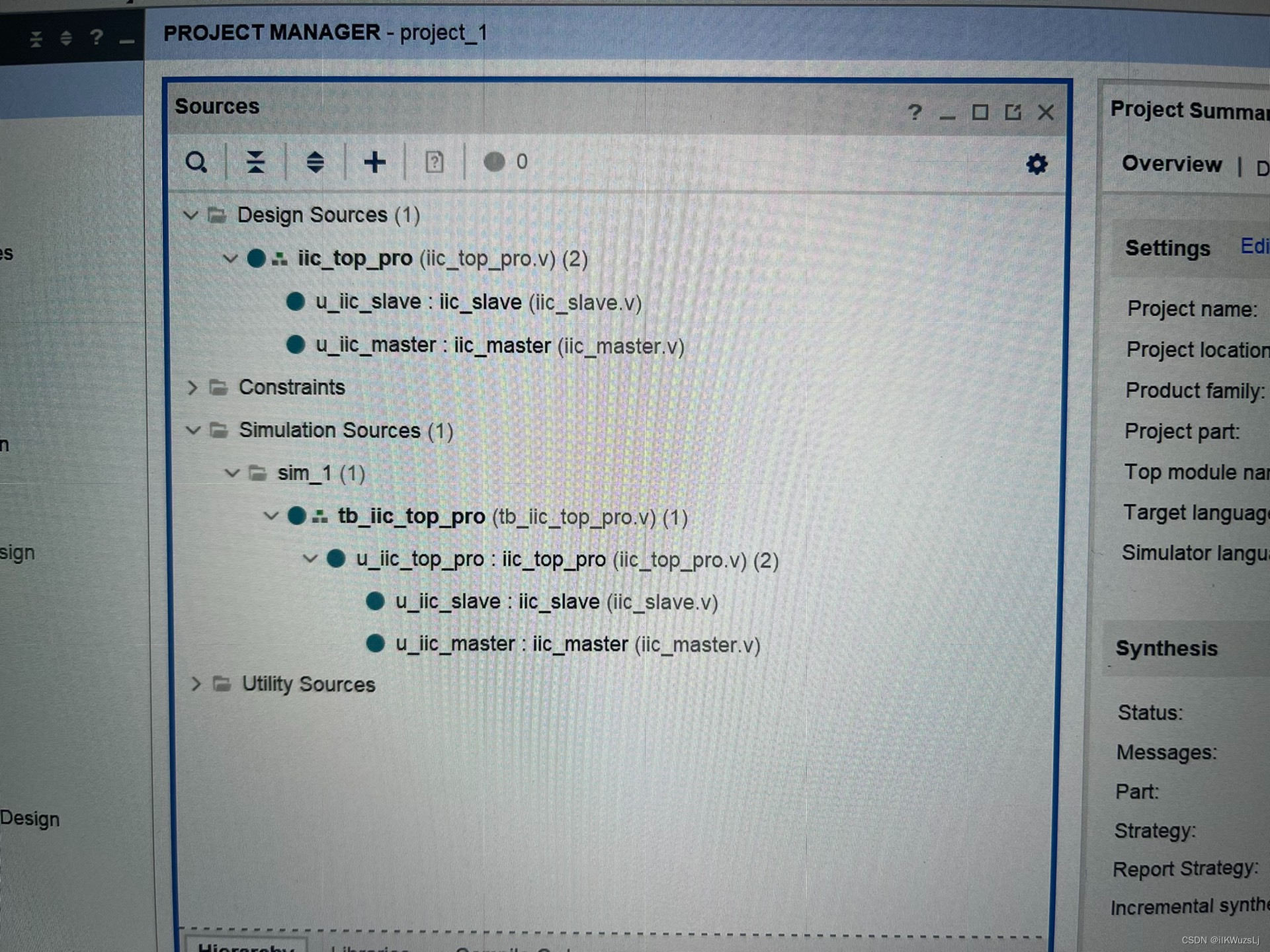

本系统基于FPGA实现了一个包含IIC主机和IIC从机的通信系统。我们使用Verilog语言进行模块设计和功能实现。系统主要由以下模块组成:

- IIC主机模块:负责发送开始信号、地址和数据,并接收从机的应答信号。

- IIC从机模块:负责接收主机的开始信号、地址和数据,并给出应答信号。

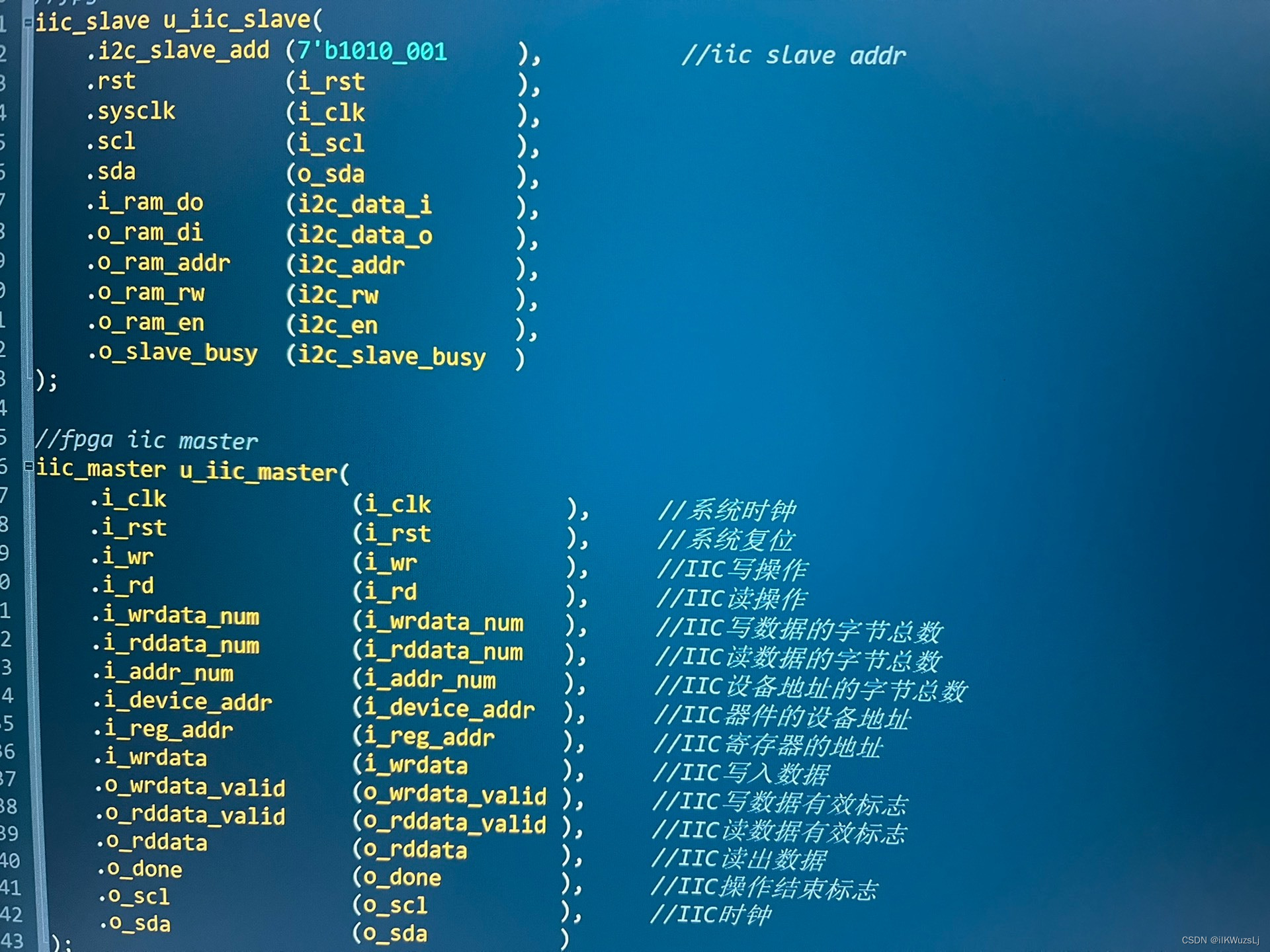

- 顶层模块:实现主机对从机自定义寄存器的读取,并进行相应的处理。

3. 模块设计与实现

3.1 IIC主机模块设计与实现

在IIC主机模块中,我们需要实现发送开始信号、地址和数据的功能。为了保证数据的可靠传输,我们还需要接收从机发送的应答信号。通过Verilog编程,我们可以使用状态机的方式来实现这些功能,并确保数据的准确性和稳定性。

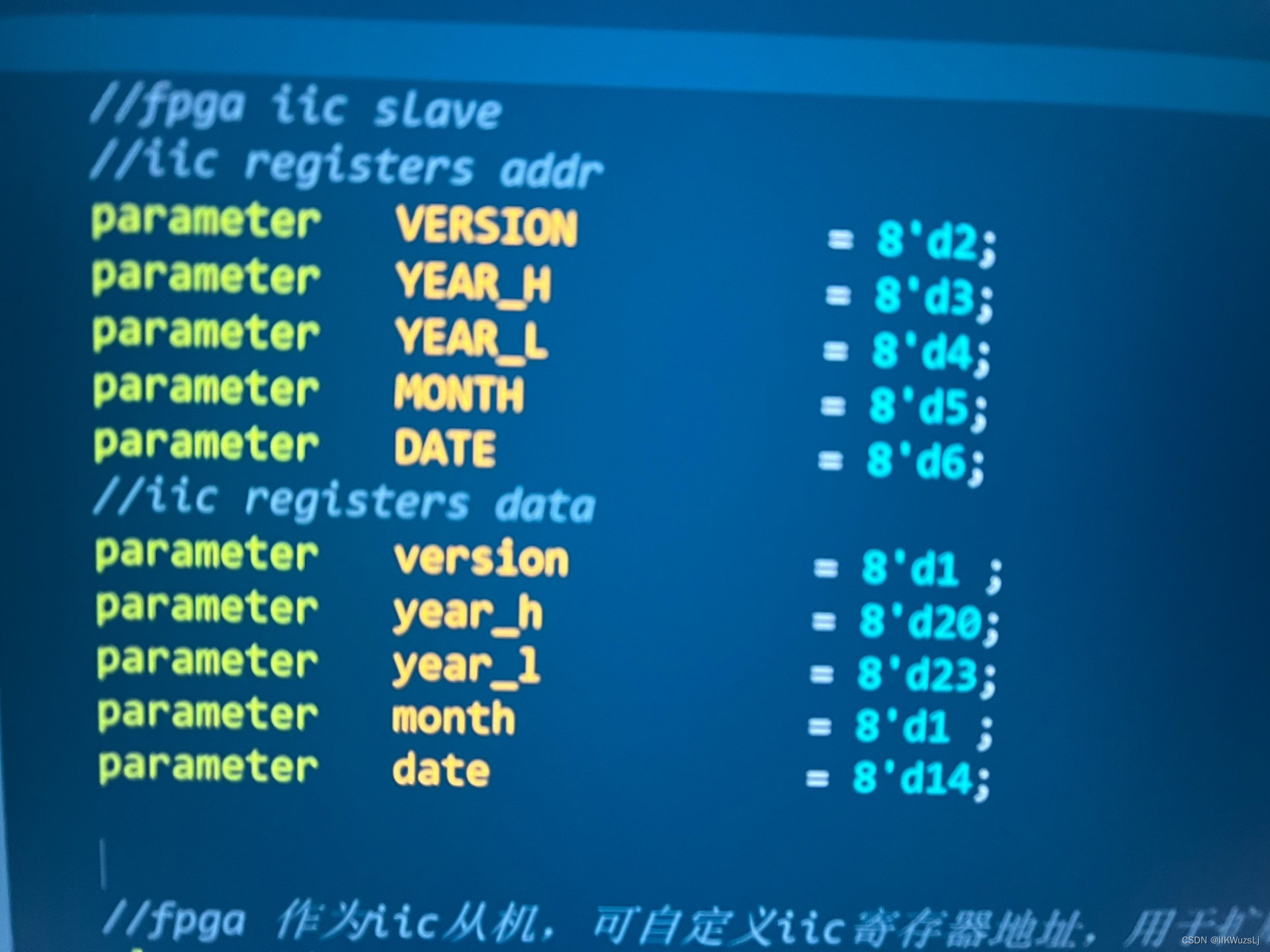

3.2 IIC从机模块设计与实现

在IIC从机模块中,我们需要实现接收主机发送的开始信号、地址和数据,并给出应答信号。为了保证通信的稳定性,我们还需要在遇到异常情况时能够正确处理,并发出相应的应答信号。通过Verilog编程,我们可以使用有限状态机的方式来实现从机模块的功能。

3.3 顶层模块设计与实现

在顶层模块中,我们需要实现主机对从机自定义寄存器的读取功能。首先,主机发送开始信号,并发送从机的地址和读取命令。然后,从机接收到命令后,根据地址进行相应的处理,并将自定义寄存器的数据返回给主机。

4. 仿真测试与性能评估

为了验证系统的功能和性能,我们设计了仿真模块进行测试。通过对各个模块的输入和输出进行监测,我们可以检查各个功能是否正常工作,并评估系统的性能指标,如通信速率和可靠性。

5. 结论

本文基于FPGA设计了一种基于IIC主从机的通信系统,并通过Verilog语言实现了各个模块的功能。通过对各个模块的设计和实现,我们成功实现了主机对从机自定义寄存器的读取功能,并使用仿真模块对系统进行了验证和性能评估。未来,我们可以进一步优化系统的稳定性和可靠性,并对其扩展更多应用场景。

相关代码,程序地址:http://imgcs.cn/lanzoun/697687398406.html

本文详细描述了如何使用Verilog在FPGA上实现IIC主从机结构,包括IICslave和IICmaster模块的编程,以及顶层模块中自定义寄存器的读取功能。同时,文中包含了功能验证和性能评估的仿真模块设计。

本文详细描述了如何使用Verilog在FPGA上实现IIC主从机结构,包括IICslave和IICmaster模块的编程,以及顶层模块中自定义寄存器的读取功能。同时,文中包含了功能验证和性能评估的仿真模块设计。

4023

4023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?