1. arm cortex M3/4的STRD/LDRD指定必须是word(4字节)对齐,不同于strh,str,ldr,ldrh等指令(这些指令在M3/4体系结构硬件自动支持非对齐访问,不过会影响效率,一条指令对应多个总线访问)

2. 所以在遇到编译器编译出STRD/LDRD指令时,一定要注意操作数(mem地址)需要4字节对齐,不然会报hard fault错误

3. 目前我还没有找到如何避免编译器编译出STRD/LDRD指令,只能遇到hard fault时候重新修改代码。编译器不会检查STRD/LDRD指令的对齐问题。

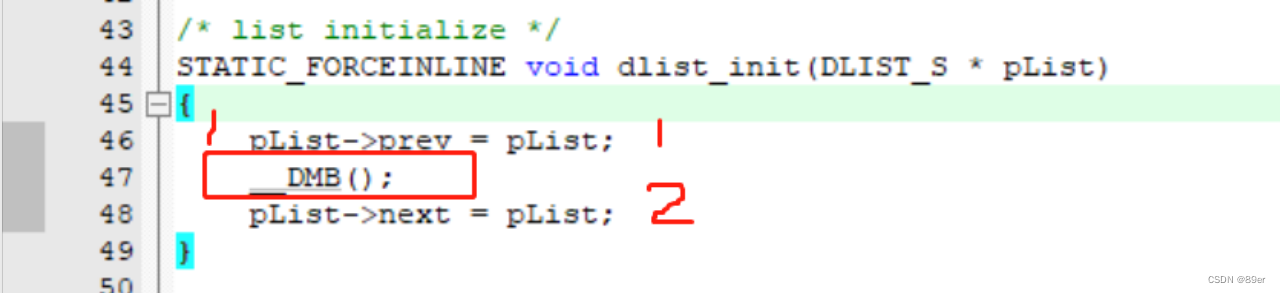

举例:

上述代码1和2,两条指针赋值,编译器就可能编译出STRD指令。原本中间没有__DMB();

上述代码1和2,两条指针赋值,编译器就可能编译出STRD指令。原本中间没有__DMB();

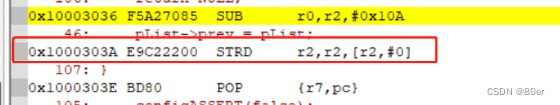

对应汇编如上,这两条C语句直接被编译器优化成0x1000303a一条STRD指令,但是由于r2刚好对应的内存地址非word对齐,就出现了hard fault!

目前我的做法是在中间加了内存barrier,让编译器不要优化出STRD指令可以解决。(但这肯定不是解决方案)。

应该要找到如何让编译器编译出类似指令的时候检查操作数是否对齐,或者认为能够提前预判编译器行为,尽量避免写出让编译器优化出此类指令的语句??!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?