目录

一、实验名称

用74LS160和74LS138(3线—8线译码器)和必要的门电路设计一个灯光控制逻辑电路。

二、实验目的

(1)掌握中规模集成寄存器构成的时序逻辑电路的设计方法。

(2)掌握中规模集成计数器设计N进制计数器的方法。

(3)学会用时序功能器件构成综合型应用电路。

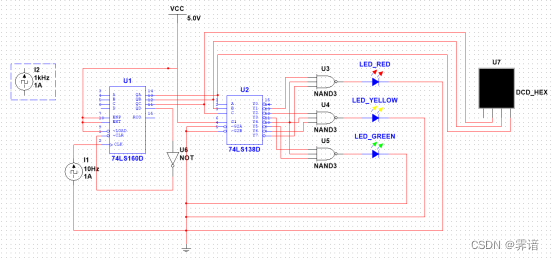

三、实验电路

四、实验软件与环境:

实验软件:NI Multisim14.0

实验环境:Windows10

五、实验内容与步骤

1.实验内容

(1)用74LS160和74LS138(3线—8线译码器)和必要的门电路设计一个灯光控制逻辑电路。

(2)要求红、绿、黄三种颜色的灯在时钟信号作用下按下表规定的顺序转换状态。表中的1表示“亮”,0表示“灭”。要求电路能自启动。

(3)三个灯接到LED上进行显示。

(4)十进制计数器74LS160输出接7段数码管,观察并记录结果。

下表为三种灯的状态转换顺序表:

2.理论与电路设计部分

(1)观察表1可得:红、黄、蓝3种颜色的灯在时钟信号的作用下在8个状态下反复循环,故考虑利用八进制计数器来实现这种状态转换。由于提供的计数器器材为一片74LS160(同步十进制加法计数器),故考虑将该十进制规模集成计数器转化设计为八进制计数器。

采用异步清零法进行进制的转换:

由于需要将十进制转换为八进制,在采用异步清零的情况下,输出端计数为8个脉冲时的状态为暂态,即输出Q端出现1000时,电路需要产生清零信号,输出立即变为0000进行异步清零。观察到此时输出端QD首次由0转变为1,故考虑将QD接一非门并与清零端CLR相连,实现此时需要的CLR端的低电平输入,进位输出端采取QD实现。此外,对于74LS160而言,还需将END端、ENT端、LORD端置1,来确保计数器的正常工作。

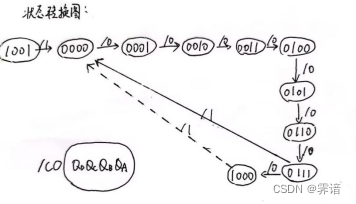

状态转换图如下图所示(进行进制转换后的74LS160的状态转换图):

由图中的循环可得,该电路可以自启动。

(2)考虑到输出端QD并未实际向外输出数据,故计数器的输出状态实际上由QC QB QA构成,当CP脉冲计数为0~7时,QC QB QA向外输出对应的二进制信号,若用R、Y、G分别表示红、黄、绿三个输出,则可列出QC QB QA与R、Y、G之间关系所对应的真值表(QC QB QA与R、Y、G之间对应的真值表):

| QC | QB | QA | R | Y | G |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 |

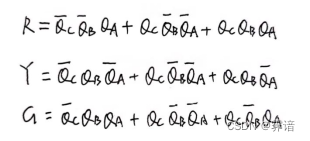

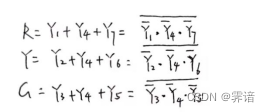

通过真值表写出逻辑关系式:33

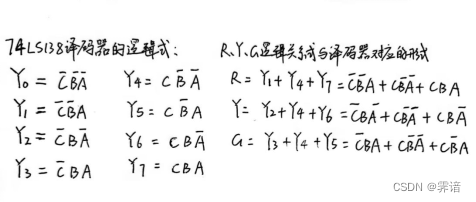

(3)选择提供的74LS138(3线—8线译码器)作为用用函数发生器,接受来自计数器的输出信号QC QB QA,并产生输出的R、Y、G信号。将QA、QB、QC分别与74LS138的A、B、C端相连便可将上述的逻辑关系式转化成与译码器输出逻辑式对应的形式:

3.仿真部分

对于计数器74LS160而言,除了输出端QA、QB、QC分别与74LS138的A、B、C端相连以及QD通过非门与CLR端相连以外,还需将END端、ENT端、LORD端置1(在电路中表现为接入电源)以及CLK端与一时钟电流源CLOCK_CURRENT相连来确保计数器的正常工作,该源的另一端接地。

对74LS138而言,考虑到其特殊的控制端G1、G2A、G2B分别输入高电平1、低电平0,低电平0时译码器才会正常工作,故将之分别接电源与接地。输入端A、B、C与计数器74LS160的QA、QB、QC相连。 输出端则根据上述的表达式进行设计。

由于该译码器输出低电平的特性,我们将表达式转换为低电平输出的与非式:

并分别将R、Y、G对应的三个输出端作为与非门的输入端连接即可。将五个输出端的输出结果作为与非门的输入端连接即可。为了使输出结果表示出来,将R、Y、G对应的与非门分别接到红、黄、绿三色的LED灯上。此外,按照题目要求,将计数器的QA、QB、QC分别与一七段数码管的最低三位相连,使数码管可以显示脉冲次数。根据三盏LED灯亮的数量和顺序以及数码管显示的数字来判断实验结果是否正确。

六、实验结果

当数码管显示为0时,红灯、黄灯、绿灯均不亮;

当数码管显示为1时,红灯亮,黄灯、绿灯不亮;

当数码管显示为2时,黄灯亮,红灯、绿灯不亮;

当数码管显示为3时,绿灯亮,红灯、黄灯不亮;

当数码管显示为4时,红灯、黄灯、绿灯均亮;

当数码管显示为5时,绿灯亮,红灯、黄灯不亮;

当数码管显示为6时,黄灯亮,红灯、绿灯不亮;

当数码管显示为7时,红灯亮,黄灯、绿灯不亮;

此后,数码管的计数回到0,开始新一轮循环,而三盏灯亮的情况也重新循环,实验结果符合实验前理论推演所作出的假设。

6651

6651

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?