一. NVIC和系统控制块特性

1. 灵活的中断管理:使能/禁止中断,优先级配置

2. 硬件嵌套中断支持

3. 向量化的异常入口

4. 中断屏蔽

5. NVIC寄存器的起始地址:0xE000E100, 对其访问必须是每次32bit

6. SCB的起始地址: 0xE000E010,也是每次32bit访问。

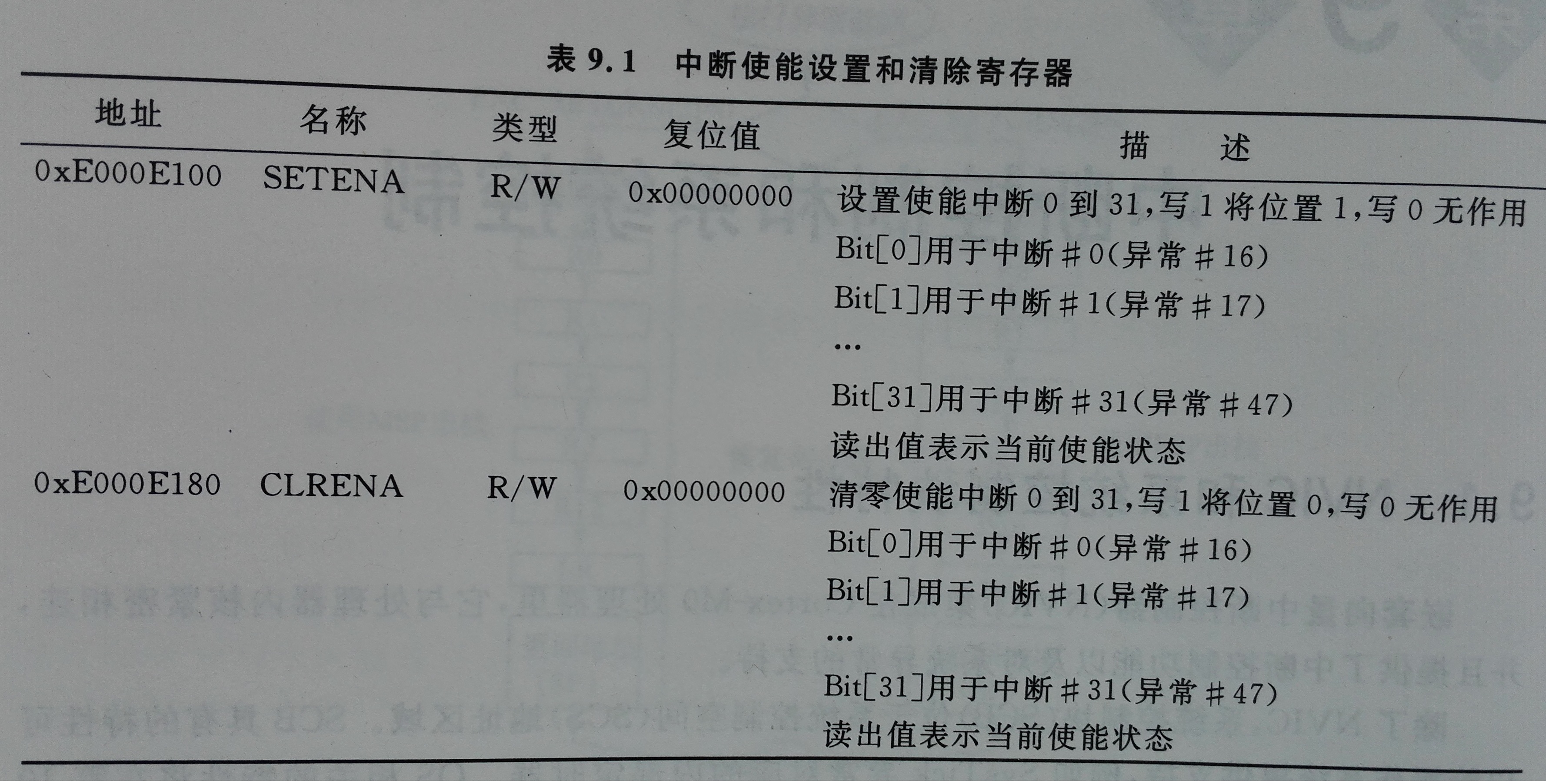

二. 中断使能和清除使能

1. 中断寄存器是可编程的,用于控制中断请求(异常编号16以上)的使能(SETENA)和禁止(CLRENA), 如下所示:

2. 使能/禁止 中断的代码:

1). C代码:

*(volatile unsigned long) (0xE000E100) = 0x4 ; //使能#2中断

*(volatile unsigned long) (0xE000E180) = 0x4 ; //禁止#2中断 2). 汇编代码:

LDR R0, =0xE000E100 ; //SETEAN寄存器的地址

MOVS R1, #04 ; //设置#2中断

STR R1, [R0] ; //使能中断#2 3). CMSIS标准设备驱动函数:

void NVIC_EnableIRQ(IRQn_Type_IRQn); //使能中断#IRQn;

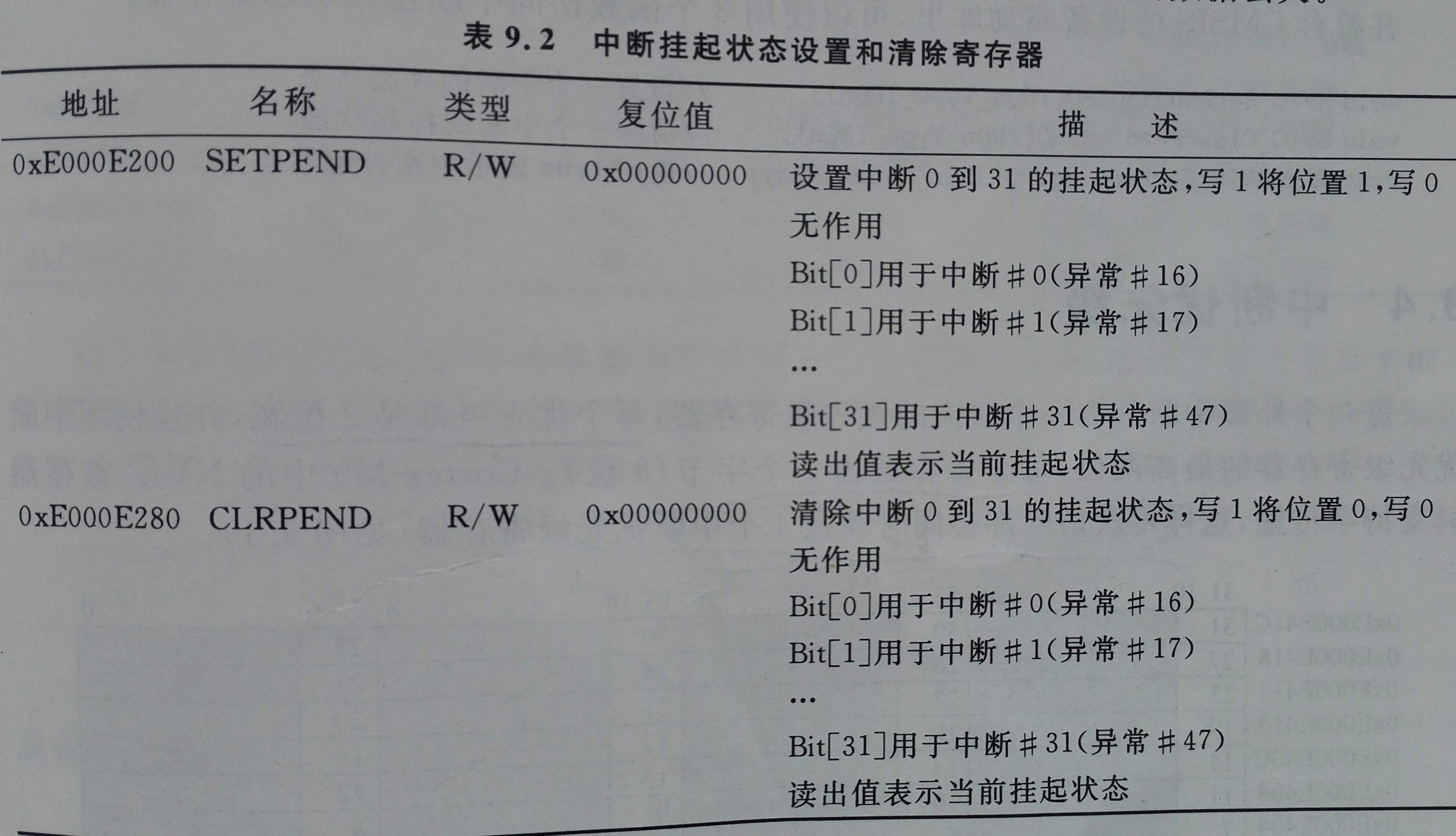

void NVIC_DisableIRQ(IRQn_Type_IRQn); //禁止中断#IRQn;三. 中断挂起和清除挂起:

1. 可以通过操作中断挂起(SETPEND)和清除挂起(CLRPEND),这两个寄存器来访问和修改中断挂起状态。

2.挂起/清除挂起的代码:

1). C代码:

这篇学习笔记详细介绍了Cortex-M0的中断控制和系统控制,包括NVIC的功能、中断使能和清除、优先级设置、异常屏蔽、中断输入行为以及系统控制寄存器的配置。

这篇学习笔记详细介绍了Cortex-M0的中断控制和系统控制,包括NVIC的功能、中断使能和清除、优先级设置、异常屏蔽、中断输入行为以及系统控制寄存器的配置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

171

171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?