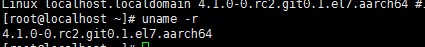

在mustang机器上安装了Centos7,并升级内核到4.1.0-0.rc2

但是dmesg发现并不支持kvm,

[ 0.343796] kvm [1]: GICV size 0x2000 not a multiple of page size 0x10000

[ 0.343802] kvm [1]: error: no compatible GIC info found

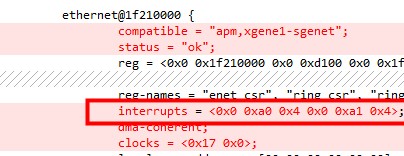

[ 0.343909] kvm [1]: error initializing Hyp mode: -6在这里有相关的patch,https://bugzilla.redhat.com/show_bug.cgi?id=1165290,但是打上补丁后虽然能够解决掉kvm的bug,但是又引入了新的问题,ethernet1和eth2识别不了,因为新的内核解析的时候需要增加对应的interrupt reg

按照如下修改后即可,好用的mustang.dts如下:

/dts-v1/;

/ {

model = "APM X-Gene Mustang board";

compatible = "apm,mustang", "apm,xgene-storm";

#address-cells = <0x2>;

#size-cells = <0x2>;

interrupt-parent = <0x1>;

pmu {

interrupts = <0x1 0xc 0xff04>;

compatible = "arm,armv8-pmuv3";

};

soc {

compatible = "simple-bus";

ranges;

#address-cells = <0x2>;

#size-cells = <0x2>;

sata@1a800000 {

reg = <0x0 0x1a800000 0x0 0x1000 0x0 0x1f230000 0x0 0x1000 0x0 0x1f23d000 0x0 0x1000 0x0 0x1f23e000 0x0 0x1000>;

interrupts = <0x0 0x88 0x4>;

compatible = "apm,xgene-ahci";

dma-coherent;

status = "ok";

};

serial@1c020000 {

reg = <0x0 0x1c020000 0x0 0x1000>;

interrupts = <0x0 0x4c 0x4>;

reg-shift = <0x2>;

compatible = "ns16550a";

clock-frequency = <0x2faf080>;

device_type = "serial";

status = "ok";

interrupt-parent = <0x1>;

};

serial@1c021000 {

reg = <0x0 0x1c021000 0x0 0x1000>;

interrupts = <0x0 0x4d 0x4>;

reg-shift = <0x2>;

compatible = "ns16550a";

clock-frequency = <0x2faf080>;

device_type = "serial";

status = "disabled";

interrupt-parent = <0x1>;

};

serial@1c022000 {

reg = <0x0 0x1c022000 0x0 0x1000>;

interrupts = <0x0 0x4e 0x4>;

reg-shift = <0x2>;

compatible = "ns16550a";

clock-frequency = <0x2faf080>;

device_type = "serial";

status = "disabled";

interrupt-parent = <0x1>;

};

serial@1c023000 {

reg = <0x0 0x1c023000 0x0 0x1000>;

interrupts = <0x0 0x4f 0x4>;

reg-shift = <0x2>;

compatible = "ns16550a";

clock-frequency = <0x2faf080>;

device_type = "serial";

status = "disabled";

interrupt-parent = <0x1>;

};

pcie@1f500000 {

reg = <0x0 0x1f500000 0x0 0x10000 0xa0 0xd0000000 0x0 0x200000>;

reg-names = "csr", "cfg";

compatible = "apm,xgene-storm-pcie", "apm,xgene-pcie";

dma-coherent;

device_type = "pci";

clocks = <0x9 0x0>;

#interrupt-cells = <0x1>;

dma-ranges = <0x42000000 0x80 0x0 0x80 0x0 0x0 0x80000000 0x42000000 0x0 0x0 0x0 0x0 0x80 0x0>;

ranges = <0x1000000 0x0 0x0 0xa0 0x10000000 0x0 0x10000 0x2000000 0x0 0x80000000 0xa1 0x80000000 0x0 0x80000000>;

status = "disabled";

#address-cells = <0x3>;

interrupt-map = <0x0 0x0 0x0 0x1 0x1 0x0 0xd4 0x1 0x0 0x0 0x0 0x2 0x1 0x0 0xd5 0x1 0x0 0x0 0x0 0x3 0x1 0x0 0xd6 0x1 0x0 0x0 0x0 0x4 0x1 0x0 0xd7 0x1>;

interrupt-map-mask = <0x0 0x0 0x0 0x7>;

#size-cells = <0x2>;

};

pcie@1f510000 {

reg = <0x0 0x1f510000 0x0 0x10000 0xc0 0xd0000000 0x0 0x200000>;

reg-names = "csr", "cfg";

compatible = "apm,xgene-storm-pcie", "apm,xgene-pcie";

dma-coherent;

device_type = "pci";

clocks = <0xa 0x0>;

#interrupt-cells = <0x1>;

dma-ranges = <0x42000000 0x80 0x0 0x80 0x0 0x0 0x80000000 0x42000000 0x0 0x0 0x0 0x0 0x80 0x0>;

ranges = <0x1000000 0x0 0x0 0xc0 0x10000000 0x0 0x10000 0x2000000 0x0 0x80000000 0xc1 0x80000000 0x0 0x80000000>;

status = "disabled";

#address-cells = <0x3>;

interrupt-map = <0x0 0x0 0x0 0x1 0x1 0x0 0xda 0x1 0x0 0x0 0x0 0x2 0x1 0x0 0xdb 0x1 0x0 0x0 0x0 0x3 0x1 0x0 0xdc 0x1 0x0 0x0 0x0 0x4 0x1 0x0 0xdd 0x1>;

interrupt-map-mask = <0x0 0x0 0x0 0x7>;

#size-cells = <0x2>;

};

pcie@1f2b0000 {

reg = <0x0 0x1f2b0000 0x0 0x10000 0xe0 0xd0000000 0x0 0x200000>;

reg-names = "csr", "cfg";

compatible = "apm,xgene-storm-pcie", "apm,xgene-pcie";

dma-coherent;

device_type = "pci";

clocks = <0x6 0x0>;

#interrupt-cells = <0x1>;

dma-ranges = <0x42000000 0x80 0x0 0x80 0x0 0x0 0x80000000 0x42000000 0x0 0x0 0x0 0x0 0x80 0x0>;

ranges = <0x1000000 0x0 0x0 0xe0 0x10000000 0x0 0x10000 0x2000000 0x0 0x80000000 0xe1 0x80000000 0x0 0x80000000>;

status = "ok";

#address-cells = <0x3>;

interrupt-map = <0x0 0x0 0x0 0x1 0x1 0x0 0xc2 0x1 0x0 0x0 0x0 0x2 0x1 0x0 0xc3 0x1 0x0 0x0 0x0 0x3 0x1 0x0 0xc4 0x1 0x0 0x0 0x0 0x4 0x1 0x0 0xc5 0x1>;

interrupt-map-mask = <0x0 0x0 0x0 0x7>;

#size-cells = <0x2>;

};

pcie@1f2c0000 {

reg = <0x0 0x1f2c0000 0x0 0x10000 0xd0 0xd0000000 0x0 0x200000>;

reg-names = "csr", "cfg";

compatible = "apm,xgene-storm-pcie", "apm,xgene-pcie";

dma-coherent;

device_type = "pci";

clocks = <0x7 0x0>;

#interrupt-cells = <0x1>;

dma-ranges = <0x42000000 0x80 0x0 0x80 0x0 0x0 0x80000000 0x42000000 0x0 0x0 0x0 0x0 0x80 0x0>;

ranges = <0x1000000 0x0 0x0 0xd0 0x10000000 0x0 0x10000 0x2000000 0x0 0x80000000 0xd1 0x80000000 0x0 0x80000000>;

status = "disabled";

#address-cells = <0x3>;

interrupt-map = <0x0 0x0 0x0 0x1 0x1 0x0 0xc8 0x1 0x0 0x0 0x0 0x2 0x1 0x0 0xc9 0x1 0x0 0x0 0x0 0x3 0x1 0x0 0xca 0x1 0x0 0x0 0x0 0x4 0x1 0x0 0xcb 0x1>;

interrupt-map-mask = <0x0 0x0 0x0 0x7>;

#size-cells = <0x2>;

};

pcie@1f2d0000 {

reg = <0x0 0x1f2d0000 0x0 0x10000 0x90 0xd0000000 0x0 0x200000>;

reg-names = "csr", "cfg";

compatible = "apm,xgene-storm-pcie", "apm,xgene-pcie";

dma-coherent;

device_type = "pci";

clocks = <0x8 0x0>;

#interrupt-cells = <0x1>;

dma-ranges = <0x42000000 0x80 0x0 0x80 0x0 0x0 0x80000000 0x42000000 0x0 0x0 0x0 0x0 0x80 0x0>;

ranges = <0x1000000 0x0 0x0 0x90 0x10000000 0x0 0x10000 0x2000000 0x0 0x80000000 0x91 0x80000000 0x0 0x80000000>;

status = "disabled";

#address-cells = <0x3>;

interrupt-map = <0x0 0x0 0x0 0x1 0x1 0x0 0xce 0x1 0x0 0x0 0x0 0x2 0x1 0x0 0xcf 0x1 0x0 0x0 0x0 0x3 0x1 0x0 0xd0 0x1 0x0 0x0 0x0 0x4 0x1 0x0 0xd1 0x1>;

interrupt-map-mask = <0x0 0x0 0x0 0x7>;

#size-cells = <0x2>;

};

ethernet_old@17020000 {

reg = <0x0 0x17020000 0x0 0x30 0x0 0x17020000 0x0 0x10000 0x0 0x17020000 0x0 0x20>;

interrupts = <0x0 0x38 0x4 0x0 0x39 0x4 0x0 0x3a 0x4>;

#clock-cells = <0x1>;

devid = <0x8>;

phyid = <0x3>;

compatible = "apm,xgene-enet-old";

local-mac-address = [00 01 73 02 0b 73];

slave-name = "RGMII";

dma-coherent;

phy-mode = "rgmii";

clocks = <0x15 0x0>;

status = "ok";

max-frame-size = <0x233a>;

};

dwusb@19000000 {

reg = <0x0 0x19000000 0x0 0x100000>;

interrupts = <0x0 0x89 0x4>;

compatible = "xhci-platform";

dma-coherent;

status = "ok";

};

phy@1f21a000 {

reg = <0x0 0x1f21a000 0x0 0x100>;

apm,tx-eye-tuning = <0x2 0xa 0xa 0x2 0xa 0xa>;

compatible = "apm,xgene-phy";

#phy-cells = <0x1>;

clocks = <0xb 0x0>;

apm,tx-boost-gain = <0x2 0x3 0x3 0x2 0x3 0x3>;

status = "ok";

phandle = <0xf>;

linux,phandle = <0xf>;

};

phy@1f22a000 {

reg = <0x0 0x1f22a000 0x0 0x100>;

apm,tx-eye-tuning = <0x1 0xa 0xa 0x2 0xa 0xa>;

compatible = "apm,xgene-phy";

#phy-cells = <0x1>;

apm,tx-boost-gain = <0x1e 0x1e 0x1e 0x1e 0x1e 0x1e>;

status = "ok";

phandle = <0x11>;

linux,phandle = <0x11>;

};

phy@1f23a000 {

reg = <0x0 0x1f23a000 0x0 0x100>;

apm,tx-eye-tuning = <0x2 0xa 0xa 0x2 0xa 0xa>;

compatible = "apm,xgene-phy";

#phy-cells = <0x1>;

apm,tx-boost-gain = <0x1f 0x1f 0x1f 0x1f 0x1f 0x1f>;

status = "ok";

phandle = <0x13>;

linux,phandle = <0x13>;

};

system-clk-controller@17000000 {

reg = <0x0 0x17000000 0x0 0x400>;

compatible = "apm,xgene-scu", "syscon";

phandle = <0x16>;

linux,phandle = <0x16>;

};

dwusb@19800000 {

reg = <0x0 0x19800000 0x0 0x100000>;

interrupts = <0x0 0x8a 0x4>;

compatible = "xhci-platform";

dma-coherent;

status = "ok";

};

clocks {

ranges;

#address-cells = <0x2>;

#size-cells = <0x2>;

pcie1clk@1f2cc000 {

reg = <0x0 0x1f2cc000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "pcie1clk";

status = "disabled";

phandle = <0x7>;

linux,phandle = <0x7>;

};

pcie2clk@1f2dc000 {

reg = <0x0 0x1f2dc000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "pcie2clk";

status = "disabled";

phandle = <0x8>;

linux,phandle = <0x8>;

};

xge0clk@1f61c000 {

reg = <0x0 0x1f61c000 0x0 0x1000>;

csr-mask = <0x3>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "xge0clk";

phandle = <0x19>;

linux,phandle = <0x19>;

};

sataphy1clk@1f21c000 {

reg = <0x0 0x1f21c000 0x0 0x1000>;

csr-offset = <0x4>;

csr-mask = <0x0>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

enable-offset = <0x0>;

enable-mask = <0x6>;

clocks = <0x4 0x0>;

clock-output-names = "sataphy1clk";

status = "disabled";

phandle = <0xb>;

linux,phandle = <0xb>;

};

socplldiv2 {

#clock-cells = <0x1>;

compatible = "fixed-factor-clock";

clock-names = "socplldiv2";

clocks = <0x3 0x0>;

clock-div = <0x2>;

clock-output-names = "socplldiv2";

phandle = <0x4>;

clock-mult = <0x1>;

linux,phandle = <0x4>;

};

rngpkaclk@17000000 {

reg = <0x0 0x17000000 0x0 0x2000>;

csr-offset = <0xc>;

csr-mask = <0x10>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

enable-offset = <0x10>;

enable-mask = <0x10>;

clocks = <0x4 0x0>;

clock-output-names = "rngpkaclk";

phandle = <0x1a>;

linux,phandle = <0x1a>;

};

sge0clk@1f21c000 {

reg = <0x0 0x1f21c000 0x0 0x1000>;

csr-mask = <0x3>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "sge0clk";

phandle = <0x18>;

linux,phandle = <0x18>;

};

pcie3clk@1f50c000 {

reg = <0x0 0x1f50c000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "pcie3clk";

status = "disabled";

phandle = <0x9>;

linux,phandle = <0x9>;

};

ethclk {

reg = <0x0 0x17000000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "div-reg";

divider-shift = <0x0>;

divider-width = <0x9>;

compatible = "apm,xgene-device-clock";

clock-names = "ethclk";

clocks = <0x4 0x0>;

clock-output-names = "ethclk";

divider-offset = <0x238>;

phandle = <0x5>;

linux,phandle = <0x5>;

};

pcppll@17000100 {

reg = <0x0 0x17000100 0x0 0x1000>;

type = <0x0>;

#clock-cells = <0x1>;

compatible = "apm,xgene-pcppll-clock";

clock-names = "pcppll";

clocks = <0x2 0x0>;

clock-output-names = "pcppll";

};

qmlclk {

reg = <0x0 0x1703c000 0x0 0x1000>;

csr-offset = <0x0>;

csr-mask = <0x3>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clock-names = "qmlclk";

enable-offset = <0x8>;

enable-mask = <0x3>;

clocks = <0x4 0x0>;

clock-output-names = "qmlclk";

status = "ok";

phandle = <0x14>;

linux,phandle = <0x14>;

};

refclk {

#clock-cells = <0x1>;

compatible = "fixed-clock";

clock-frequency = <0x5f5e100>;

clock-output-names = "refclk";

phandle = <0x2>;

linux,phandle = <0x2>;

};

pcie4clk@1f51c000 {

reg = <0x0 0x1f51c000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "pcie4clk";

status = "disabled";

phandle = <0xa>;

linux,phandle = <0xa>;

};

pcie0clk@1f2bc000 {

reg = <0x0 0x1f2bc000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clocks = <0x4 0x0>;

clock-output-names = "pcie0clk";

status = "ok";

phandle = <0x6>;

linux,phandle = <0x6>;

};

socpll@17000120 {

reg = <0x0 0x17000120 0x0 0x1000>;

type = <0x1>;

#clock-cells = <0x1>;

compatible = "apm,xgene-socpll-clock";

clock-names = "socpll";

clocks = <0x2 0x0>;

clock-output-names = "socpll";

phandle = <0x3>;

linux,phandle = <0x3>;

};

sata01clk@1f21c000 {

reg = <0x0 0x1f21c000 0x0 0x1000>;

csr-offset = <0x4>;

csr-mask = <0x5>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

enable-offset = <0x0>;

enable-mask = <0x39>;

clocks = <0x4 0x0>;

clock-output-names = "sata01clk";

phandle = <0xe>;

linux,phandle = <0xe>;

};

menetclk {

reg = <0x0 0x1702c000 0x0 0x1000>;

#clock-cells = <0x1>;

reg-names = "csr-reg";

compatible = "apm,xgene-device-clock";

clock-names = "menetclk";

clocks = <0x5 0x0>;

clock-output-names = "menetclk";

phandle = <0x15>;

linux,phandle = <0x15>;

};

};

rng@10520000 {

reg = <0x0 0x10520000 0x0 0x100>;

interrupts = <0x0 0x41 0x4>;

compatible = "apm,xgene-rng";

clocks = <0x1a 0x0>;

};

qmtm@17030000 {

reg = <0x0 0x17030000 0x0 0x10000 0x0 0x10000000 0x0 0x400000>;

interrupts = <0x0 0x40 0x4 0x0 0x3c 0x4>;

#clock-cells = <0x1>;

compatible = "apm,xgene-qmtm-lite";

slave-name = "CPU_QMTM3";

clocks = <0x14 0x0>;

status = "ok";

};

oldsata@1a000000 {

reg = <0x0 0x1a000000 0x0 0x1000 0x0 0x1f210000 0x0 0x10000>;

phys = <0xf 0x0>;

interrupts = <0x0 0x86 0x4>;

compatible = "apm,xgene-ahci-sgmii";

phy-names = "sata-6g";

clocks = <0xe 0x0>;

status = "disabled";

};

reboot@17000014 {

mask = <0x1>;

compatible = "syscon-reboot";

offset = <0x14>;

regmap = <0x16>;

};

oldsata@1a400000 {

reg = <0x0 0x1a400000 0x0 0x1000 0x0 0x1f220000 0x0 0x10000>;

phys = <0x11 0x0>;

interrupts = <0x0 0x87 0x4>;

compatible = "apm,xgene-ahci-sgmii";

phy-names = "sata-6g";

clocks = <0x10 0x0>;

status = "ok";

};

oldsata@1a800000 {

reg = <0x0 0x1a800000 0x0 0x1000 0x0 0x1f230000 0x0 0x10000>;

phys = <0x13 0x0>;

interrupts = <0x0 0x88 0x4>;

compatible = "apm,xgene-ahci-pcie";

phy-names = "sata-6g";

clocks = <0x12 0x0>;

status = "ok";

};

ethernet@17020000 {

reg = <0x0 0x17020000 0x0 0xd100 0x0 0x17030000 0x0 0xc300 0x0 0x10000000 0x0 0x200>;

interrupts = <0x0 0x3c 0x4>;

phy-handle = <0x17>;

reg-names = "enet_csr", "ring_csr", "ring_cmd";

compatible = "apm,xgene-enet";

local-mac-address = [00 01 73 02 0b 73];

dma-coherent;

clocks = <0x15 0x0>;

status = "ok";

phy-connection-type = "rgmii";

mdio {

compatible = "apm,xgene-mdio";

#address-cells = <0x1>;

#size-cells = <0x0>;

menetphy@3 {

reg = <0x3>;

compatible = "ethernet-phy-id001c.c915";

phandle = <0x17>;

linux,phandle = <0x17>;

};

};

};

ethernet@1f210000 {

reg = <0x0 0x1f210000 0x0 0xd100 0x0 0x1f200000 0x0 0xc300 0x0 0x1b000000 0x0 0x200>;

interrupts = <0x0 0xa0 0x4 0x0 0xa1 0x4>;

reg-names = "enet_csr", "ring_csr", "ring_cmd";

compatible = "apm,xgene1-sgenet";

local-mac-address = [00 00 00 00 00 00];

dma-coherent;

clocks = <0x18 0x0>;

status = "ok";

phy-connection-type = "sgmii";

};

ethernet@1f610000 {

reg = <0x0 0x1f610000 0x0 0xd100 0x0 0x1f600000 0x0 0xc300 0x0 0x18000000 0x0 0x200>;

interrupts = <0x0 0x60 0x4 0x0 0x61 0x4>;

reg-names = "enet_csr", "ring_csr", "ring_cmd";

compatible = "apm,xgene1-xgenet";

local-mac-address = [00 00 00 00 00 00];

dma-coherent;

clocks = <0x19 0x0>;

status = "ok";

phy-connection-type = "xgmii";

};

sata@1a000000 {

reg = <0x0 0x1a000000 0x0 0x1000 0x0 0x1f210000 0x0 0x1000 0x0 0x1f21d000 0x0 0x1000 0x0 0x1f21e000 0x0 0x1000 0x0 0x1f217000 0x0 0x1000>;

phys = <0xf 0x0>;

interrupts = <0x0 0x86 0x4>;

compatible = "apm,xgene-ahci";

dma-coherent;

phy-names = "sata-phy";

clocks = <0xe 0x0>;

status = "disabled";

};

sata@1a400000 {

reg = <0x0 0x1a400000 0x0 0x1000 0x0 0x1f220000 0x0 0x1000 0x0 0x1f22d000 0x0 0x1000 0x0 0x1f22e000 0x0 0x1000 0x0 0x1f227000 0x0 0x1000>;

interrupts = <0x0 0x87 0x4>;

compatible = "apm,xgene-ahci";

dma-coherent;

status = "ok";

};

};

cpus {

#address-cells = <0x2>;

#size-cells = <0x0>;

cpu@000 {

reg = <0x0 0x0>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0x8008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@001 {

reg = <0x0 0x1>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0x9008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@100 {

reg = <0x0 0x100>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xa008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@101 {

reg = <0x0 0x101>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xb008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@200 {

reg = <0x0 0x200>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xc008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@201 {

reg = <0x0 0x201>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xd008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@300 {

reg = <0x0 0x300>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xe008>;

enable-method = "spin-table";

device_type = "cpu";

};

cpu@301 {

reg = <0x0 0x301>;

compatible = "apm,potenza", "arm,armv8";

cpu-release-addr = <0x40 0xf008>;

enable-method = "spin-table";

device_type = "cpu";

};

};

timer {

interrupts = <0x1 0x0 0xff01 0x1 0xd 0xff01 0x1 0xe 0xff01 0x1 0xf 0xff01>;

compatible = "arm,armv8-timer";

clock-frequency = <0x2faf080>;

};

aliases {

ethernet0 = "/soc/ethernet@17020000";

};

interrupt-controller@78010000 {

reg = <0x0 0x78090000 0x0 0x10000 0x0 0x780a0000 0x0 0x20000 0x0 0x780c0000 0x0 0x10000 0x0 0x780e0000 0x0 0x20000>;

interrupts = <0x1 0x9 0xf04>;

compatible = "arm,cortex-a15-gic";

#interrupt-cells = <0x3>;

phandle = <0x1>;

interrupt-controller;

linux,phandle = <0x1>;

};

};使用方法如下:

sudo yum install -y dtc

dtc -I dts mustang.dts -O dtb -o /boot/mustang.dtb随后修改/boot/efi/EFI/centos/grub.cfg中修改第一个entry,添加

devicetree /mustang.dtb

并重启即可~

157

157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?