现代嵌入式计算系统将大量模块互连在一个外壳中,可能需要背板,连接这些系统的总线以多 Gbps 的数据速率运行。连接器、PCB 和接口总计会造成整个总线的损耗,系统级仿真需要考虑所有这些元素,以确保设计可行。

作为设计和验证流程的一部分,需要进行模拟以优化系统中的每个元素,并验证整个系统的信号完整性。遗憾的是,许多连接器的宽带 S 参数模型可能并非在每个数据速率下都可用或准确,因此可能需要进行一些 3D 模拟或测量。当您可以为通道生成准确的连接器和走线 S 参数时,您就可以在系统级准确模拟背板的行为。

背板总线、连接器拓扑和信号完整性

通过背板连接器进行单个物理互连的布线涉及差分对。单个差分对可能是涉及多个差分对的较大接口的一部分,网络/电信设备或数据中心的加速器就是这种情况。这里我们列出了高速数字系统中信号完整性问题的所有主要决定因素:

- S21/插入损耗:背板总线上的损耗包括电介质损耗

- S11/回波损耗:这里我们需要担心总线连接器的反射。阻抗不匹配的影响将根据路由拓扑(点对点、点对多点或多点)而有所不同。

- 串扰:显然,我们希望走线上的信号彼此充分隔离,并具有较低的串扰,但我们也希望连接器中引脚之间的串扰较低。在连接器中,可以通过将不同信号之间的引脚接地来提供隔离。

- 模式转换:这是指设计中共模和差模信号之间的转换。如果差模到共模的转换过多,这种转换可能会导致 EMC 故障。

- 接地:背板通常具有底盘接地和数字/模拟接地部分,它们在系统的特定点(通常是 PSU)连接在一起。请注意,对于布线,您可以使用底盘接地平面作为参考平面和层间隔离。

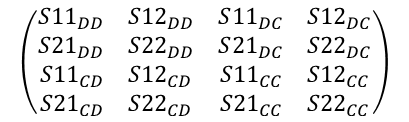

背板拓扑中的每个元素都有自己的一组 S 参数。基于点 1-3,我们可以得到一个 4x4 混合模式 S 参数矩阵,描述差分和共模激励和模式转换。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?