verilog小知识——对阻塞赋值和非阻塞赋值的理解

一. 两者的区别

1.硬件电路的区别

在时序逻辑中使用非阻塞赋值会生成触发器;在组合逻辑仲使用阻塞赋值会综合成一个连线。因此一般非阻塞赋值用于时序逻辑,而阻塞赋值用于组合逻辑。

2.语句执行顺序

非阻塞赋值语句是并行执行的,等到always块结束后,才完成赋值,而阻塞赋值是顺序执行的,下一条赋值语句要等到上一条赋值语句完成后才能赋值,并且阻塞赋值是立即完成的。

3.混用容易产生的错误

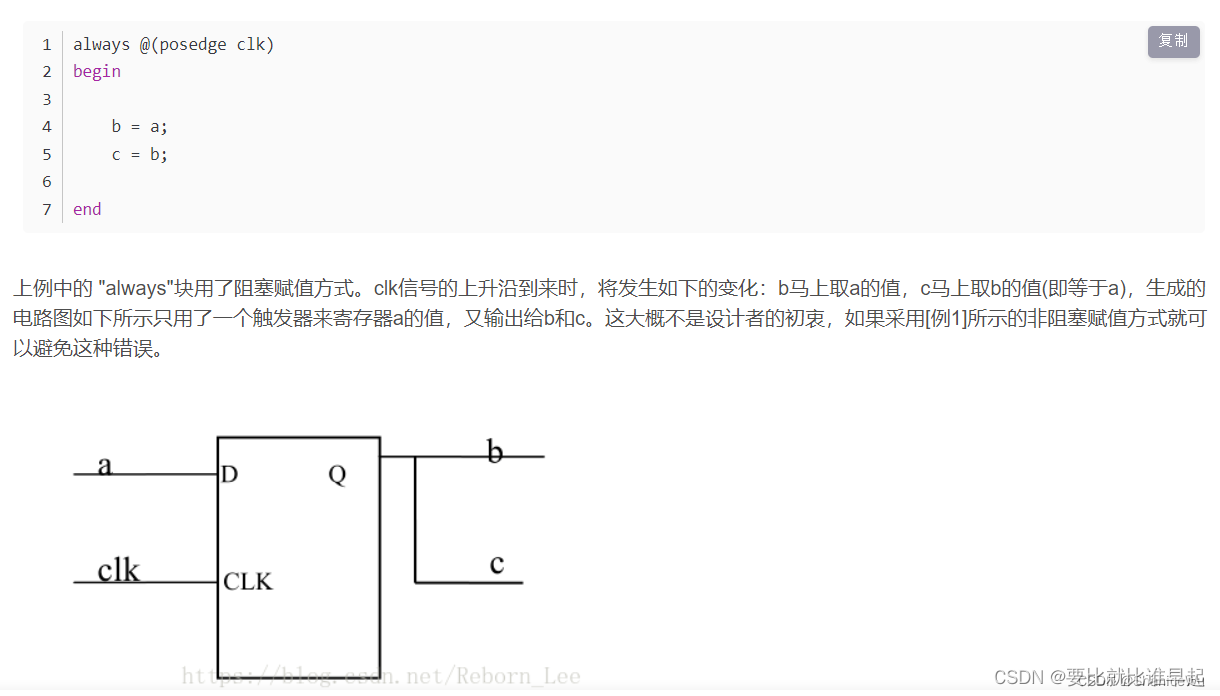

在组合逻辑中,使用非阻塞赋值,则和使用阻塞赋值没什么区别;但是在时序逻辑中,使用阻塞赋值进行赋值,除了第一个语句综合为触发器外,后续的语句均综合为一个连线,如下。

二. 举例说明区别

1.阻塞赋值

前面语句执行完,才可执行下一条语句;即:前面语句的执行(b=a)阻塞了后面语句的执行(c=b)。即:always块内,2条语句顺序执行。

always @(posedge iclk)

begin

b = a;

c = b;

end

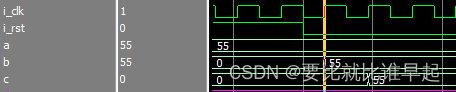

注意:a的值打一拍赋给b,b的值立刻赋给c。

2.非阻塞赋值

always块内,2条语句同时执行。即:前面语句的执行(b=a)不会阻塞后面语句的执行(c=b)。

always @(posedge iclk)

begin

b <= a;

c <= b;

end

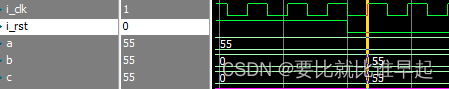

注意:因为生成寄存器,所以上升沿来的时候值才发生变化。所以第一个上升沿来的时候,a(55)的值赋给b,b(0)的值赋给c.

————————————————

原文作者侵删。本文无需三连和打赏,如确实有收获,请前往原作者博文进行感谢和支持。

参考原文博客:

1.https://blog.csdn.net/ShaniceWu/article/details/126013569?spm=1001.2014.3001.5502

2.https://blog.csdn.net/fzr_en/article/details/89552323

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?