关于Verilog 中阻塞与非阻塞赋值的几点理解

相信很多刚开始学习Verilog的童鞋对阻塞、非阻塞赋值理解得不是很明白,或者说是一头雾水。确实,Verilog中阻塞、非阻塞一直就是一个难点,很多具备很久开发经验的工程师仍是不得要领,在分析代码,看仿真时还是迷迷糊糊。我自己在学习语法的时候感觉理解了,但是在自己写代码,看仿真时仍然会出现不理解的波形,所以,就从头开始再看了遍语法。

阻塞赋值

阻塞赋值,顾名思义,即在一个always块中,后面的语句会受到前语句的影响,具体来说,在同一个always中,一条阻塞赋值语句如果没有执行结束,那么该语句后面的语句就不能被执行,即被“阻塞”。也就是说always块内的语句是一种顺序关系,这里和C语言很类似,比如,在C语言中,b= a;c=b;执行的时候就是先执行第一句b= a,然后执行下一句c=b,最后结果是a=c。同样,在时钟沿触发下,always块内,阻塞赋值是同样顺序执行,如下代码:

always@(posedge clk)

begin

b = a;

c = b;

end在时钟上升沿来的时候,a赋给b,执行完成后,b在赋给c,整个代码执行完时,a=c,效果与C语言同。

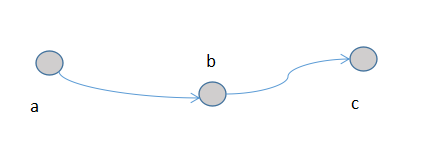

其过程下图所示

a的值先给b,然后才能给到c,这都是在一个时钟沿上完成的。

非阻塞赋值

在说非阻塞赋值之前,我们要先知道触发器的工作原理。即在时钟到来时,触发器会将输入端的数据打到输出端,这是受时钟节拍控制的。其实,非阻塞赋值更能体现出硬件电路工作时的实际情况。那么非阻塞赋值具体是怎么回事呢?

继续用上面的例子:

always@(posedge clk)

begin

b <= a;

c <= b;

end 在时钟上升沿到来时,该always块就不同于阻塞赋值的最终输出结果a=c,而是a传递到c需要间隔两个时钟,怎么理解呢?

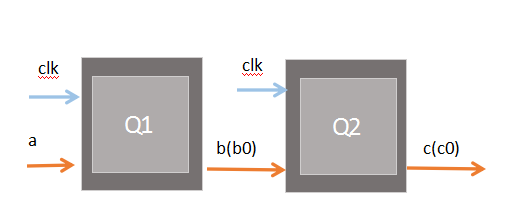

直接看图吧

非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将begin-end之间的所有赋值语句同时赋值到赋值语句的左边,注意:是begin—end之间的所有语句,一起执行,且一个时钟只执行一次。对于上面例子,在第一个时钟上升沿到来时,a把值赋给b,b把值赋给c,而此时b的值还没有被更新(即a的值还没有被触发器打给b),只是将b0(b前一次的值)打给c,所以第一个时钟结束后,b的当前值是a,c的当前值是b0(图中的c0)。第二个时钟上升沿到来时,才当前的b赋给c,由触发器输出,所以此时c的值才更新为a,故a和c相差2个时钟。

若a为 1,b为0,c为1的话,那么在非阻塞语句的always块中,一个时钟沿到来,由于他们之间是同时执行的,所以把a的1赋给了b,把b的0赋给了c,但是在阻塞语句里面,a的1先给了b,然后b把新赋值的1又给了c,那么c在一个时钟之后即变成了1。

通过上面的描述,阻塞、非阻塞赋值应该有了比较清晰的了解,但是什么时候用阻塞,什么时候用非阻塞赋值呢?在同一个always块中是否可以混合赋值呢?

对于第一个问题,夏宇闻老师书中直接给出了建议:

1、时序逻辑,使用“非阻塞赋值”。

2、 锁存器(latch)建模,使用“非阻塞赋值”。

3、组合逻辑,使用“阻塞赋值”

4、 当在同一个always块里面既为组合逻辑又为时序逻辑时,使用“非阻塞赋值”。

5、组合逻辑输出时,为消除毛刺会在输出端加一个触发器,即使用非阻塞赋值

对于第二个问题,不建议在同一个always块中使用混合赋值,在quartusII 中直接会报错,综合无法通过。同时同一个变量也不能在多个always块中被赋值,会报错。

507

507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?