7 Hardware design(HWD)

•

硬件设计包括硬件

架构设计(

HWD

)

和硬件

详细设计

。

硬件架构设计表示所有的硬件组件以及它们彼此的相互关系。

硬件详细设计是在电子电气原理图级别上, 表示构成硬件组件的元器件间的相互连接。

(为开发同时符合硬件安全要求及所有的非安全要求的唯一的硬件设计, 在此子阶段, 应在同一开发过程中处理安全和非安全性要求。)

•

硬件架构应实现硬件安全需求。

•

硬件架构将

硬件安全要求分配到对应的硬件要素,分配时应按照分配给它的所有要求中最高的

ASIL

等级来开发。

•

如果在硬件架构设计中对硬件安全要求应用了 安全分解,要注意按照安全分解的原则去实施 。

•

如果一个硬件要素是由

ASIL

等级低于要素

ASIL

等级或没有指定

ASIL

等级的子要素组成, 除非满足共存准则, 否则应按照最高的

ASIL

等级处理每个子要素。

•

对硬件安全要求和硬件架构设计要素之间的可追溯性, 应保持到硬件组件的最底层。

•

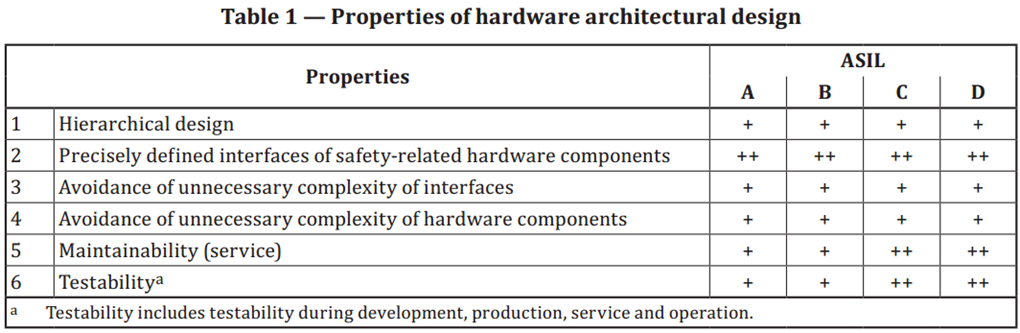

为避免系统性故障, 应通过使用表

1

中列出的原则, 使硬件架构设计具有下述特性:

a) 模块化; b) 适当的粒度水平; 及c) 简单性。

在硬件架构设计时, 应考虑安全相关硬件组件失效的非功能性原因, 如果适用, 可包括以下的影响因素: 温度、 振动、 水、 灰尘、 电磁干扰、 噪声因素、 或来自硬件架构的其他硬件组件或其所在环境的串扰。

ASIL C要求

1 分层设计

2 精确定义接口

3 避免不必要的接口复杂性

4 避免不必要的硬件组件复杂性

5 可维护性(服务)

6 可测试性

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?