文章目录

- 0x00寄存器,关于复位的寄存器

- 0x01寄存器,关于时钟开关的寄存器

- 0x02寄存器,ADC分频系数的寄存器

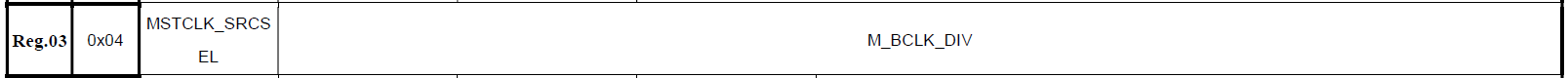

- 0x03寄存器,位时钟分频系数的寄存器

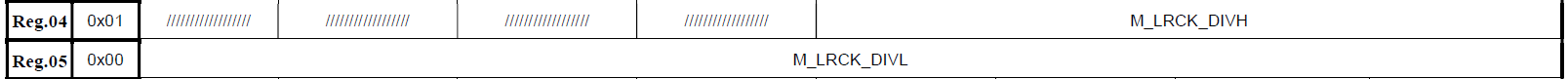

- 0x04/0x05寄存器,帧时钟分频系数的寄存器

- 0x06寄存器,与部分电路的供电有关

- 0x07寄存器,ADC的源时钟选择

- 0x08寄存器,工作模式寄存器

- 0x09/0x0a寄存器,一些关于内部时长控制寄存器

- 0x0b寄存器

- 0x0c寄存器

- 0x11寄存器,音频格式

- 0x12寄存器,输出引脚控制方面

- 0X13/0X14/0x15寄存器 静音控制

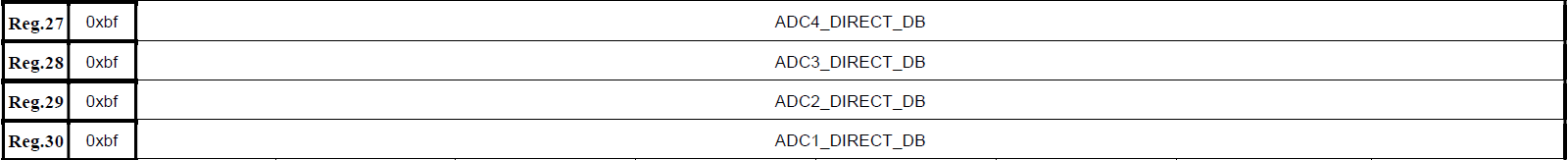

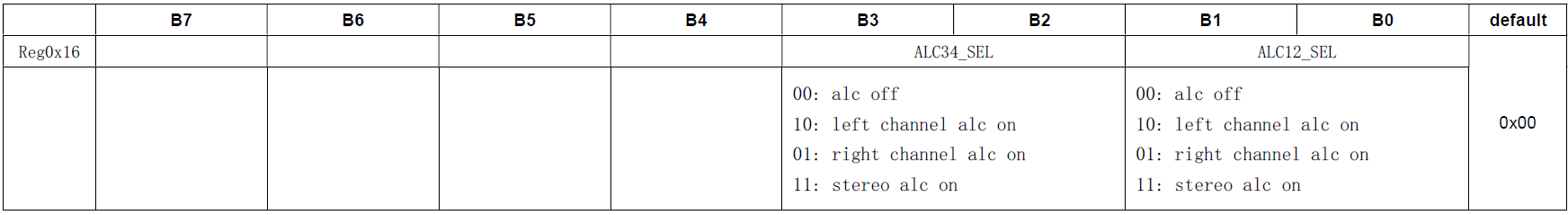

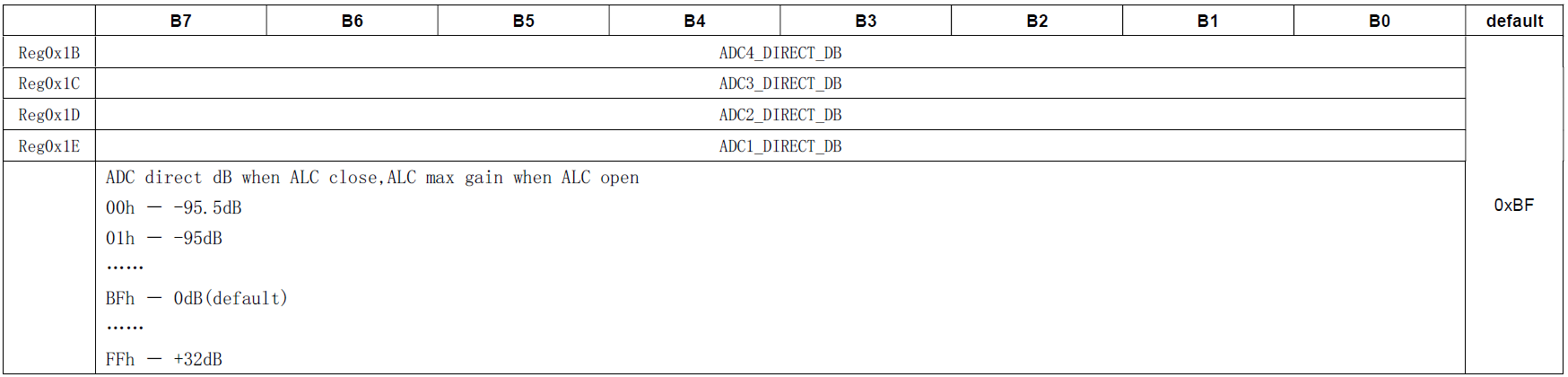

- 0X16/0x1b/0x1c/0x1d/0x1e寄存器

- 0X40寄存器

- 0X41/0X41寄存器

- 0X43/0X44/0X45/0X46寄存器 增益控制

对ES7210寄存器的理解

没找到详细点的寄存器手册,通过一个调试手册中部分寄存器描述和程序一起分析,把理解的寄存器内容记录下来。

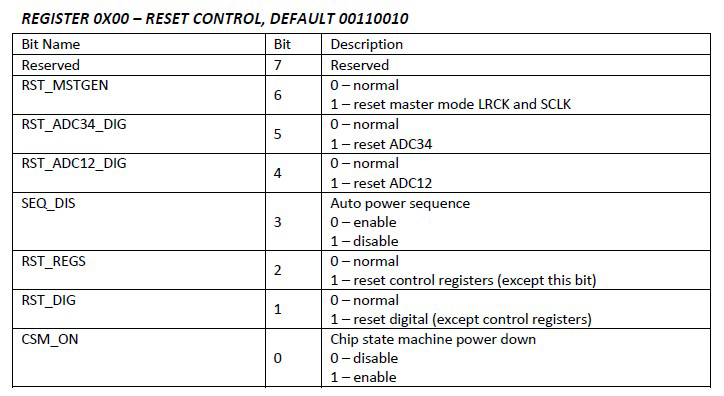

0x00寄存器,关于复位的寄存器

最高位没用,主控时钟电路复位,ACD34数字电路复位,ACD12数字电路复数,自动通道轮询(多麦克风用)允许位,寄存器复位,数字电路复位,时序电源开关,常见用法是先全1,再开相应电路,修改完时钟频率后,时钟电路要复位一次,另外,当MCLK由外部提供时,RST_MSTGEN保持为1,表示关闭。

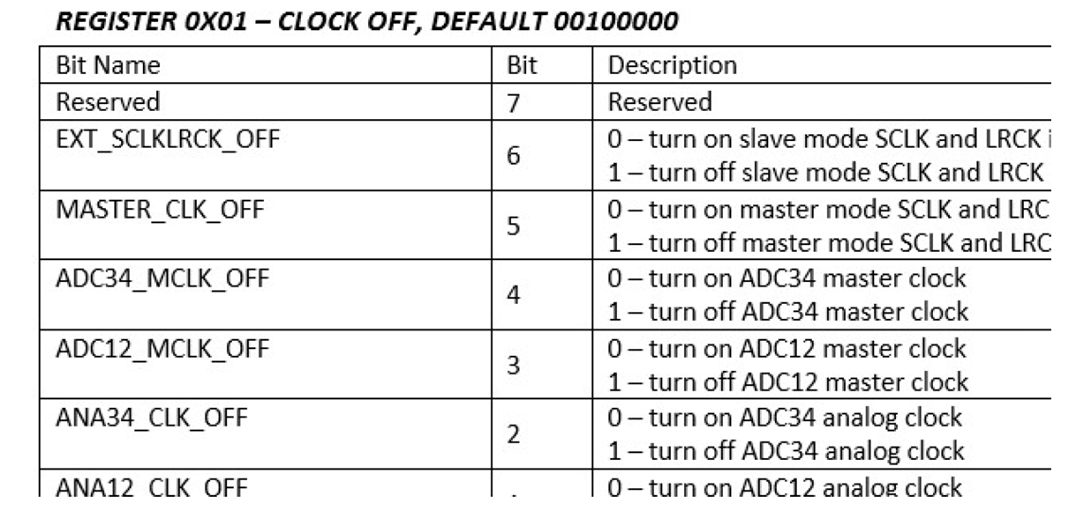

0x01寄存器,关于时钟开关的寄存器

这应该是关于时钟树向各ADC还有ANA的开关,0是打开,1是关闭,默认值是关闭了主控时钟,其他都打开了,关闭时钟电路可以减少功耗。

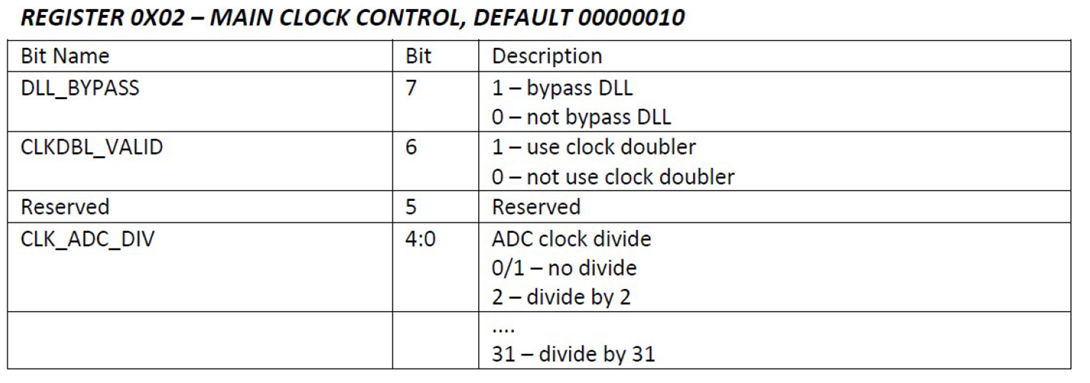

0x02寄存器,ADC分频系数的寄存器

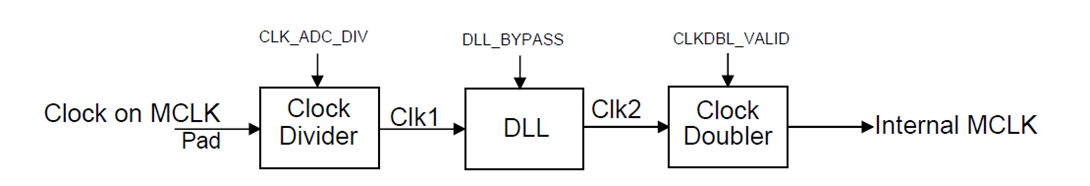

下图展示了主机模式中的内部时钟图。这里需要特别注意的是,ES7210 在从机模式下可以自动检测 LRCK 比率。

图中,时钟分频器的比率从 1 到 31。CLK1 的频率等于 MCLK 除以采样率,其中采样率就是时钟分频器的比率。

DLL 输出时钟的频率是 DLL 输入时钟的 4 倍。所以,如果 DLL_BYPASS 设置为 0,那么 CLK2 的频率应该是 CLK1 的 4 倍。如果 DLL_BYPASS 设置为 1,那么 CLK2 的频率应该等于 CLK1。

时钟倍频器的输出频率是其输入时钟的 2 倍。所以,如果 CLKDBL_VALID 设置为 1,那么内部 MCLK 的频率应该是 CLK2 的 2 倍。如果 CLKDBL_VALID 为 0,那么内部 MCLK 应该等于 CLK2。

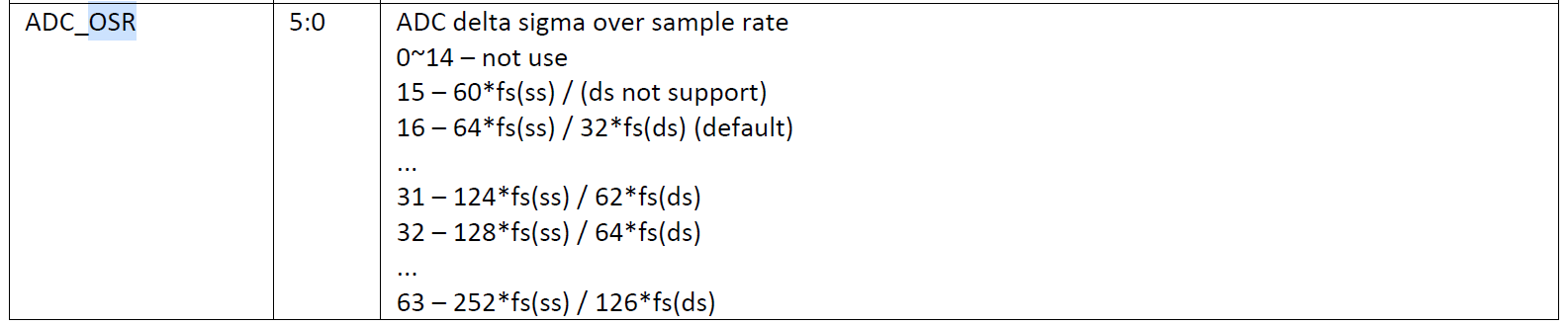

在单速模式下(0x08寄存器第2位的设置内容),当内部均衡器启用时,内部 MCLK 与 LRCK 之间的比率必须高于 512;而当内部均衡器禁用时,该比率必须高于 480。在单速模式下,为了使抗混叠效果最佳,内部 MCLK 应为 16×ADC_OSR。

在双速模式下(0x08寄存器第2位的设置内容),内部 MCLK 与 LRCK 之间的比率必须高于 256。ES7210 在双速模式下不支持均衡器。在双速模式下,为了使抗混叠效果最佳,内部 MCLK 应为 8×ADC_OSR。

以下是一些时钟分频器、DLL 和时钟倍频器设置的示例。

示例 1:CPU/SOC 向 ES7210 提供 12.288MHz 的 MCLK 和 48KHz 的 LRCK,因此外部 MCLK/LRCK 比率为 256。在这种时钟条件下,时钟分频器比率应为 1,并且应绕过 DLL。但应启用时钟倍频器以获得 24.576MHz 的内部时钟。现在内部 ADC 时钟为 24.576MHz,等于 512×LRCK。

示例 2:CPU/SOC 向 ES7210 提供 18.432MHz 的 MCLK 和 48KHz 的 LRCK,因此 MCLK/LRCK 比率为 384。在这种时钟条件下,时钟分频器比率应为 3,以获得 6.144MHz 的时钟。应启用 DLL 以获得 24.576MHz(4×6.144MHz)的时钟。应禁用时钟倍频器。现在内部 ADC 时钟为 24.576MHz,等于 512×LRCK。

0x03寄存器,位时钟分频系数的寄存器

设置位时钟分频系数,在ES8311的分析中详细说过这块原理。

在从模式下,LRCK引脚是输入引脚,由外部主机控制器向ES7210发送适当的LRCK时钟。ES7210可以自动检测MCLK/LRCK比率。

在主模式下,LRCK是输出引脚。ES7210产生适当的LRCK时钟输出。LRCK是通过LRCK时钟分频器从MCLK时钟派生出来的。在这里,MCLK时钟是由MSTCLK_SRCSEL(寄存器0x03的第7位)控制的多路复用器的输出。

0x04/0x05寄存器,帧时钟分频系数的寄存器

帧时钟和采样时钟频率一致,都是比较低的频率,需要的分频系数大,因此用了12位来存放。

0x06寄存器,与部分电路的供电有关

DLL_POWER_DOWN是锁相环电路的电源开关,TDMIN_PDF_OFF是级联时外部TDM输入的PDN模块电源开关,PUPDN_OFF上拉电阻开关。默认都是关的,不级联多个ES7210时用不到。

0x07寄存器,ADC的源时钟选择

adc的转换也需要时钟驱动,这个源配置需要倍频,具体内容不详,程序中在查表时找出对应值。下图是ES8311的,可借鉴

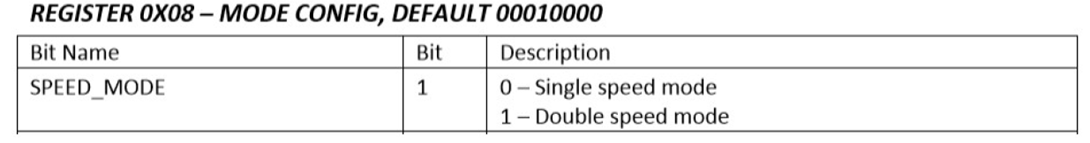

0x08寄存器,工作模式寄存器

MS_MODE位:主从模式选择位,0是从模式,这里注意,当使用主模式时,通过设置I2S总线时,也会发现,硬件上MCLK/LRCK/BCLK信号都是主控提供给ES7210的,所以芯片会自动检测 MCLK 与 LRCK 的比率(无需手动配置分频),也就是说作为I2S总线上的从机时,0x02/0x03/0x04/0x05寄存器都不用设置。

SPEED_MODE位:支持三种方式:

主模式工作时分单速模式(Single Speed Mode)和双速模式(Double Speed Mode)。

单速模式(Single Speed Mode):

LRCK(帧时钟)频率通常支持 8kHz 至 48kHz。

适用于标准音频采样率(如 44.1kHz、48kHz)。

双速模式(Double Speed Mode):

LRCK 频率通常支持 64kHz 至 96kHz。

适用于高采样率音频(如 88.2kHz、96kHz)。

自动模式:

从模式(Slave Mode)下,ES7210 会自动检测当前速率模式(单速/双速)。

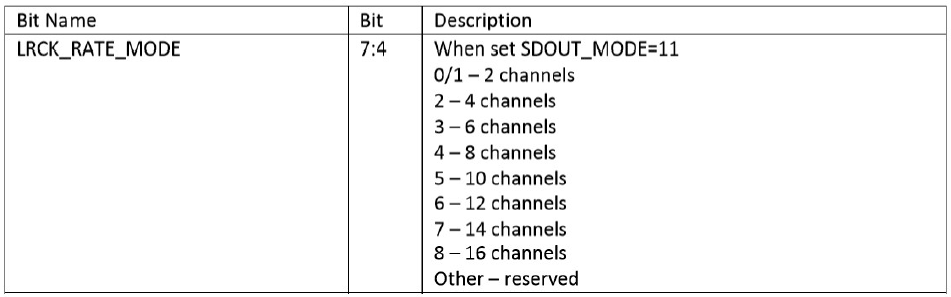

LRCK_RATE_MODE位:占4位,默认值是1,

在TDM(时分复用)模式下,"channels"参数代表系统中使用的麦克风总数。ES7210的LRCK_RATE_MODE设置与麦克风数量直接相关,具体配置规则如下:

- 通道数配置原则:

- 当系统使用2个麦克风时,LRCK_RATE_MODE可设为0或1

- 使用16个麦克风时,必须设为8

- 通用公式:LRCK_RATE_MODE = 总麦克风数/2(取整)

注:实际配置时需确保:

- 所有级联设备的LRCK_RATE_MODE一致

- BCLK频率满足:BCLK = 2×时隙数×比特深度×FS

- 时序余量保留至少10%

BCLK_INV_MODE位:在正常的I2S/LJ/DSP格式中,数据位总是在BCLK(SCLK)的下降沿传输,并且主机控制器在BCLK(SCLK)的上升沿接收数据位。但有些主机控制器可能需要在BCLK(SCLK)的下降沿接收数据位。寄存器0x08的第3位(SCLK_INV_MODE)用于反转BCLK边缘以传输/接收数据位。

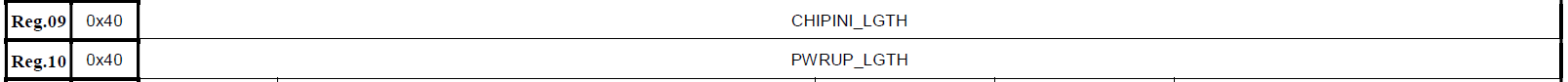

0x09/0x0a寄存器,一些关于内部时长控制寄存器

CHIPINI_LGTH其中一个功能是在LRCK为短脉冲时设置高电平时长的。其他情况下的用途没搞明白。

PWRUP_LGTH应该是配合时序电源开关,控制上电时长的。

两个寄存器值看大部分程序中都是0X30。跟着用。

0x0b寄存器

看名称好理解,清除内部RAM采样数据,两个静音开关。

FORCE_CSM默认是同步时钟,0为自动。

CSM_STATE是同步状态,可能是以下的情况

| 状态值 | 含义 | 触发场景 |

|---|---|---|

00 | 未锁定(Unlocked) | 上电初始化、时钟中断或MCLK不稳定时 |

01 | 同步中(Calibrating) | 时钟切换或强制同步(FORCE_CSM)中 |

10 | 已锁定(Locked) | 时钟稳定,正常工作时 |

11 | 错误(Error) | 检测到时钟冲突或超范围抖动 |

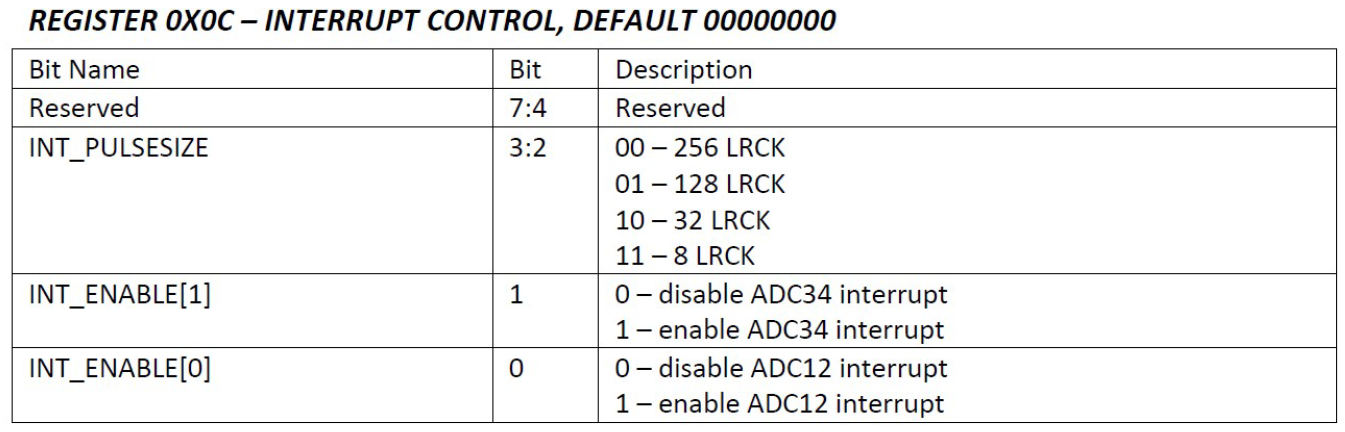

0x0c寄存器

ES7210 具有可中断输出的静音控制功能。当中断控制位 INT_ENABLE 设置为 1 时,ADC 可输出低电平脉冲,脉冲宽度由 INT_PULSESIZE 控制。

-

静音控制(Mute Control)

- ES7210 支持通过硬件或寄存器配置(0x13/0x14/0x15)实现静音(Mute),此时 ADC 会停止正常数据输出。

- 该静音功能可以被中断(Interrupt),即允许在特定条件下恢复输出。

-

中断控制(INT_ENABLE)

- 当寄存器位

INT_ENABLE = 1时,允许 ADC 在特定事件(如信号恢复)时输出一个低电平脉冲,用于通知外部设备(如 DSP 或 MCU)。 - 该脉冲可用于同步或唤醒系统,例如在从静音状态恢复时触发外部设备处理数据。

- 当寄存器位

-

脉冲宽度控制(INT_PULSESIZE)

- 脉冲的持续时间(低电平时间)由

INT_PULSESIZE寄存器的值决定,用户可配置(如几个时钟周期或固定时间长度)。 - 例如:

INT_PULSESIZE = 0x10表示32个 lrck 周期的低电平脉冲。- 具体时间取决于芯片的时钟配置。

- 脉冲的持续时间(低电平时间)由

典型应用场景:

- 音频信号异常检测:当输入信号异常(如麦克风断开)时,ES7210 可静音并发送中断脉冲,通知主控芯片处理。

- 低功耗模式唤醒:在省电模式下,ADC 可静音,当检测到有效信号时,通过中断脉冲唤醒系统。

- 硬件同步:多设备系统中,可用中断脉冲对齐数据采集时序。

关联寄存器(示例)

| 寄存器位 | 功能 | 备注 |

|---|---|---|

INT_ENABLE | 中断使能 | 1=允许输出中断脉冲,0=禁用 |

INT_PULSESIZE | 脉冲宽度 | 单位可能是 BCLK 周期或固定时间步进 |

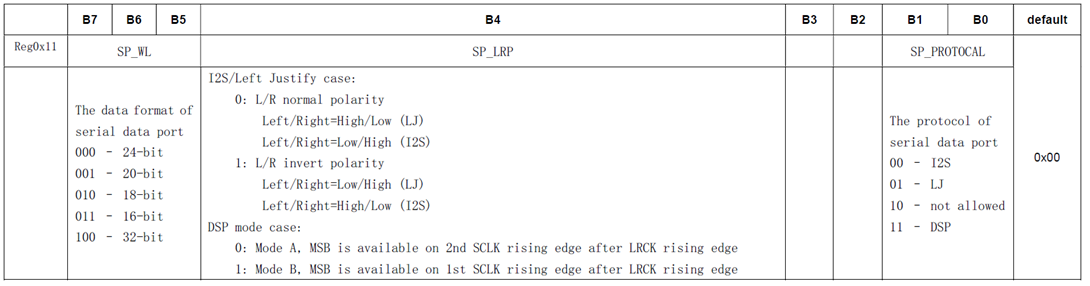

0x11寄存器,音频格式

这块需要了解I2S背景知识,后面单独来列。

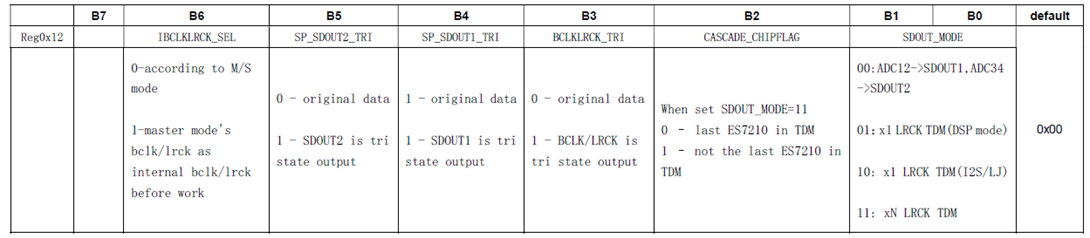

0x12寄存器,输出引脚控制方面

BIT6

0选项:表示设备将根据主/从模式(Master/Slave mode)的设置来决定时钟源。在主模式下,设备生成时钟信号;在从模式下,设备接收外部时钟信号。

1选项:表示强制使用主模式(master mode),此时设备内部生成的位时钟(BCLK)和左右声道时钟(LRCK)将在设备开始工作前就作为基准时钟信号

BIT5

0 - SDOUT2引脚数据输出

1 - SDOUT2引脚高阻状态

BIT4

0 - SDOUT1引脚数据输出

1 - SDOUT1引脚高阻状态

BIT3

0 - LRCK和SCLK引脚正常信号传输

1 - LRCK和SCLK引脚高阻状态

BIT2 这是级联时用的

当设置 SDOUT_MODE=11 时:

0 – 表示该 ES7210 是 TDM 链中的最后一个设备

1 – 表示该 ES7210 不是 TDM 链中的最后一个设备

BIT1/BIT0 TDM工作模式的设置

| 模式 | 功能 | 适用场景 |

|---|---|---|

| 00 | ADC12→SDOUT1, ADC34→SDOUT2 | 双数据线独立输出(如双麦克风) |

| 01 | 单设备 LRCK TDM(DSP 模式) | 专用 DSP 芯片对接 |

| 10 | 单设备 LRCK TDM(I2S/LJ 格式) | 标准 I2S 设备兼容 |

| 11 | 多设备 LRCK TDM(多时隙) | 多通道音频(如麦克风阵列) |

工作模式要配合0x11寄存器一起用,待总结I2S模式一起再说下该处寄存器配置内容。

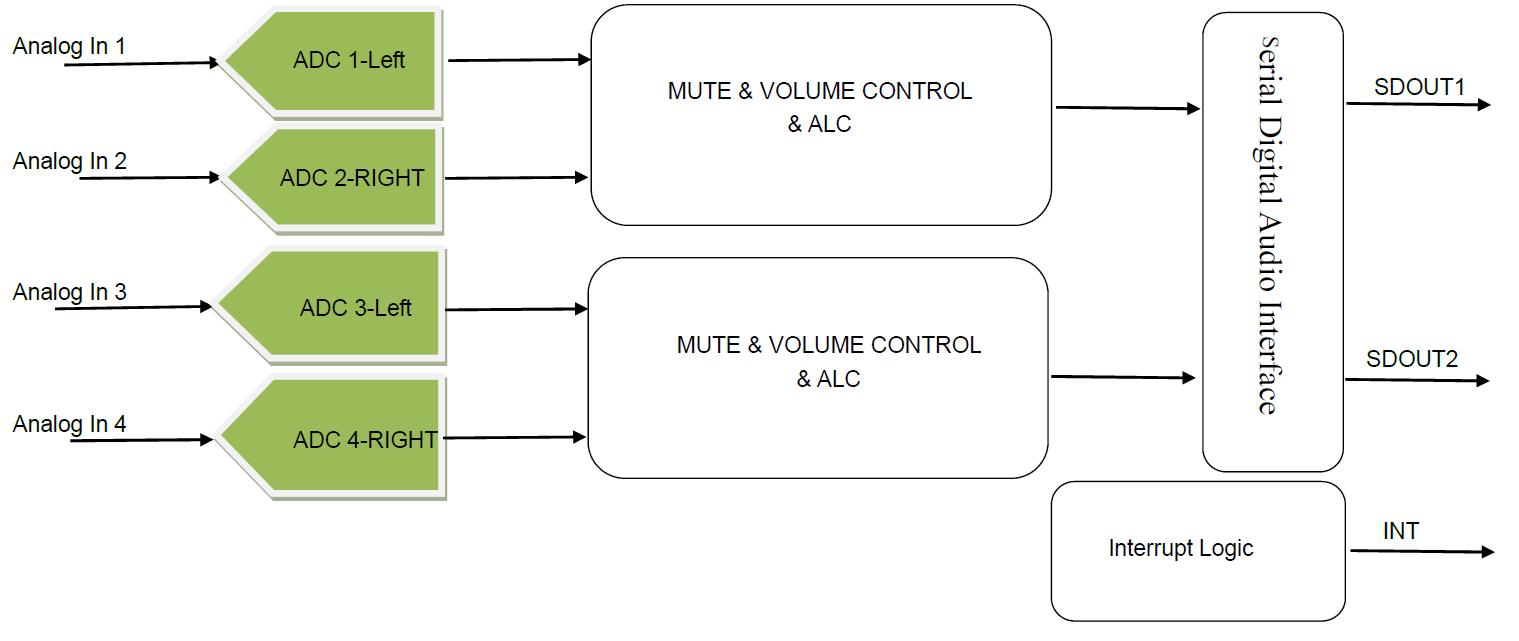

这里,贴上信号路径图,便于理解信事情输出及后面的调音

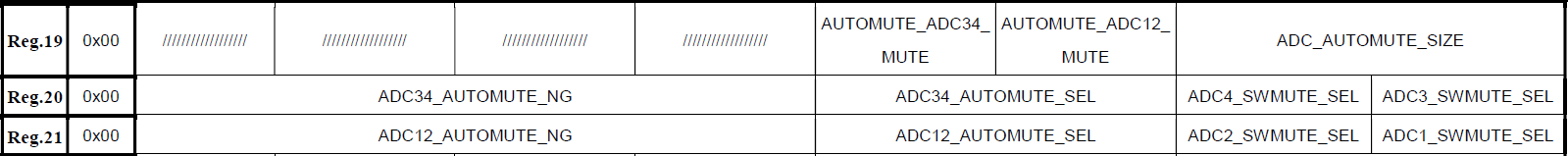

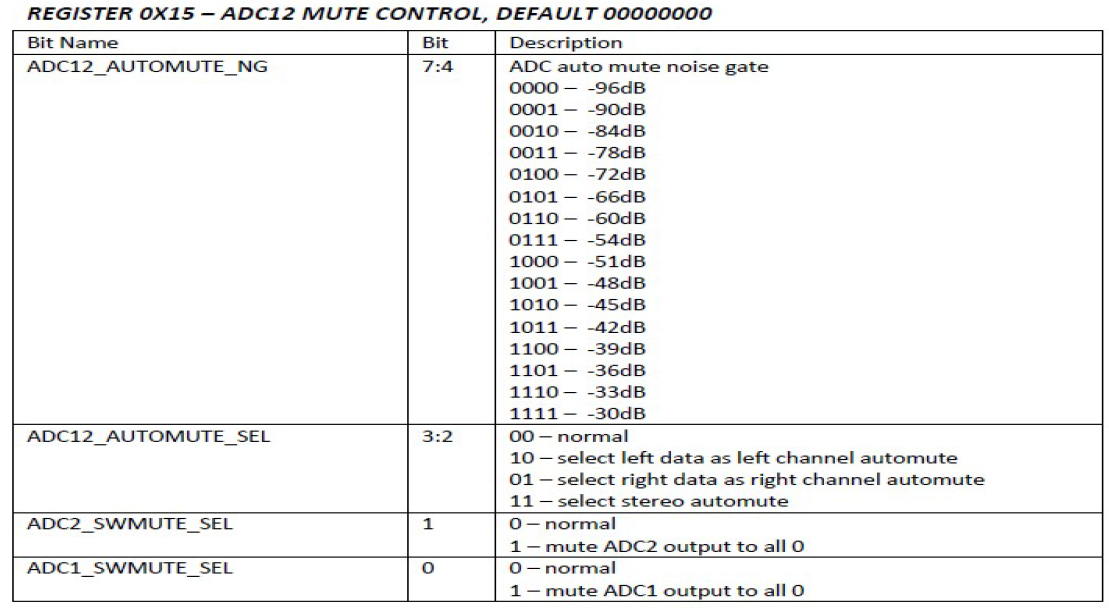

0X13/0X14/0x15寄存器 静音控制

ES7210 具有静音控制功能,可静音 ADC 输出。当静音控制设置为 1 时,ADC 将始终输出全 0 或全 1。

此外,ES7210 还支持自动静音功能。如果启用自动静音,ES7210 会自动检测输入信号电平。若输入电平在较长时间内低于设定阈值,ADC 将进入静音状态。用户可自定义阈值电平和持续时间。

注:全0输出符合IEC60958静音标准,全1输出可用于特殊测试场景。持续时间参数可有效防止瞬时噪声误触发静音功能。

关联前面0x0C寄存器,静音时与中断可以配合使用。

0X16/0x1b/0x1c/0x1d/0x1e寄存器

在具有录音功能的应用中,自动电平控制(ALC)通常用于保持录音信号电平恒定。例如在进行语音录制时,由于用户说话音量大小不同或麦克风与嘴部距离变化,会导致信号强度差异很大,最终造成回放时录音信号音量忽大忽小,影响听感。

ALC的核心功能是通过动态调节可编程增益放大器(PGA)的增益值,使ADC输出端的信号电平保持稳定。其工作原理是:

- 实时监测输入信号强度

- 当检测到信号过强时自动降低PGA增益

- 当信号过弱时则提高增益

- 通过这种闭环调节确保输出电平恒定

在音频录制系统中,针对不同音源(如人声、古典音乐、流行音乐等)优化自动电平控制(ALC)参数是一个复杂的过程。ES7210芯片提供了基础推荐配置作为调试起点,但由于实际效果存在主观性且应用场景各异,用户可能需要根据具体需求进行参数微调。在大多数情况下,这些预设配置已能提供令人满意的解决方案。

该芯片配备两路独立的ALC控制器:

- ALC12_SEL:控制通道1&2的ALC功能

- ALC34_SEL:控制通道3&4的ALC功能

每路ALC控制器支持四种工作模式:

- 模式0:ALC功能关闭

- 模式1:仅左声道启用ALC(适用于单声道左输入)

- 模式2:仅右声道启用ALC(适用于单声道右输入)

- 模式3:立体声ALC(双声道同步增益控制)

技术说明:

- 模式选择通过寄存器配置实现,需与硬件电路设计匹配

- 立体声模式能保持双声道增益一致性,避免声像偏移

- 单声道模式可降低处理功耗,适用于非对称输入场景

- 推荐针对不同音源采用以下配置:

- 语音采集:使用较快响应时间的立体声模式

- 音乐录制:采用较慢调节速度的单声道模式

- 乐器拾音:建议关闭ALC以保留动态范围

注:实际应用中需通过听感测试和示波器观测来验证ALC效果,特别注意避免产生可闻的增益调节噪声。

当启用自动电平控制(ALC)功能时,ES7210将自动检测输入信号电平并动态调整数字增益。有多项可编程参数供用户灵活配置:

核心可调参数包括:

- 阈值电平(Threshold Level) - 设定ALC开始工作的触发门限

- 持续时间(Duration Time) - 确定信号检测时间窗口

- 目标电平(Target Level) - 设置ADC输出的理想幅度值

- 增益调节步进(Gain Step) - 控制每次增益变化的幅度

- 攻击/释放时间(Attack/Release Time) - 分别配置增益提升和降低的响应速度

工作特性:

- 采用实时采样分析技术,持续监控输入信号RMS值

- 基于数字信号处理算法实现平滑增益调节

- 支持0.5dB精度的增益控制

- 可防止过调幅(Over-modulation)和噪声放大

典型配置建议:

- 语音应用:

- 目标电平:-12dBFS

- 攻击时间:10ms

- 释放时间:500ms

- 音乐录制:

- 目标电平:-6dBFS

- 攻击时间:50ms

- 释放时间:1s

建议配合示波器观察实际波形进行参数优化。芯片内置防振荡算法,可避免增益调节过程中的信号失真。

0X40寄存器

内部模拟电路的电压开关。

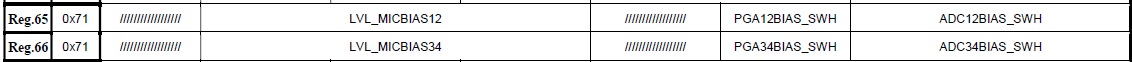

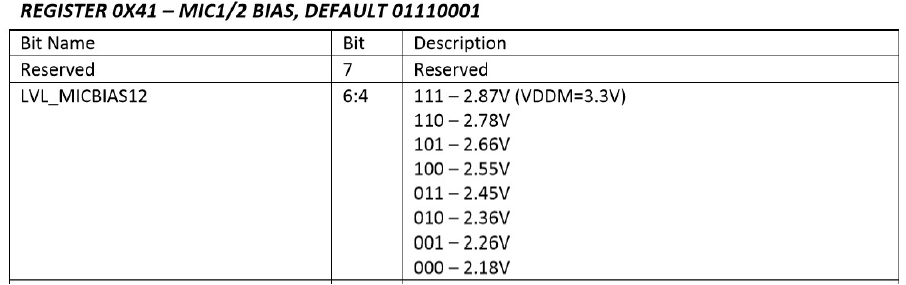

0X41/0X41寄存器

ES7210芯片提供两路独立的麦克风偏置电压:

使用顺序:

- 开启:先设置电压值,再使能PDN位

- 关闭:先静音ADC,再关断MICBIAS

硬件配置特性:

- 双路MICBIAS输出:

- MICBIAS12:支持通道1&2的麦克风供电

- MICBIAS34:支持通道3&4的麦克风供电

供电能力说明:

- 每路MICBIAS可同时驱动2个驻极体(ECM)或MEMS麦克风

- 典型负载能力:2mA/路(满足大多数数字麦克风需求)

寄存器控制功能:

-

电压等级设置:

- 通过专用寄存器位可编程调整输出电压

- 典型可选范围:1.8V/2.0V/2.2V/2.4V(具体以规格书为准)

-

使能控制:

- 独立开关MICBIAS12/MICBIAS34输出

- 支持低功耗模式下的偏置电压关闭

应用设计指南:

-

MEMS麦克风连接:

- 建议使用2.0V供电电压

- 需在MICBIAS引脚配置100nF去耦电容

-

驻极体麦克风连接:

- 推荐2.2V供电电压

- 需串联2.2kΩ偏置电阻

寄存器配置示例:

| 寄存器地址 | 控制位 | 功能描述 |

|---|---|---|

| 0x41/0x42 | BIT[0] | MICBIAS使能(1=开启) |

| 0x41/0x42 | BIT[1] | PGABIAS使能(1=开启) |

| 0x41/0x42 | BIT[4:6] | MICBIAS12电压选择 |

注:实际使用时需注意:

- 电压选择需匹配麦克风规格要求

- 上电顺序建议先开启MICBIAS后启动ADC

- PCB布局时应缩短MICBIAS走线长度以降低噪声

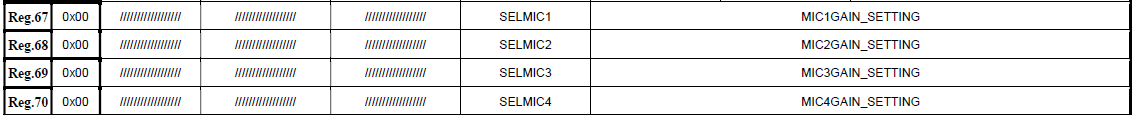

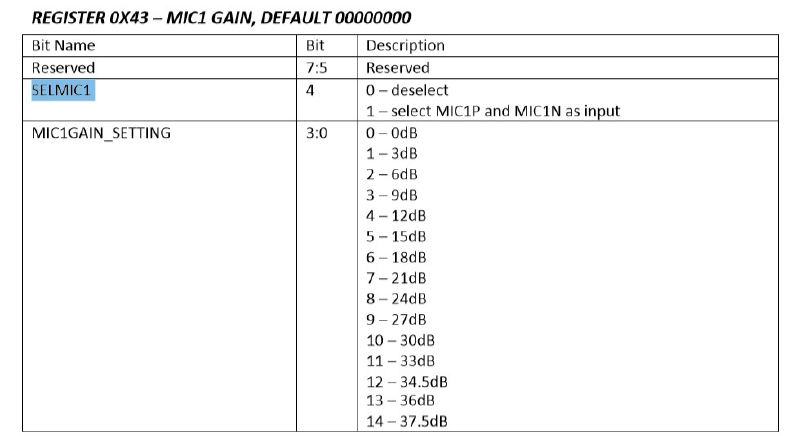

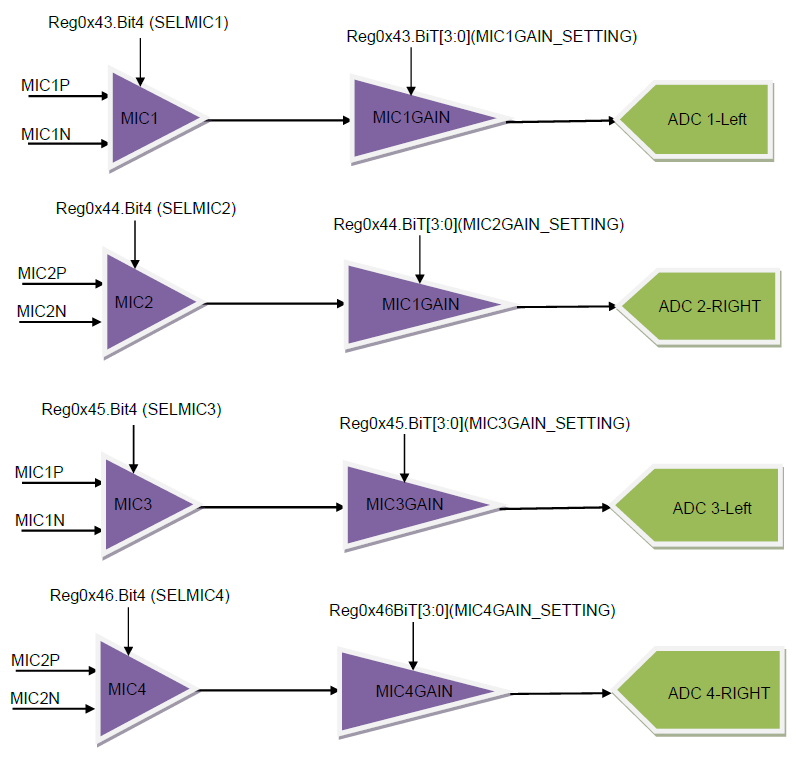

0X43/0X44/0X45/0X46寄存器 增益控制

四个寄存器对应四个输入,寄存器位意义都一样。

ES7210芯片集成四组立体声差分模拟输入接口,具体配置如下:

硬件接口定义:

- Mic1P-Mic1N:第1组差分麦克风输入

- Mic2P-Mic2N:第2组差分麦克风输入

- Mic3P-Mic3N:第3组差分麦克风输入

- Mic4P-Mic4N:第4组差分麦克风输入

核心功能模块:

- 每组输入通道配备独立可编程增益放大器(PGA)

- 增益调节范围:0dB至+37.5dB(步进0.5dB)

- 采用差分输入结构,有效抑制共模噪声

寄存器控制逻辑:

-

输入使能控制(寄存器0x43~0x46的bit4):

- SELMICX = 1:启用对应差分输入通道

- SELMICX = 0:禁用该通道

-

PGA增益设置(寄存器0x43~0x46的bit[3:0]):

- 4位二进制编码对应31级增益调节

- 增益计算公式:实际增益(dB) = 寄存器值 × 0.5

增益对照表示例:

| 寄存器值 | 增益(dB) | 适用场景 |

|---|---|---|

| 0000 | 0.0 | 线路电平输入 |

| 0010 | 1.0 | 高灵敏度麦克风 |

| 0111 | 3.5 | 中等距离拾音 |

| 1111 | 37.5 | 远距离弱信号采集 |

应用注意事项:

- 启用差分输入时需保持P/N信号线对称布局

- 高增益设置时建议启用ALC功能防止信号削波

- 各通道增益可独立设置,实现多麦克风电平匹配

- 寄存器写入后需3个BCLK周期生效

4827

4827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?