文章目录

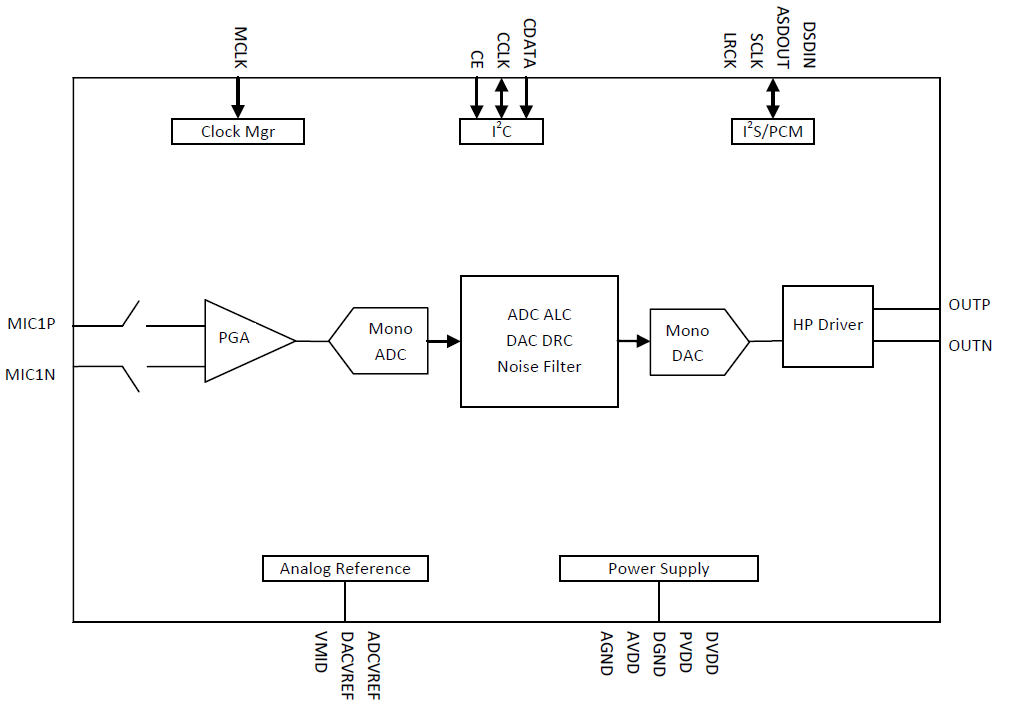

以下分析基于立创实战派S3的开发板进行分析,因为只用了ES8311的DAC部分,没用到的寄存器就不详细分析了。但初步掌握了这些,对于其他寄存器的理解也不难了,回头再看ES7211,即便没有寄存器的说明,大体上也能猜出内容。

第一步 设置电源

write_reg(ES8311_REG00, 0x1F) // 关闭主电源,设为从机模式,允许上电时序,数字电路复位,内部主控复位,关闭ADC供电,关闭DAC供电

Delay(20MS);

write_reg(ES8311_REG00, 0x02) // 保持主电源关闭,从机模式,允许上电时序,数字电路工作,内部主控工作,打开ADC供电,DAC保持关闭

write_reg(ES8311_REG00, 0x82) // 打开主电源

write_reg(ES8311_REG01, 0x35) // 允许 MCLK、BCLK、DAC时钟

第二步 设置硬件引脚

需要根据硬件对ES8311_REG01的第7位、第6位和ES8311_REG06第5位进行设置,本次硬件电路均可以用默认值,不需要设置也不影响

第三步 设置时钟

开始设置分频值

调用查表函数获得相应值,然后给0x02/0x03/0x04/0x05/0x06/0x07/0x08寄存器写值。

这里重点说一下MCLK的计算问题,分频对于ADC或是DAC电路是主要的设置内容。

先说背景知识.

1.MCLK的选择

因为涉及音频采样后的信号还需要进行处理,就需要更高的带宽,根据过采样率的原理及公式,主时钟MCLK需要选择更高的频率,以驱动电路进行过采样率处理。

过采样增加的位数为4的指数,例如,过采样率 = (4^4) x 采样率,大概意思就是可以比实际采样位深高4位,获得20位的位深精度。

因此,采样率48000Hz,位深16位(达到专业音频入门标准),要想适用过采样率处理,MCLK至少要达到采样率的256倍。

即:MCLK = 256 x BCLK = 256 x 48000 = 12288000Hz

2.BCLK的选择

根据ADC的转换原理,如果位深是16位的,每秒的采样次数是采样率,一次采样就有16位数据要进入数据总线传输,也就是位宽是16,同时两个声道,数据量就是位宽 X 2 =36位

所以位时钟信号的频率(BCLK) = 采样率 X 位宽 X 2 = 48000 X 16 X 2 = 1536000Hz。

数字电路中,都是一个主频率,然后分成各种各样的频率来用。MCLK分频过程中,如何把MCLK分频到可以同步数据位的BCLK,就需要增加了一个叫DIV的分频系数,另外,显然BCLK又要再分频,得到采样率的频率,供DAC或ACD电路做转换时用,也会产生分频系数。还有个叫LRCK的信号,好在这个信号和采样率频率相同,不用单独再分频了。

上面例子中主时钟到BLCK时钟,DIV = 12288000 / 1536000 = 8

由于位宽有时又是24位的,采样率还可以选44100Hz,不同的值会导致DIV的计算结果不一定是整数,而数字电路分频肯定是2的整数倍,所以过采样率的倍数有时也要选其他倍数,比如384倍,好得到整除的结果,让频率准确。

以384倍采样率来举例,在采样率44100Hz,位深24位时,384倍可以获得准确分频,但选择256倍就达不到合适的分频,无法对齐了

MCLK = 384 X 44100 = 16934400 Hz

BCLK = 44100 X 24 X 2 = 2116800 Hz

DIV = 16934400 / 2116800 = 8

选择256时

MCLK = 256 X 44100 = 11289600

BCLK = 44100 X 24 X 2 = 2116800 Hz

DIV = 11289600 / 2116800 = 5.333…

很显然硬件电路没法实现这个5.3的分频。

不同电路需要不同的DIV数进行,形成时钟树,供各部分电路使用,所以要分多个寄存器进行设置。

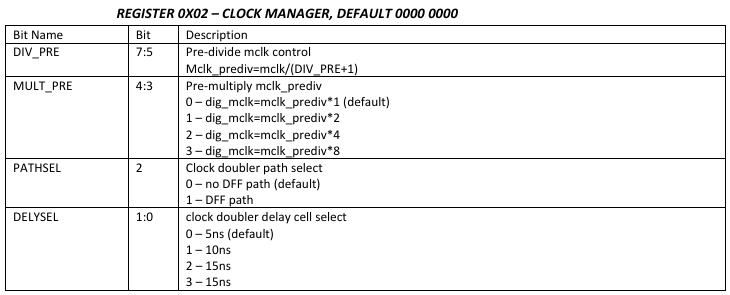

预分频(0x02)

分频后的时钟会进一步供给 PLL(锁相环)或直接用于生成 BCLK(位时钟)和 LRCLK(帧时钟,即采样率时钟)。由于不知道内部电路,可以从官方给的表中推测来验证下。

还是以44.1KHz为例,当主时钟的频率是11289600时

| mclk | rate | pre_div | mult | adc_div | dac_div | fs_mode | lrch | lrcl | bckdiv | adc osr | dac osr |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 11289600 | 44100 | 0x01 | 0x00 | 0x01 | 0x01 | 0x00 | 0x00 | 0xff | 0x04 | 0x10 | 0x10 |

DIV_PRE = 1(查表值对应表中pre_div=1,取值范围1-8),这个主要是分频,查表为1,程序中做了一次减1处理再赋值,寄存器做了一次加1处理,结果为

Mclk_prediv = MCLK / (pre_div -1 + 1) = 11289600 / 1 = 11289600

MULT_PRE = 1(查表值对应表中mult=0,取值范围是0-3)分别是1/2/4/8倍频,1倍频还是11289600

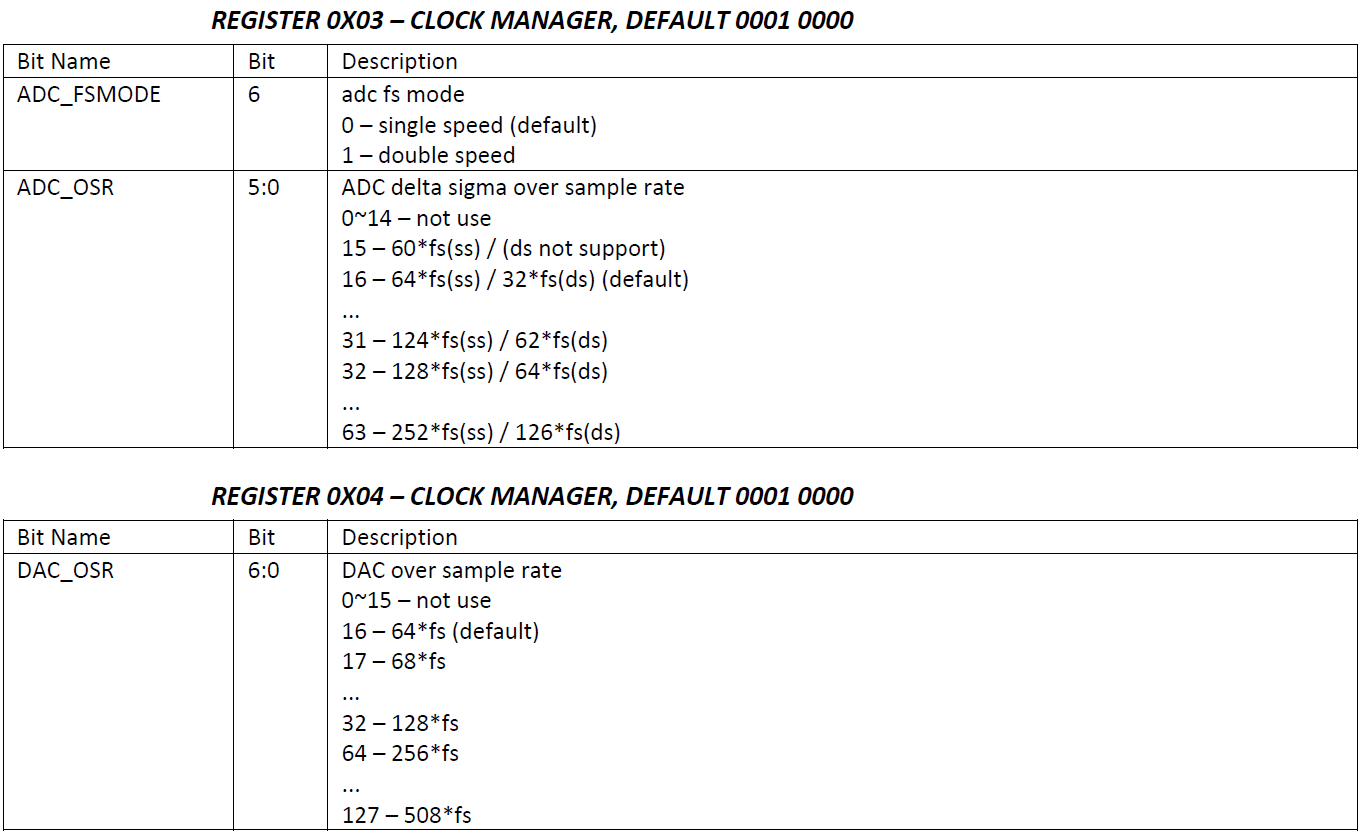

过采样有关的寄存器,ADC电路是(0x03)DAC电路是(0x04)

fs_mode = 0,ADC电路中使用,可以再提高一倍主时钟频率给ADC电路,0没有提高。

adc/dac osr = 0x10, 对应64倍采样率供模/数或数/模转换电路使用。

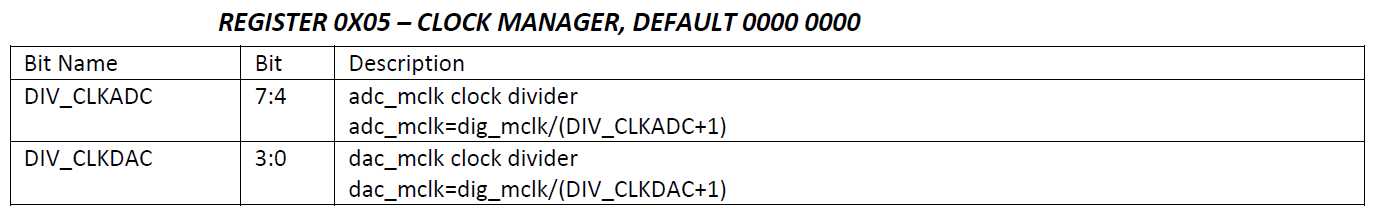

给DAC和ADC的分频(0x05)

查表值都是1,程序中做了减1处理,寄存器再做加1处理,最后就是表示

adc/dac_mclk = dig_mclk = 11289600

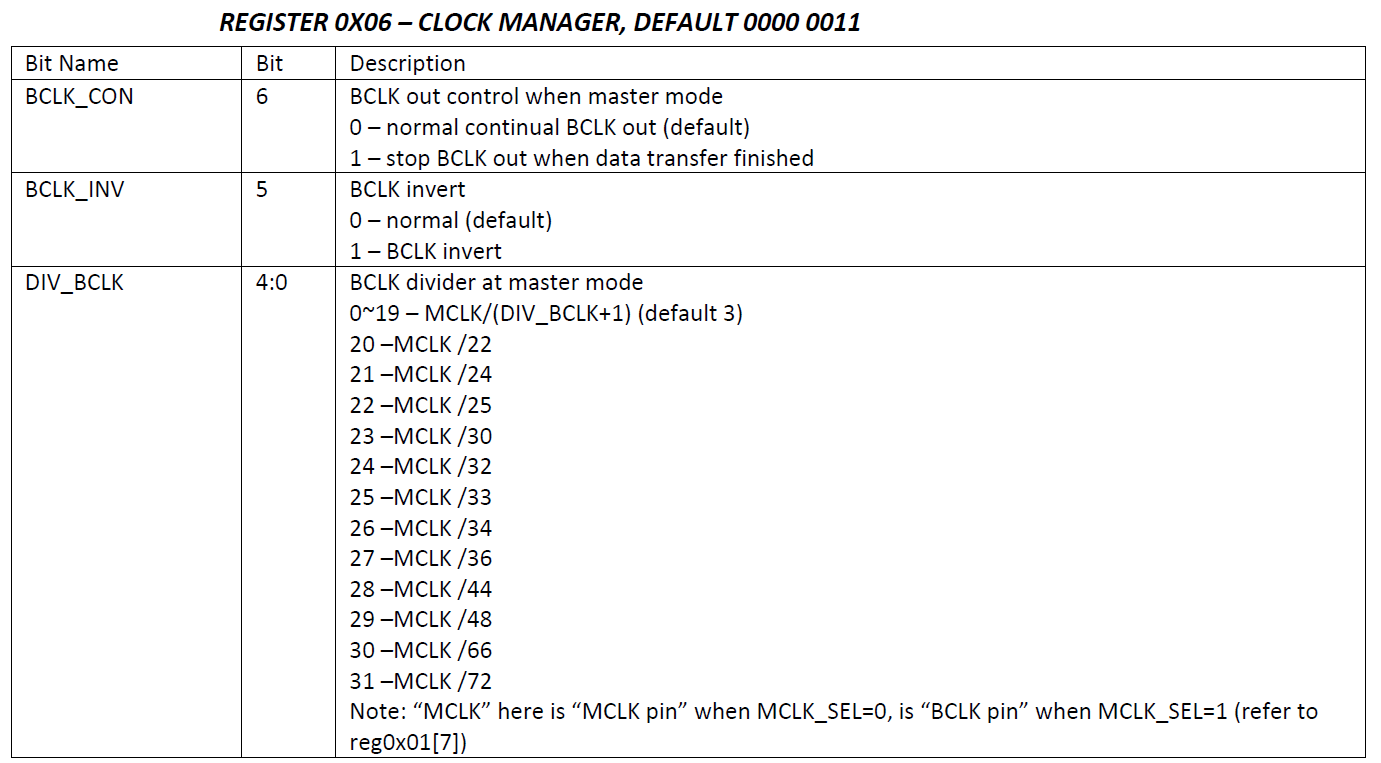

给BCLK的分频(0x06)

注意,这个是输出用的,在ES8311充当主控时才起作用,下面的0x07/0x08寄存器同样如此。

查表值是4,因为小于19,程序中同样先减1,后面寄存器再做加1处理

DIV_BCLK = 4 表示在ES8311充当主控时,BLCK脚输出是 MCLK / 4,即:

BCLK = 11289600 / 4 = 2822400 Hz

MCLK和BCLK在本次电路中都是来自外部,对于ESP32作主控来说,相应信号已经由I2S总线来控制了,这里设置实际上没有用。2822400 / 44100 = 64 也就是在44100采样率下,位信号可以对齐64位数据,2个声道情况下,位宽达到32位(24位位宽时,会补齐到32位数据的位宽进行传输)。这里有个猜想,要是用16位位宽,则可以容纳四个声道数据。是不是就能解决与TDM兼容的问题?待验证。

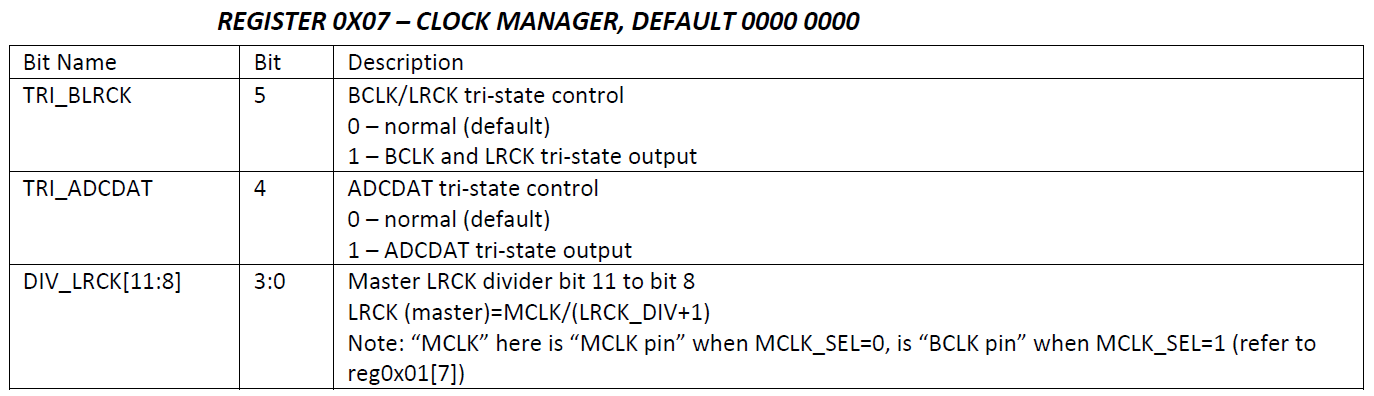

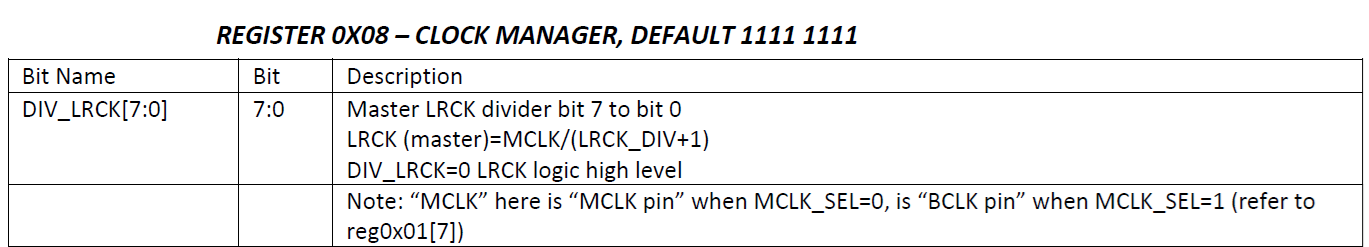

给LRCK的分频(0x07)和(0x08)。

因为超过了8位寄存器值,所以用了高8位和低8位表示,查表值是255(0x00ff)

根据LRCK与采样率的频率是一致的,寄存器加1

LRCK = MCLK / (0x00ff + 1) = 11289600 / 256 = 44100

和采样率一样。

人工计算这些值有点麻烦,特别是位宽不一样时,主时钟频率是否够用要重新选择。好在常用位宽及采样率是固定的,官方给了个表,用查表函数把值找出来,赋值就行了,倒也省心,只需要提前准备好“采样率、采样率的系数、位宽”这三个参数就行了。官方根据硬件提前准备好了宏定义。

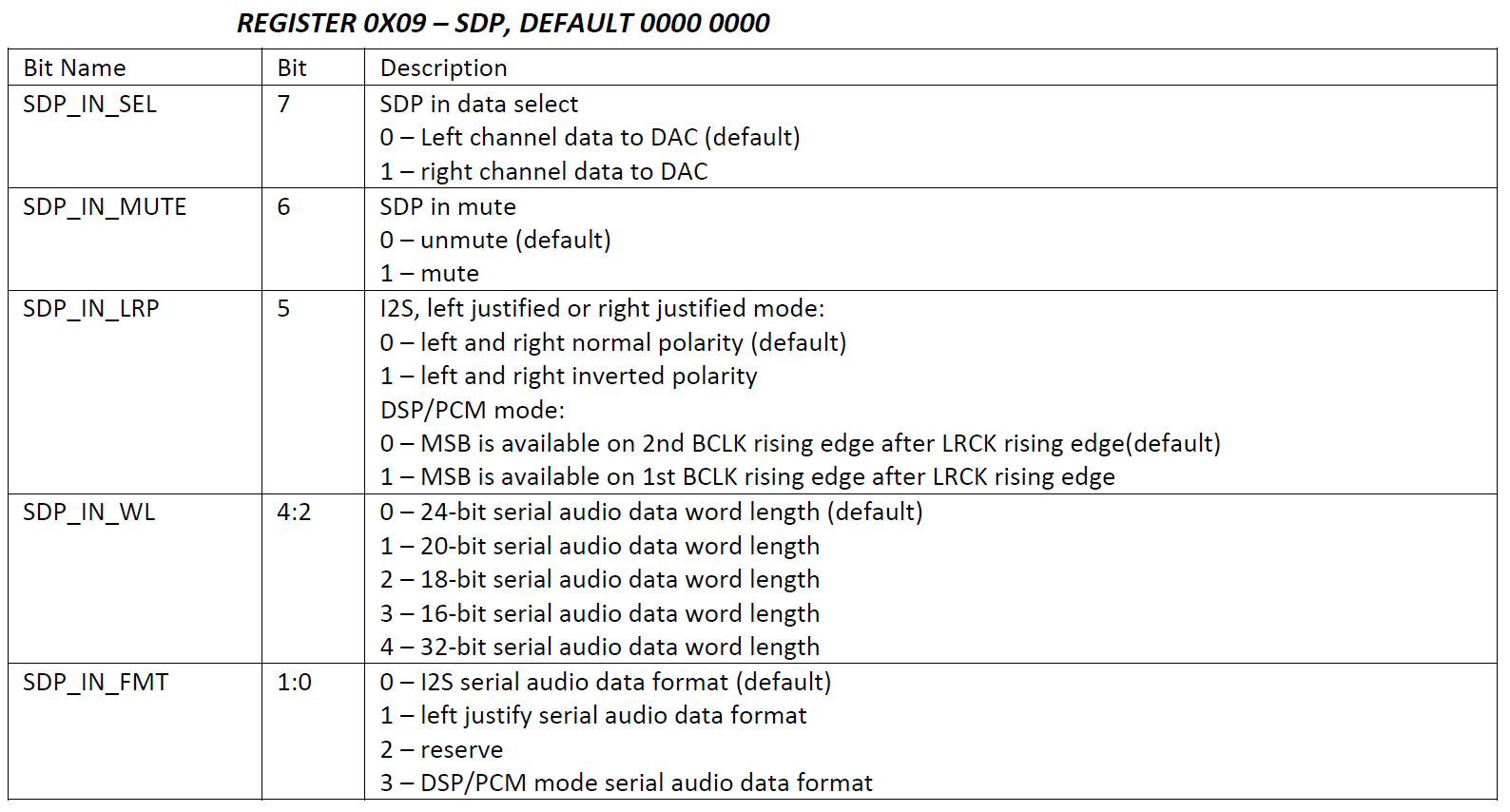

第四步 设置I2S的工作模式

write_reg(ES8311_REG00, 改变第6位的值) // 设置主从机模式,本次硬件电路用默认值,这儿就决定了0x06/0x07寄存器不起作用(忘记在哪儿看到过说是自动计算外部时钟,需要有空时读一下不同时钟输入时寄存器来验证)。在第一次设置电源寄存器时工作模式已经设置过了,没想明白主控程序一旦确定,什么场景需要在工作过程中切换对数据总线的主控。

write_reg(ES8311_REG09, 0x00) // 针对DAC电路,左声道送到输出,不静音,LRCK左低右高,0x00对应24位位宽,LRCK高低时长一样,这块参照I2S的模式更改就行

这个需要特别注意的是,确认了是单声道数据输出。这个寄存器最高位就是控制输出左右哪个声道的。

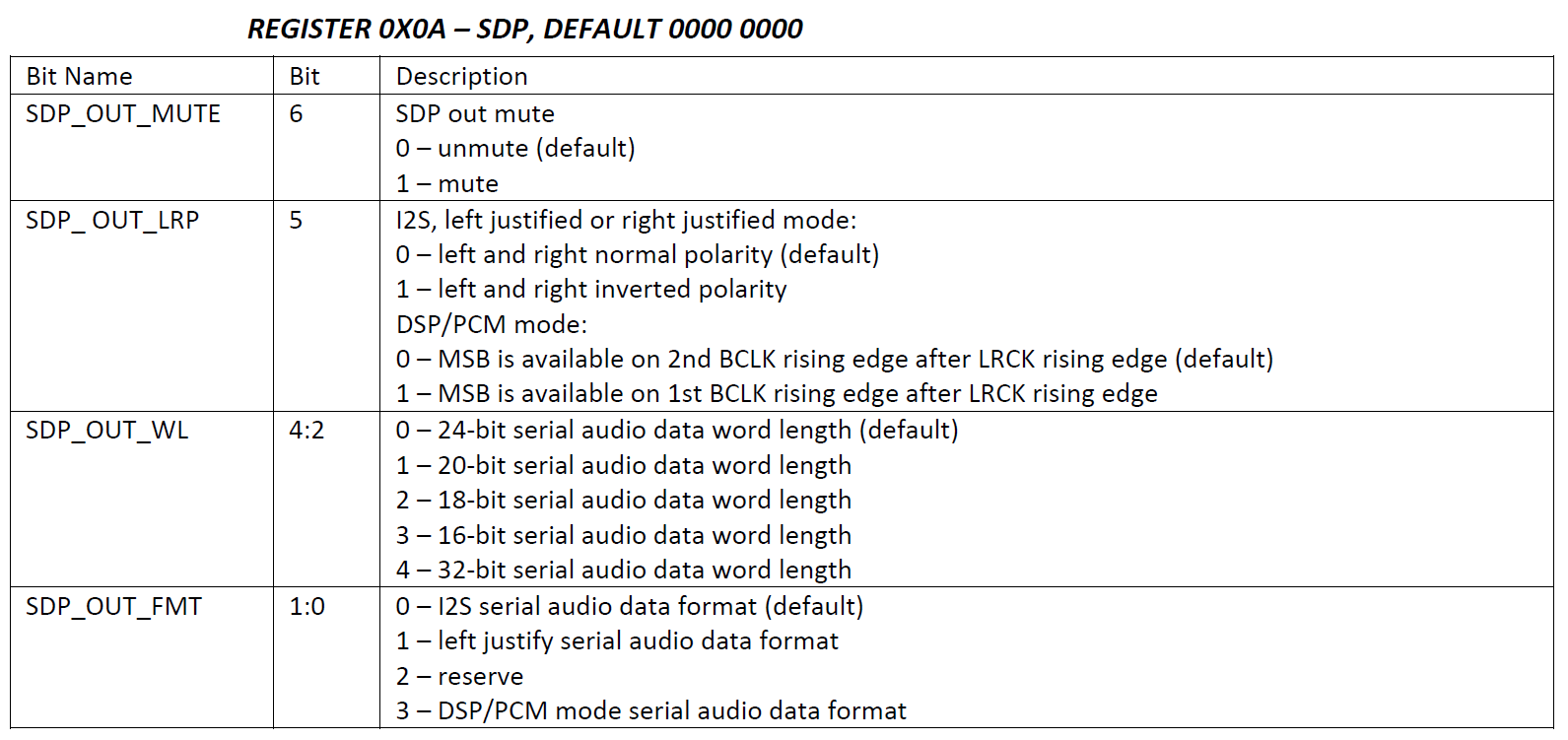

write_reg(ES8311_REG0a, 0x00) // 针对DAC电路,输入不静音,LRCK左低右高,24位位宽,LRCK高低时长一样,本次电路不用麦克风,不需要设置

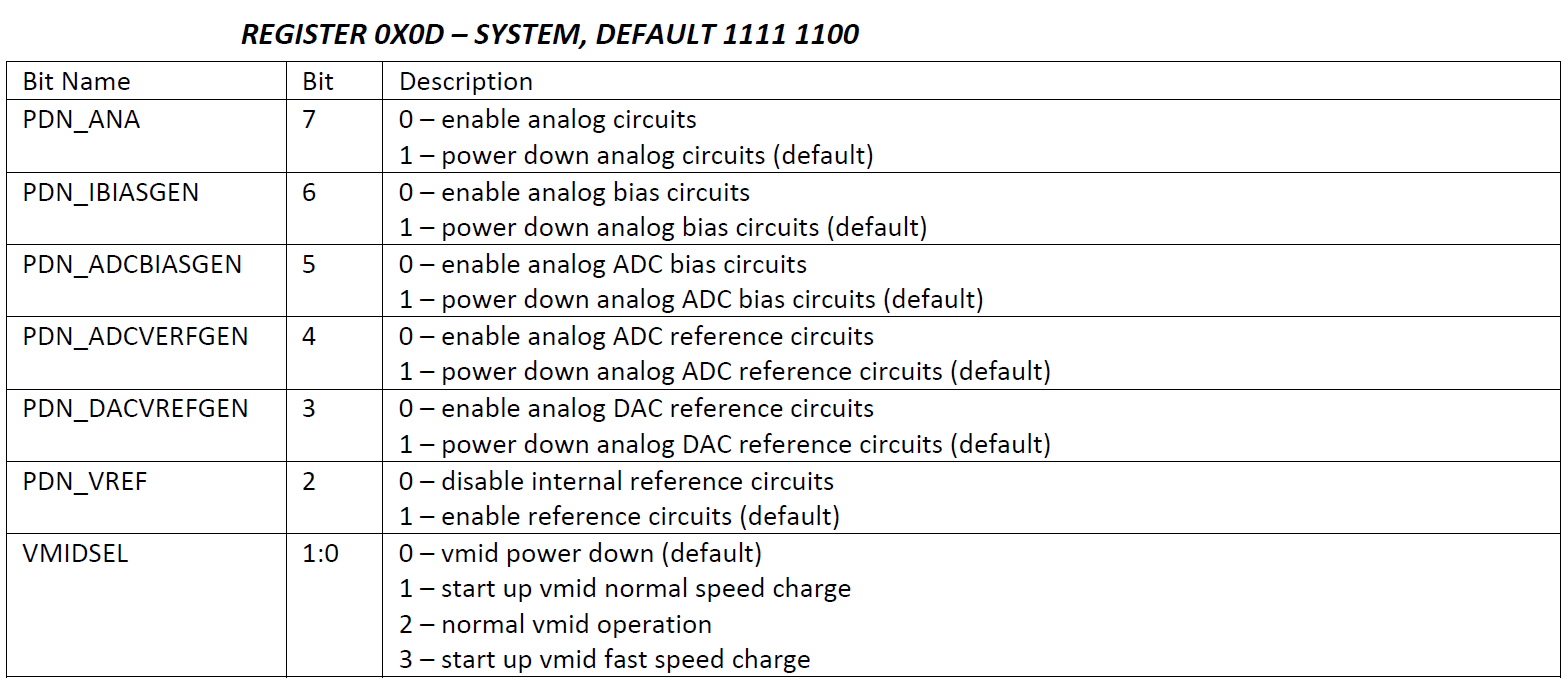

第五步 给各模拟电路供电

(ES8311_REG0D, 0x31) // 后级放大器开,模拟电路偏置电压开,ADC偏置电压关,ADC基准电压关,DAC基准电压开,内部基准电压开,启动VMID(虚拟中点电位)电路。

VMID 电路有四个选择

| 位值 | 功能 |

|---|---|

| 00 (Power Down) | 用于 低功耗模式(如设备待机、睡眠状态)。唤醒后需切换至 01 或 11 重新充电。 |

| 01 (Normal Speed Charge) | 适用于 普通音频播放(如音乐、视频),平衡功耗和启动时间。 |

| 10 (Normal Operation) | 默认工作状态,VMID 已充满电,提供稳定电压。 |

| 11 (Fast Speed Charge) | 用于 快速唤醒(如电话接听、语音助手),减少延迟,但电流消耗更大。 |

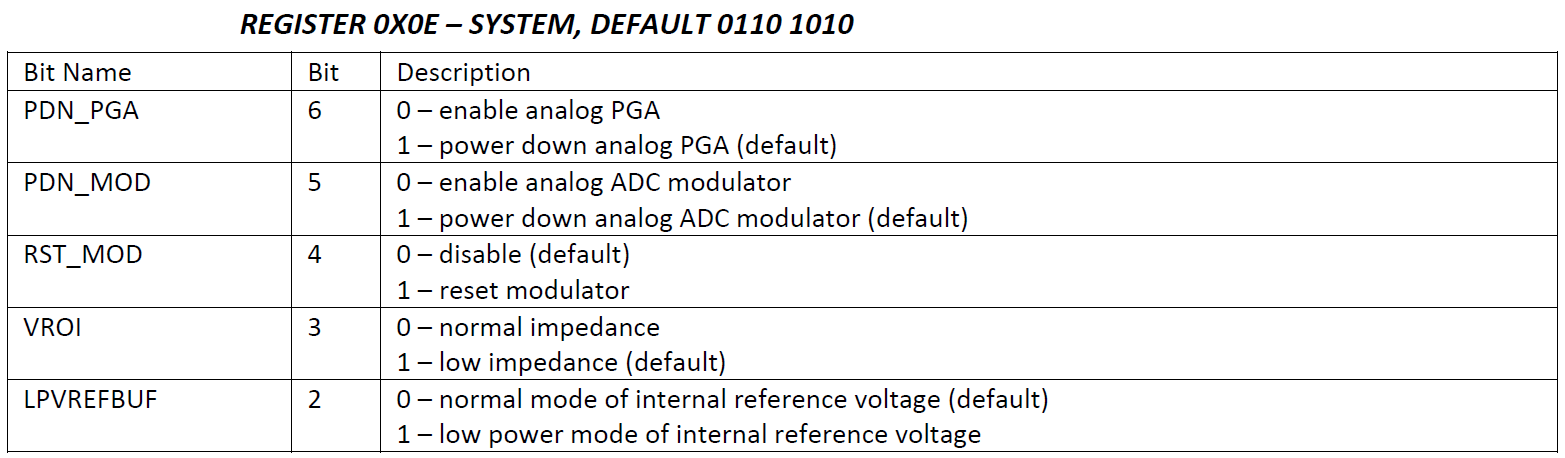

(ES8311_REG0E, 0x6a) // 是用默认值,本次电路不用,PGA是麦克风电路的

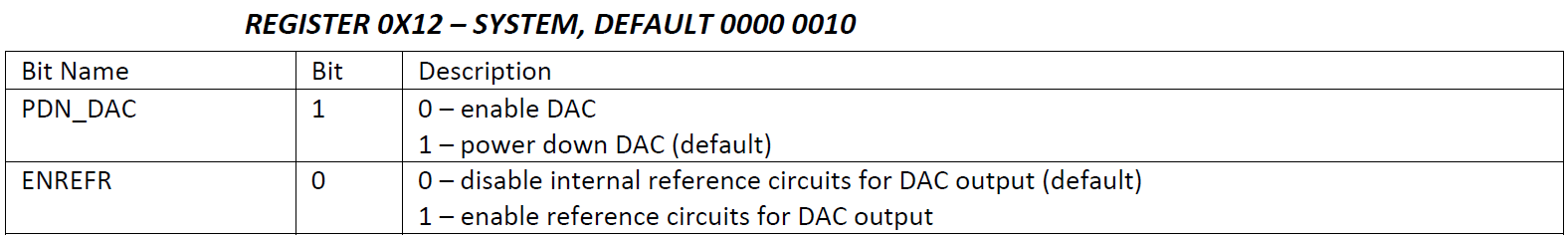

(ES8311_REG12, 0x00) // DAC部分模拟电路供电开和内部输入到输出关

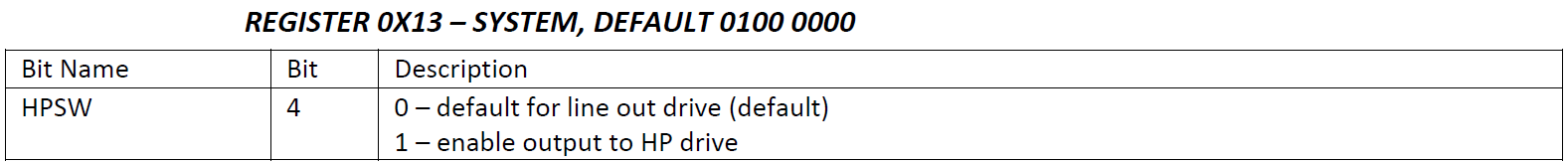

(ES8311_REG13, 0x00) // 是线路输出还是耳机输出,后面有功放,用线路输出比较好点 官方用的0X10耳机输出,我试了,在外接功放时没什么区别

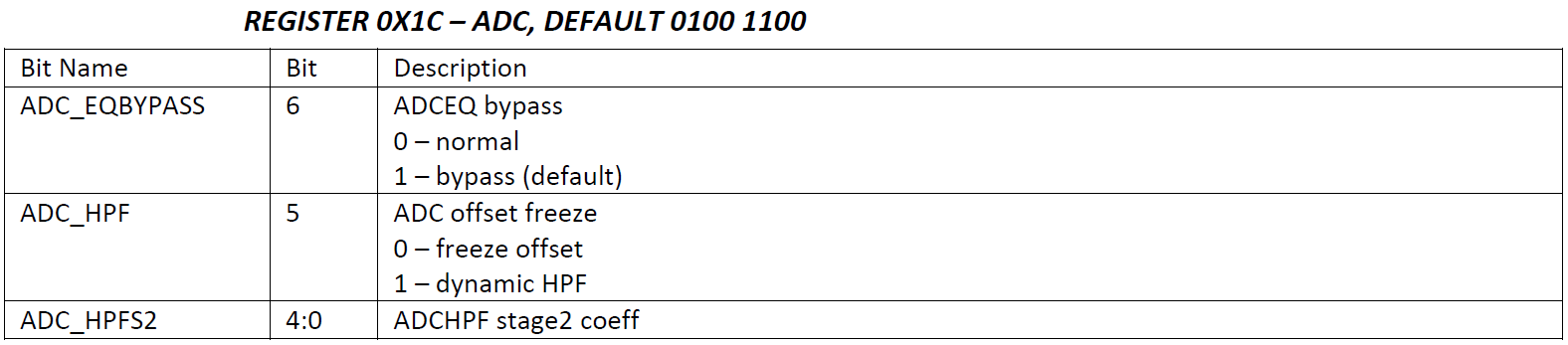

(ES8311_REG1C, 0x6A) // ADC的调音,本次电路不用

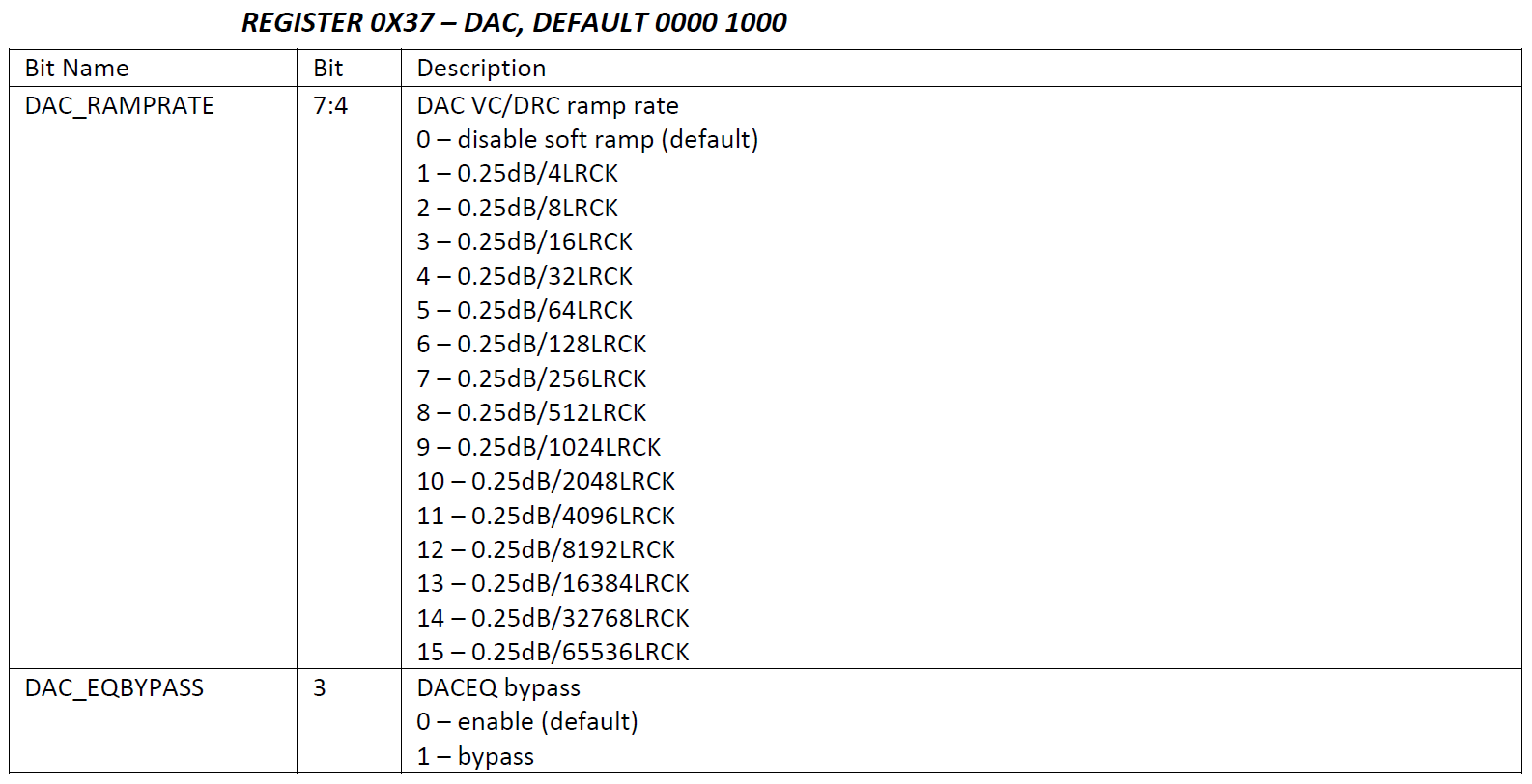

(ES8311_REG37, 0x08) // DAC调音用的,0x08是默认值,我试着用了0x00,结果只有噪音了。

设置音量

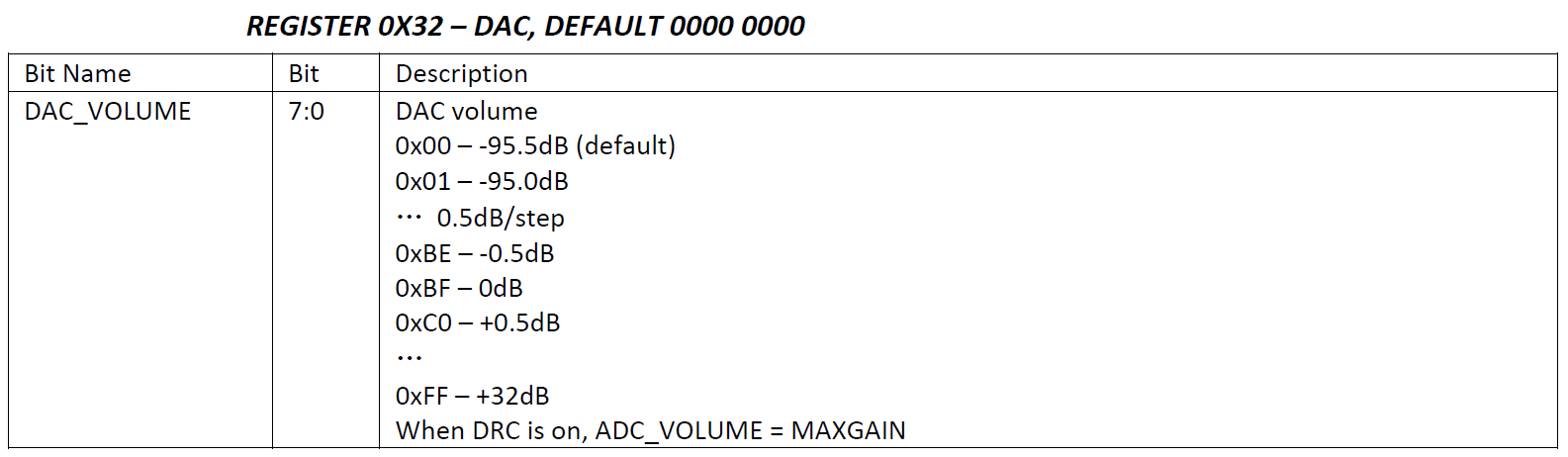

(ES8311_REG32, 0xff) // DAC 音量,默认是0,最大255,可以编个映射的函数设定音量曲线调整。

这其中还有些更多调音的设置,没再细分析了,需要可以跟一下官方组件中的函数所涉寄存器。

官方组件中的说明:为了平衡在不同平台上播放相同内容的响度差异,需要了解音频增益的相关机制。简单说来音频增益包括软件增益 (可调节)和硬件增益 (不可调节) 两部分。软件增益可以通过改变音频数据的幅值或者改变音量寄存器实现。硬件增益受外围电路的影响,主要取决于模拟信号的放大系数。实现中选取了典型的影响参数 esp_codec_dev_hw_gain_t,作为配置参数进行配置,以抵消平台间响度差异,详情可参考代码注释 [esp_codec_dev_vol.h]。

结句语

还要补允些知识。I2S总线就是其中之一,想要让ES8311与其他设备协同工作好,实际设置中还要回到I2S的设置过程。后面要再根据ESP32的I2S库来分析下主控是如何进行I2S总线设置的。避免初始化过程中一些冲突。

1408

1408

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?