Netlist 仿真和RTL比匹配主要是因为Netlist会存在不定态以及传播不定态,导致仿真不正确;

不定态的来源:

大多数设计在上电时不能保证cell的特定的逻辑状态。flip flop或memory根据环境因素,芯片间的工艺差异等可能会有不同的初始态(可以根据这种特性设计出SRAM PUF)。

因此,在仿真时间0时,flip flop或memory会输出X,直到在第一个时钟沿被加载一个新的逻辑值。

在仿真中还有其他一些常见的不定态X来源:

•缺少仿真模型,或仿真设置中出现其他错误。

•对于testbench外部输入信号没有设置初始值

•一些锁相环时钟仿真模型输出X ,直到lock

•发生时序违例(timing violation)

•当使用back annotated时序进行仿真时,输入信号传播到之前还是不定态X

•一些cell library在任何一个输入是X时,就会输出X,即使已知输出的逻辑值。

不定态X的传播

在现实中不会存着真正的X逻辑值,只是cell library考虑到所有可能组合,最终无法确定输出的逻辑值。

- VCS仿真选项+nospecify和+notimingcheck没打开,注意后仿(带sdf)时应该将+nospecify去掉

- 有的模块没接上复位信号,用VCS仿真时rstn为高阻,功能可能正确;但是综合工具可能会把这些DFF的复位端口统统接0,这样输出就永远为0,进而就会被工具优化掉

- 如果想要工具不优化上述constant型的寄存器,可以将compile_seqmap_propagate_constants变量设置为false

- RTL功能正确,综合后网表仿真存在大量不定态,原因有可能是控制通路存在X态、输入输出信号声明错误(即input声明为output,output声明为input,RTL仿真可能没问题),控制通路存在X态考虑如下实际例子:

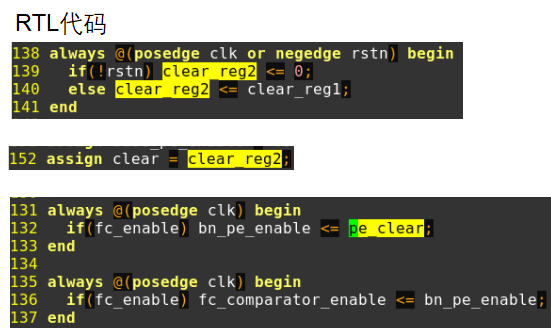

RTL代码如下,其中clear2(pe_clear)信号带有复位逻辑,而bn_pe_enable和fc_comparator_enable不带复位:

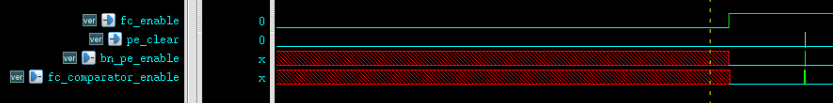

RTL仿真波形如下图所示,可以看到,pe_clear被复位至0,在fc_enable信号拉高以后,bn_pe_enable和fc_comparator_enable三个信号都立即变为低电平(这其实与实际电路不符,不定态没有传播,所以不定态在RTL阶段传播很重要!!!)

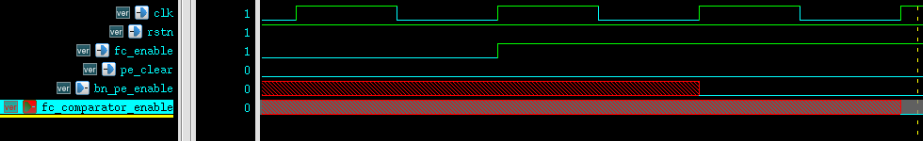

综合以后的网表仿真如下图所示,可以看到,在fc_enable拉高后1个周期bn_pe_enable才从X态变为低电平,而fc_comparator_enable在fc_enable拉高2个周期后才从X态变为低电平

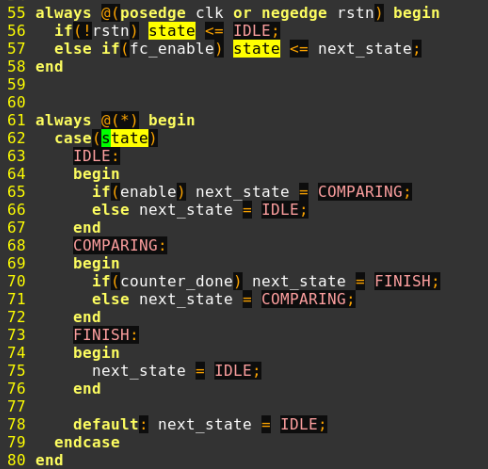

上述控制信号被用于fc_comparator中的如下状态机:

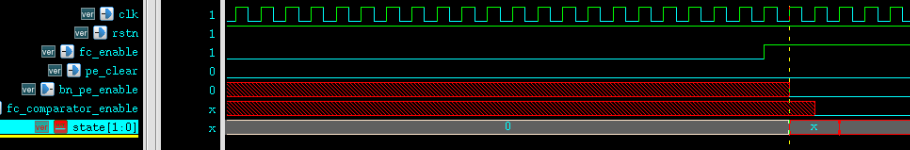

网表仿真如下图所示,可以看到,在fc_enable拉高后state开始更新状态,由于输入的fc_comparator_enable为X态,state更新为了一个X态,导致电路出错。

- 关于+neg_thck

1.PR后的timing rpt没有时序违反,那sdf里负的hold 是什么意思,是好是坏?

没有关系,hold为负值的意思是信号在时钟沿之前指定时间内(那个负值的绝对值)翻转都不会出问题。

2 有error,提示要加+neg_thck,这个和负的hold有什么关系吗?加+neg_tchk貌似把负的hold修成0了?

需要+neg_thck,我认为不是因为“+neg_tchk”才把负值改为0,而是因为工具不支持负值,

所以把负值改为0来计算,这样相当于仿真时hold check更苛刻了。

3.+notimingcheck就相当于不检查负的hold?那影响仿真所加时序吗?这个命令在仿真时候需要加吗?

时序仿真不能用“+notimingcheck”,只有功能仿真时才可以加这个选项。

- Round问题

tensorflow的tf.round()函数其实不是“四舍五入”,而是“四舍六入五取偶”,即:

1、整数为偶数则舍去小数;

2、整数为奇数则进位到整数

本文探讨了Netlist仿真与RTL比对时出现的不定态X问题,包括其来源、传播以及对功能正确性的影响。强调了初始化、时序违例和模型缺失等因素,并通过实例说明了不定态在控制通路中的传播如何导致错误。同时提到了VCS仿真的相关选项,如+nospecify和+notimingcheck的使用,以及在综合后不定态可能导致的问题。此外,还讨论了时序报告中负的hold时间和+neg_thck选项的相关性。

本文探讨了Netlist仿真与RTL比对时出现的不定态X问题,包括其来源、传播以及对功能正确性的影响。强调了初始化、时序违例和模型缺失等因素,并通过实例说明了不定态在控制通路中的传播如何导致错误。同时提到了VCS仿真的相关选项,如+nospecify和+notimingcheck的使用,以及在综合后不定态可能导致的问题。此外,还讨论了时序报告中负的hold时间和+neg_thck选项的相关性。

8970

8970

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?