一,方案选择

方案一:采用FPGA中的高速DAC发送信号,FPGA具有强大的并行计算能力,能够同时处理多个数据流,能够提供非常低的延时,远远优于传统的CPU;但是FPGA的编程速度耗时且功耗大。

方案二:采用单片机STM32,DDS产生信号,但是受单片机内部时钟信号影响和内部DAC速度限制,很难应用与高频信号中;

方案三:采用集成DDS芯片AD9959制作实现,其最高工作时钟为500MHz,可以输出2MHZ和40MHz的正弦信号。可以便捷改变载波和调制波输出幅度和频率,同时可设置初始位移和时延。

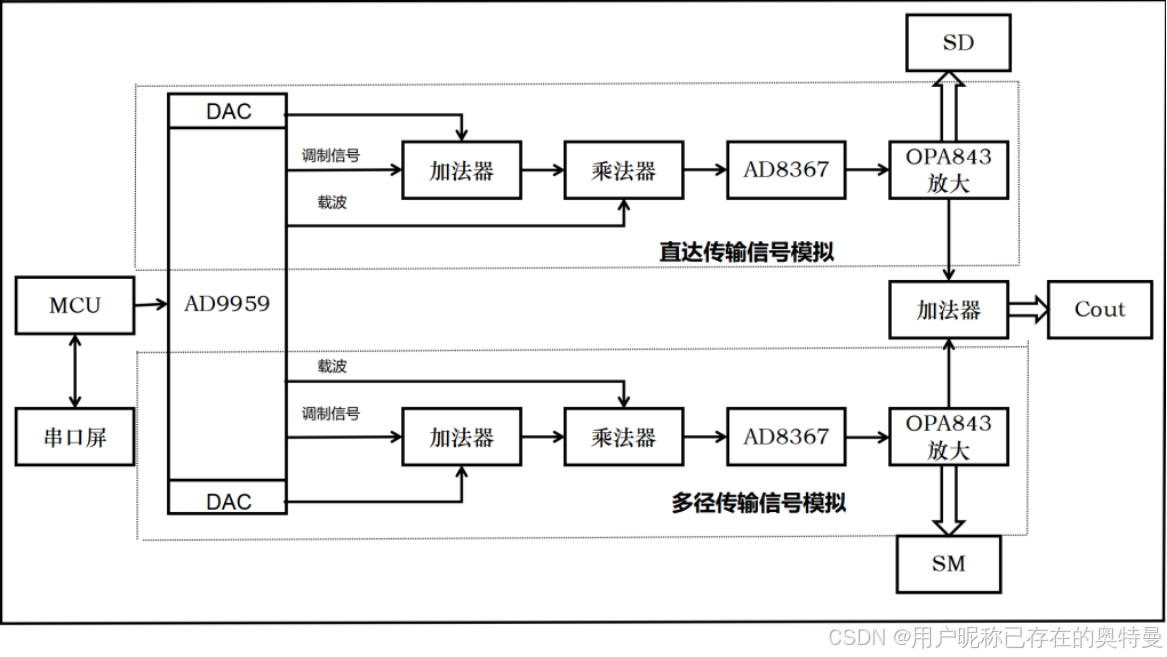

通过上述分析比较,我们选择采用STM32+AD9959来模拟输出无限传输信号。

二,硬件方案

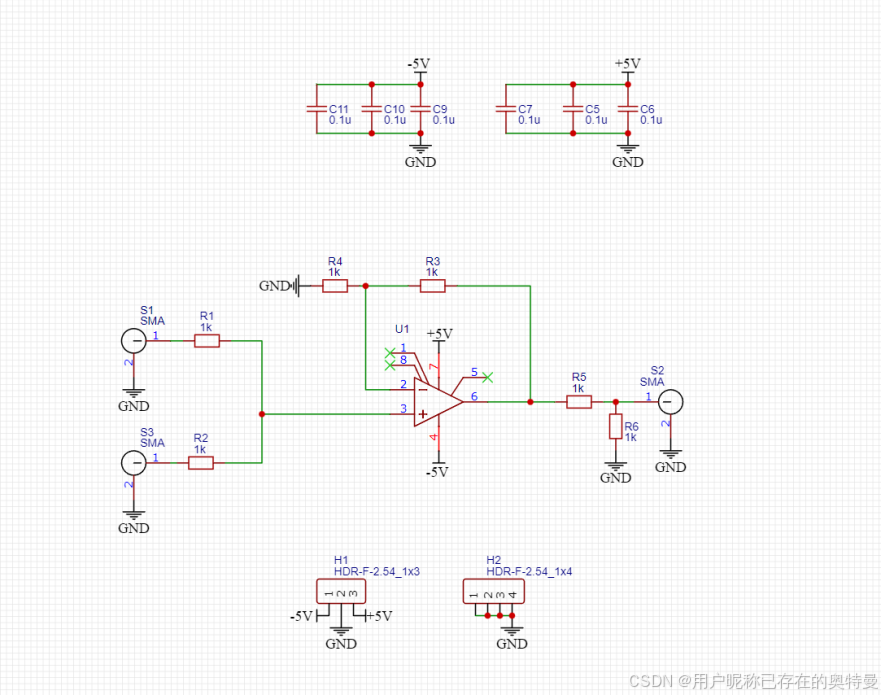

1.加法器电路设计

根据叠加定理,当有多路信号输入时,反相和同相放大电路可构成加法电路。此处采用同相加法电路,最终实现叠加直流和最终合波。加法器电路如图3-1所示。

图3-1 加法器电路

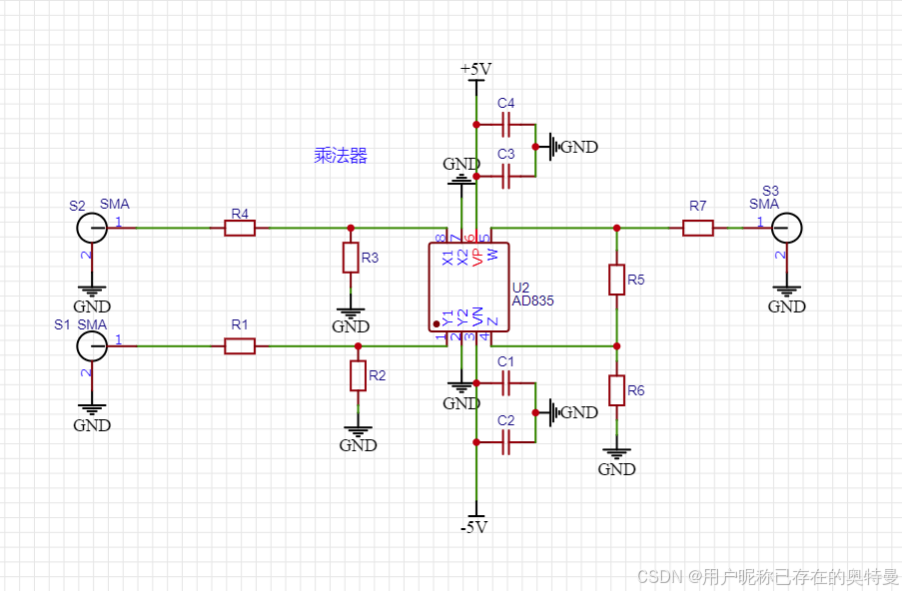

2.乘法器模块设计

乘法器主要用于完成两个互不相关的模拟信号的相乘作用。乘法器的基本原理是通过一系列计算机算数技术实现的,它由更基本的加法器组成。乘法器不仅用于乘法运算,还广泛应用于电子通信系统中的调制、解调、混频、鉴相和自动增益控制等场合。我们这里的乘法器主要用于调制。

3-2 乘法器电路

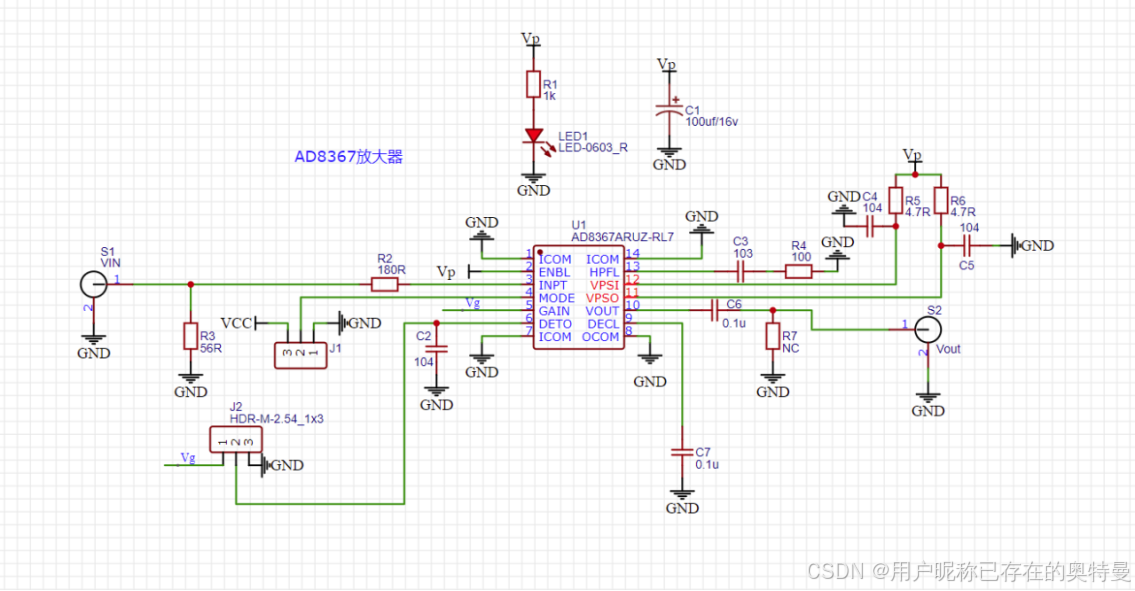

3放大器模块设计

首先需要明确所需放大器的具体类型,如电压放大器、功率放大器和运算放大器,这里我们选用运算放大器作为主要作用。通过设置放大器的反馈电阻或输入电阻来实现。根据具体的应用需求,确定一个合适的增益值。

图3-3 放大器电路

三、结语

针对这个题我还是感悟颇深,对调制度及高频处理有了更多的体会,方案已经经过论证,百分百实现。

3162

3162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?