以下内容摘自《步步惊芯——软核处理器内部设计分析》一书

14.1 SB模块的作用与工作过程

ICache是直接与Wishbone总线接口单元WB_BIU相连的,但是在DCache与Wishbone总线接口单元WB_BIU之间插入了一个Store Buffer(SB)模块,如图1.6所示。

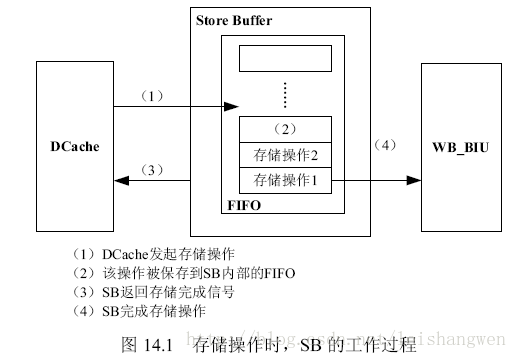

SB的作用是通过缓冲存储操作,从而加快存储操作。其原理是这样的:当执行存储操作时,可能需要通过WB_BIU将要写的数据写入外部Memory,尤其是在通写法模式下,每次执行存储操作都要将数据写入外部Memory,这样会等待外部Memory完成存储操作,在此期间,CPU处于暂停状态,降低了CPU的效率,引入SB后,如果是存储操作,那么SB模块将本次操作保存起来,同时立即向DCache返回一个存储完成信号(dcsb_ack_o为1),使得CPU可以继续执行,然后SB模块会接着完成被其保存起来的存储操作。在SB内部有一个FIFO(先入先出队列)作为缓冲,如果是连续的多个存储操作,那么会将每个存储操作都存放在FIFO中,并向DCache返回存储完成信号,然后SB从FIFO中取出要保存的数据,完成存储操作。图14.1是存储操作时SB的工作过程。

上述设计会带来两个问题:

(1)SB直接向DCache返回存储完成信号,但如果在SB通过WB_BIU模块向外部Memory存储的过程中发生错误如何处理?

(

本文详细介绍了OR1200处理器中Store Buffer(SB)的设计和作用,旨在加快存储操作。SB通过缓冲存储指令,提高CPU效率,避免因外部Memory操作引起的暂停。文中还讨论了SB在数据一致性与错误处理方面的问题,并提供了模块结构和接口信息,以及示例程序以验证SB模块的效果。通过对SB和内部FIFO的分析,展示了SB如何减少存储操作的时钟周期。

本文详细介绍了OR1200处理器中Store Buffer(SB)的设计和作用,旨在加快存储操作。SB通过缓冲存储指令,提高CPU效率,避免因外部Memory操作引起的暂停。文中还讨论了SB在数据一致性与错误处理方面的问题,并提供了模块结构和接口信息,以及示例程序以验证SB模块的效果。通过对SB和内部FIFO的分析,展示了SB如何减少存储操作的时钟周期。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2811

2811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?