一、南北桥架构的起源与经典设计(1990-2004)

1.1 架构定义与功能划分

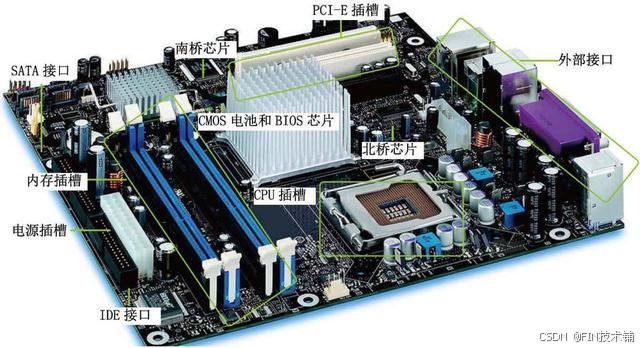

在早期PC架构中,**北桥(Northbridge)和南桥(Southbridge)构成主板的核心逻辑芯片组,通过前端总线(FSB)**与CPU协同工作:

- 北桥:负责高速设备互联

- CPU与内存控制器(DRAM Controller)

- 高速图形接口(AGP/PCIe)

- 前端总线(FSB)管理

- 南桥:管理低速外设与扩展功能

- PCI总线控制器

- SATA/IDE存储接口

- USB/LAN/音频编解码器

- BIOS与LPC(Low Pin Count)总线

典型芯片组案例:Intel 440BX(1998)

- 北桥82443BX:支持Pentium II,133MHz FSB,SDRAM控制器

- 南桥82371EB(PIIX4E):集成USB 1.1、IDE、AC97音频

1.2 技术瓶颈与架构缺陷

- 带宽瓶颈:

FSB带宽限制导致CPU与北桥通信效率低下(如Pentium 4的800MHz FSB理论带宽仅6.4GB/s)。 - 延迟问题:

数据需经北桥中转,内存访问延迟高达100ns以上。 - 功耗与散热:

北桥因高频工作成为主板发热核心,需独立散热片(如nForce 590 SLI北桥功耗达15W)。

1.3 典型总线技术演进

| 总线类型 | 带宽 | 应用场景 |

|---|---|---|

| FSB | 6.4GB/s (800MHz) | CPU-北桥通信 |

| AGP 8x | 2.1GB/s | 显卡连接 |

| PCI 2.3 | 133MB/s | 扩展卡(声卡、网卡) |

| ATA-133 | 133MB/s | 硬盘接口 |

二、技术转折点:北桥的消亡与CPU集成(2004-2011)

2.1 内存控制器集成(AMD K8 vs Intel Nehalem)

- AMD Athlon 64(2003):

首次将内存控制器集成至CPU,消除北桥的DRAM控制功能,延迟降至50ns以内。 - Intel Nehalem(2008):

引入集成内存控制器(IMC)与QuickPath Interconnect(QPI),北桥功能开始瓦解。

2.2 北桥功能解构

- 图形核心集成:

Intel Clarkdale(2010)将GPU集成至CPU封装内,AGP/PCIe控制器转移至CPU。 - PCIe直连CPU:

Sandy Bridge(2011)支持CPU直连PCIe 3.0,北桥仅保留部分I/O功能。

2.3 架构对比:传统 vs 集成

| 组件 | 传统架构(Pentium 4) | 集成架构(Sandy Bridge) |

|---|---|---|

| 内存控制器 | 北桥(如i875P) | CPU内置IMC |

| PCIe控制器 | 北桥提供16x通道 | CPU直连16x PCIe 3.0 |

| GPU位置 | 独立显卡(北桥管理) | CPU集成HD Graphics 2000 |

| 典型延迟 | 内存延迟100ns | 内存延迟40ns |

三、南桥的蜕变:从低速总线枢纽到平台控制器中枢(2011-2020)

3.1 南桥功能扩展与标准化

Intel将南桥重命名为平台控制器中枢(PCH,Platform Controller Hub),承担更多系统管理功能:

- 接口升级:

SATA 6Gbps、USB 3.0(5Gbps)、PCIe 2.0(5GT/s) - 高级功能集成:

- 可信平台模块(TPM 2.0)

- 千兆以太网MAC层

- 高精度时钟与电源管理

典型PCH案例:Intel Z97(2014)

- 支持6x SATA 6Gbps、6x USB 3.0

- 集成Realtek音频Codec与LAN PHY

- 提供8x PCIe 2.0通道

3.2 DMI总线的演进

CPU与PCH间采用直接媒体接口(DMI),带宽逐步提升:

- DMI 1.0(2004):1GB/s(4x PCIe 1.0)

- DMI 3.0(2015):3.93GB/s(4x PCIe 3.0)

- DMI 4.0(2020):7.88GB/s(8x PCIe 4.0)

3.3 异构计算的挑战

随着PCIe设备复杂度提升(如NVMe SSD、USB4),PCH需支持更灵活的拓扑结构:

- PCIe分叉(Bifurcation):允许单个x16插槽拆分为x8/x8或x4/x4/x4/x4

- 动态带宽分配:基于使用场景调整USB与SATA带宽优先级

四、现代SoC时代:南北桥功能的彻底重构(2020至今)

4.1 全集成SoC架构

在移动与嵌入式领域,**系统级芯片(SoC)**将传统南北桥功能完全整合:

- Apple M1(2020):

- 集成CPU/GPU/神经引擎

- 统一内存架构(UMA)

- Thunderbolt 4控制器直连SoC

- AMD Ryzen 6000(2022):

- 内置USB4控制器

- 支持PCIe 5.0与DDR5

4.2 功能模块化与Chiplet设计

- Intel Meteor Lake(2023):

采用多芯片封装(Compute Tile、SoC Tile、GPU Tile),SoC Tile集成传统南桥功能。 - AMD X670(AM5平台):

通过Promontory 21芯片实现双PCH级联,支持24x PCIe 5.0通道。

4.3 协议融合与高速互连

- USB4与Thunderbolt 4:

统一基于PCIe 3.0与DisplayPort Alt Mode,带宽达40Gbps。 - CXL(Compute Express Link):

在PCIe 5.0基础上增加缓存一致性协议,支持内存池化与加速器直连。

五、技术驱动力与未来展望

5.1 核心驱动力

- 性能需求:降低延迟(从100ns至10ns级)、提升带宽(DMI 4.0达63Gbps)

- 功耗优化:制程升级(从130nm至5nm)减少I/O PHY功耗占比

- 成本控制:芯片组集成降低主板布线复杂度与BOM成本

5.2 技术挑战

- 信号完整性:PCIe 6.0(64GT/s)要求PCB阻抗控制精度达±5%

- 热设计:高密度封装下局部热点(如USB4控制器)需微流道散热

- 安全隔离:防止DMA攻击需硬件级IOMMU保护

5.3 未来趋势

- 光互连集成:硅光引擎(Silicon Photonics)替代铜互连,突破距离与带宽限制

- AI驱动的资源调度:基于机器学习预测I/O负载,动态调整PCIe/USB带宽分配

- 全功能SoC:南桥残余功能(如RTC、GPIO)最终融入CPU Die

结语

南北桥架构的演进史本质是计算机系统从分立模块化向高度集成化转变的缩影。这一过程不仅重构了硬件拓扑,更推动了PCIe/CXL等协议的创新。未来,随着Chiplet与光互连技术的成熟,传统“桥接”概念将彻底消融,代之以更智能、更高效的异构计算平台。

5910

5910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?