简介

本章节是对于高速IO接口应用的一个扩展,目前扩展为SATA(SSD硬盘,机械硬盘不能使用)。通俗易懂的讲,即把SSD硬盘当做大型的Nand Flash来处理,不格式化硬盘,直接以地址和数据的格式,在SATA盘中写入数据,该数据不能被Window和linux直接识别,需单独编写App来查看SSD硬盘内部,根据协议来完成数据的识别。

FPGA实现SSD硬盘的存储,有点在于速度优势(可达到200MB/s),在存储未经过压缩的数据时,有先天的优势。同理在于可扩展性和对于数据的系统处理性,没有带有操作系统的芯片功能强大。

应用

应用1:存储未经压缩过得图像,循环存储

应用2:存储通信信息,并加密备份

应用3:存储加密文件,防止销毁数据,防止恢复数据。

硬件框图

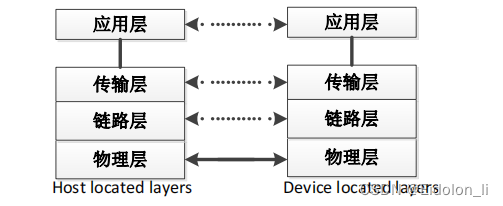

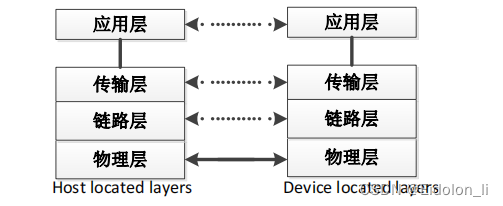

SATA协议从上到下分为四层如图,物理层、链路层、传输层和应用层

订阅专栏 解锁全文

订阅专栏 解锁全文

860

860

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?