1.PAE和PSE

1.1、PAE(Physical Address Extensions)

在x86 CPU中,只有32位地址总线,也就意味着只有4G地址空间。为了实现在32位系统中使用更多的物理内存,Intel CPU提供了PAE(Physical Address Extensions)机制,这样可以使用超过4G物理内存。PAE机制的打开,需要设置CR0、CR4控制寄存器和IA32_EFERMSR寄存器。设置值为CR0.PG = 1,CR4.PAE = 1和IA32_EFER.LME = 0。但PAE机制打开后,MMU会将32位线性地址转换为52位物理地址。尽管物理地址是52位(4PB),但线性地址仍然为32位,即进程可使用的虚拟内存不超过4GB。

1.2、PSE(Page Size Extensions)

前面提到x86/x86_64 CPU中提供的是段页式机制,也介绍了页面。页面大小虽然是固定的,但x86/x86_64 CPU支持两种页面大小4KB和4MB。大多数情况下OS内核使用的是4KB页面,但系统中多数进程使用内存较大时,如每次申请至少4MB,则使用4MB页面较为合适。当控制寄存器CR4.PSE = 1时,页面大小是4MB。

2.PAE页面机制地址映射过程

PAE(Physical Address Extension)是IA-32架构中物理地址扩展机制。在正常情况下,32位系统只能使用4G物理内存,但使能PAE机制后使地址总线达到36根,最大可以访问64G物理内存。必须设置CR0寄存器的第31bit为0(CR0.PG=1),打开页式映射机制;设置CR4寄存器第5bit为1(CR4.PAE=1)和IA32_EFERLMW=0,使能PAE机制。当逻辑处理器使用PAE页面机制时,会将32位线性地址转换为52位物理地址。

2.1 PDPTE寄存器

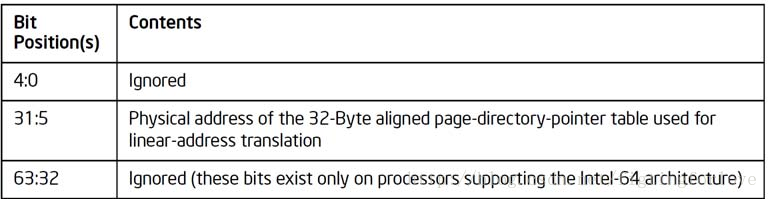

当使用PAE机制时,CR3寄存器的值是指向32字节对齐的页面目录指针表(Page Directory PointerTable)。

图1 PAE机制下CR3寄存器的使用

页面目录指针表中共有4个64bit项,称为PDPTEs。每个PDPTE控制1G线性地址空间的访问。对应PDPTE,逻辑处理器维护4个架构无关的内部PDPTE寄存器,分别为PDPTE0、PDPTE1、PDPTE2、PDPTE3。

图2 PAE机制下PDPTE格式

2.2逻辑地址到线性地址的映射

PAE机制仅与页面映射有关,因此逻辑地址到线性地址映射过程一样。详细步骤请参考地址映射部分的非PAE机制下映射过程。

2.3 线性地址到物理地址的映射

PAE机制可以映射4K页面或者2MB页面,在此我们仅考虑4K页面的映射过程,如下图所示。

本文详细介绍了x86_32架构下的PAE(Physical Address Extensions)机制,包括PAE如何通过PDPTE寄存器扩展地址空间至64GB,并详细阐述了线性地址到物理地址的映射过程,包括PDPTE、页面目录表和页面表项的作用。通过对实例的分析,验证了PAE机制下的地址映射。

本文详细介绍了x86_32架构下的PAE(Physical Address Extensions)机制,包括PAE如何通过PDPTE寄存器扩展地址空间至64GB,并详细阐述了线性地址到物理地址的映射过程,包括PDPTE、页面目录表和页面表项的作用。通过对实例的分析,验证了PAE机制下的地址映射。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3488

3488

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?