由于所有的APP都是在DDR中运行的,所以先让DDR工作起来是后续实验的基础.使用的硬件是z-turn开发板.

本文主要讲怎样创建一个内存测试程序,测试DDR,程序还是运行在内部RAM;FPGA涉及的内容有怎样配置DDR参数,及怎样保存和导入硬件参数;软件方面会涉及BSP修改及 BOOT.bin的 生成.关于Vivado的具体操作请参考--"Zynq 7000从零开始之一 -- helloworld".

1. 用vivado搭好硬件模型.

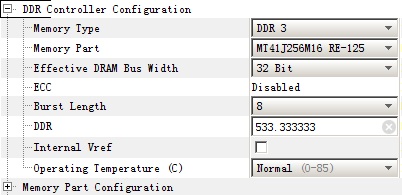

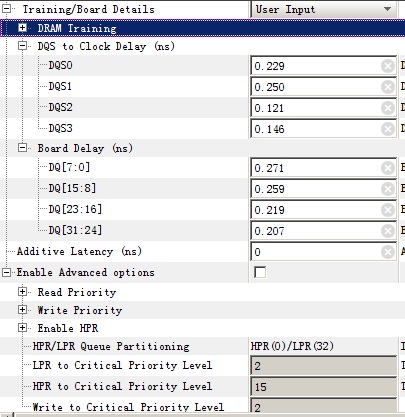

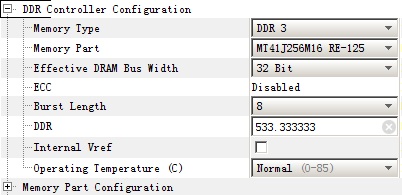

在vivado的block design中,PS的DDR Configuration配置如下:

选好Memory Part之后,Memory Part Configuration的参数就自动出来了,不用修改.

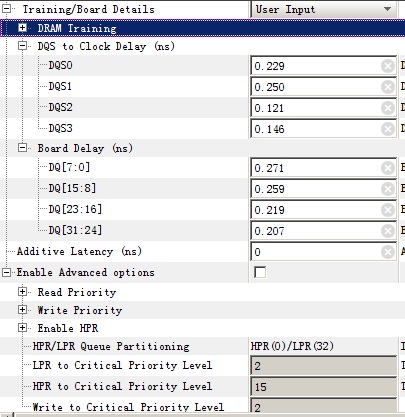

上面是根据DDR手册设置的参数,其他参数默认.

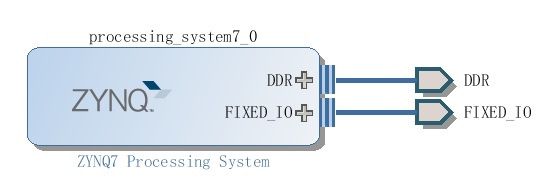

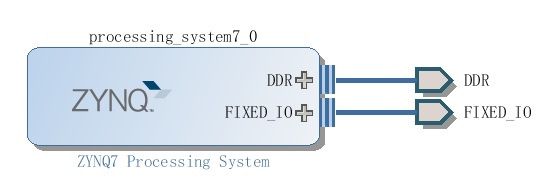

记得先Create HDL Wraper,再Run Synthesis.我配置好的block design界面如下:

就只有PS部分而已,不用生成bitstream.

点击file->export->export hardware导出硬件参数给SDK使用,因为没有用到FPGA,所以不用选Include bitstream, 导出到工程文件夹内.

点击file->launch SDK打开SDK编写软件.

2. 保存硬件参数

配置好参数后,把参数保存到硬盘上,下次可以直接导入该配置,后面的实验会基于该实验的配置进行配置.

在Re-customize IP界面点Presets->Save Configaration将PS配置保存为memtest.tcl.

3. 软件编写

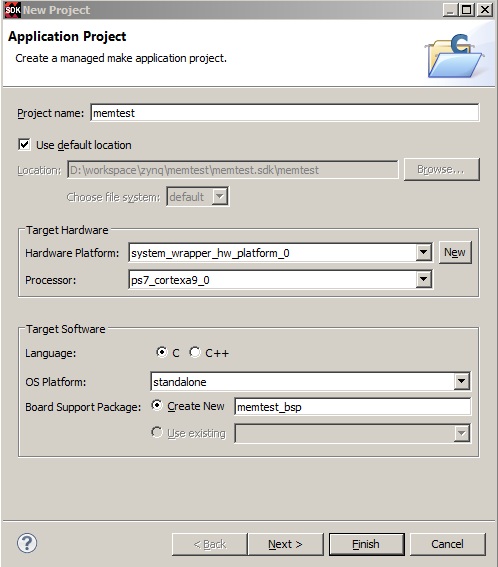

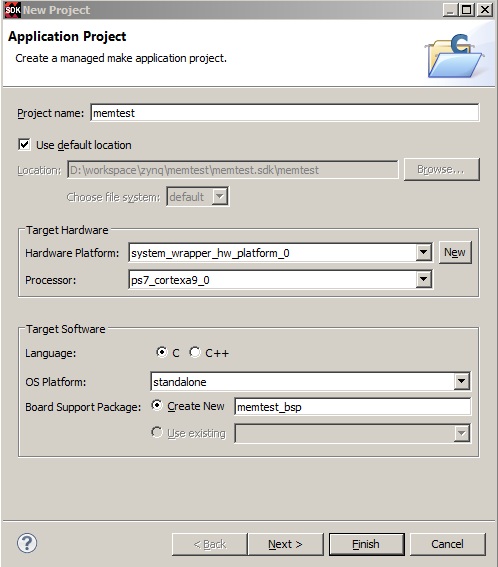

创建一个Application Project参数如下:

点击Next->Memory Tests->Finish.完成的在Project Explorer中多出了两个工程,一个是BSP,别一个是app工程.

因为使用2.3版本的SD卡驱动有问题,所以我们先把BSP中的SD卡驱动改成2.2版本的,具体方法请参考前一篇文章.

对源码还需要做些修改:

1>. 在memorytest.c中包含头文件 #include "ps7_init.h"

2>. memorytest.c中main函数中,在init_platform前面添加硬件初始化函数ps7_init();

3>. 将system_wrapper_hw_platform_0中的ps7_init.c包含到memtest工程中.

右击memtest工程->New->File->Advanced,勾上Link to file in the file system,

定位到system_wrapper_hw_platform_0下的ps7_init.c文件.

4>. 将ps7_init.h的路径添加到memtest中的头文件搜索路径.

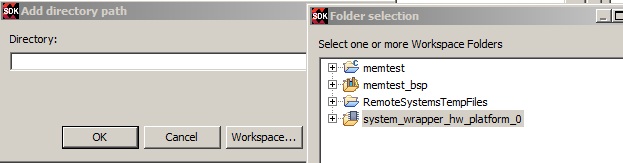

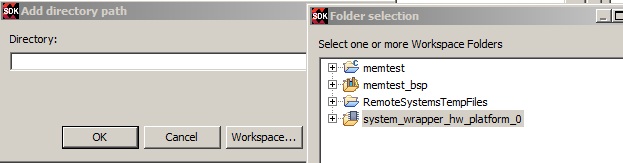

右击memtest工程->C/C++ Build Setttings->ARM gcc compiler->Directories,点击右边的添加按钮添加

路径,在Add directory path对话框中,点Workspace,选中system_wrapper_hw_platform_0.

之后,就可以编译了.

4. 生成BOOT.bin下载到z-turn板子上运行

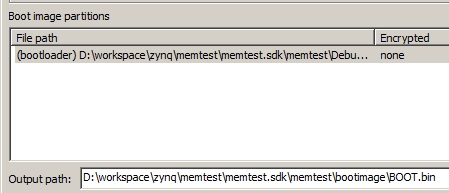

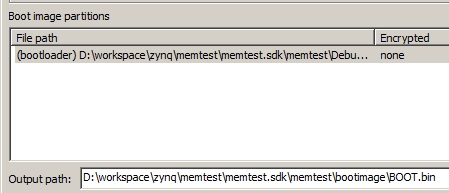

编译完成后,右击Project Explorer中的memtest工程->Create Boot Image.

在Boot image partitions将memtest.elf的partition type更改为bootloader.

将memtest\memtest.sdk\memtest\bootimage\文件夹下的BOOT.bin copy到SD卡上,插到z-turn板上运行,会出现以下串口信息:

--Starting Memory Test Application--

NOTE: This application runs with D-Cache disabled.As a result, cacheline requests will not be generated

Testing memory region: ps7_ddr_0

Memory Controller: ps7_ddr

Base Address: 0x00100000

Size: 0x3ff00000 bytes

32-bit test: PASSED!

16-bit test: PASSED!

8-bit test: PASSED!

Testing memory region: ps7_ram_1

Memory Controller: ps7_ram

Base Address: 0xffff0000

Size: 0x0000fe00 bytes

32-bit test: PASSED!

16-bit test: PASSED!

8-bit test: PASSED!

--Memory Test Application Complete--

本文主要讲怎样创建一个内存测试程序,测试DDR,程序还是运行在内部RAM;FPGA涉及的内容有怎样配置DDR参数,及怎样保存和导入硬件参数;软件方面会涉及BSP修改及 BOOT.bin的 生成.关于Vivado的具体操作请参考--"Zynq 7000从零开始之一 -- helloworld".

1. 用vivado搭好硬件模型.

在vivado的block design中,PS的DDR Configuration配置如下:

选好Memory Part之后,Memory Part Configuration的参数就自动出来了,不用修改.

上面是根据DDR手册设置的参数,其他参数默认.

记得先Create HDL Wraper,再Run Synthesis.我配置好的block design界面如下:

就只有PS部分而已,不用生成bitstream.

点击file->export->export hardware导出硬件参数给SDK使用,因为没有用到FPGA,所以不用选Include bitstream, 导出到工程文件夹内.

点击file->launch SDK打开SDK编写软件.

2. 保存硬件参数

配置好参数后,把参数保存到硬盘上,下次可以直接导入该配置,后面的实验会基于该实验的配置进行配置.

在Re-customize IP界面点Presets->Save Configaration将PS配置保存为memtest.tcl.

3. 软件编写

创建一个Application Project参数如下:

点击Next->Memory Tests->Finish.完成的在Project Explorer中多出了两个工程,一个是BSP,别一个是app工程.

因为使用2.3版本的SD卡驱动有问题,所以我们先把BSP中的SD卡驱动改成2.2版本的,具体方法请参考前一篇文章.

对源码还需要做些修改:

1>. 在memorytest.c中包含头文件 #include "ps7_init.h"

2>. memorytest.c中main函数中,在init_platform前面添加硬件初始化函数ps7_init();

3>. 将system_wrapper_hw_platform_0中的ps7_init.c包含到memtest工程中.

右击memtest工程->New->File->Advanced,勾上Link to file in the file system,

定位到system_wrapper_hw_platform_0下的ps7_init.c文件.

4>. 将ps7_init.h的路径添加到memtest中的头文件搜索路径.

右击memtest工程->C/C++ Build Setttings->ARM gcc compiler->Directories,点击右边的添加按钮添加

路径,在Add directory path对话框中,点Workspace,选中system_wrapper_hw_platform_0.

之后,就可以编译了.

4. 生成BOOT.bin下载到z-turn板子上运行

编译完成后,右击Project Explorer中的memtest工程->Create Boot Image.

在Boot image partitions将memtest.elf的partition type更改为bootloader.

将memtest\memtest.sdk\memtest\bootimage\文件夹下的BOOT.bin copy到SD卡上,插到z-turn板上运行,会出现以下串口信息:

--Starting Memory Test Application--

NOTE: This application runs with D-Cache disabled.As a result, cacheline requests will not be generated

Testing memory region: ps7_ddr_0

Memory Controller: ps7_ddr

Base Address: 0x00100000

Size: 0x3ff00000 bytes

32-bit test: PASSED!

16-bit test: PASSED!

8-bit test: PASSED!

Testing memory region: ps7_ram_1

Memory Controller: ps7_ram

Base Address: 0xffff0000

Size: 0x0000fe00 bytes

32-bit test: PASSED!

16-bit test: PASSED!

8-bit test: PASSED!

--Memory Test Application Complete--

1720

1720

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?