1 曼切斯特编码原理

1.1 当前时钟,输入为高,输出前半拍为高,后半拍为低。

1.2 当前时钟,输入为低,输出前半拍为低,后半拍为高。

1.3 manchester编码,可用其中的一个逻辑将信道归零。信道特性较好,但是需要2倍的频带带宽。

2 设计例子:曼切斯特编解码

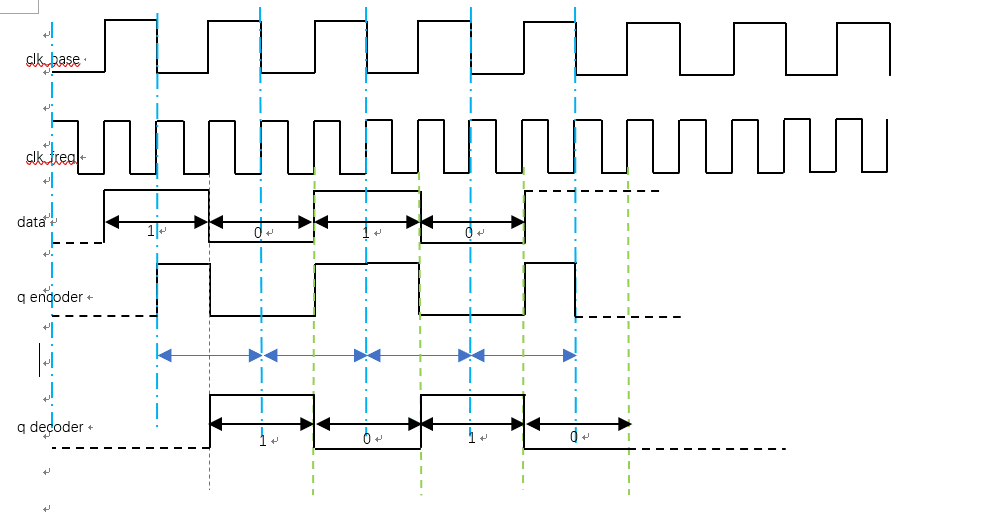

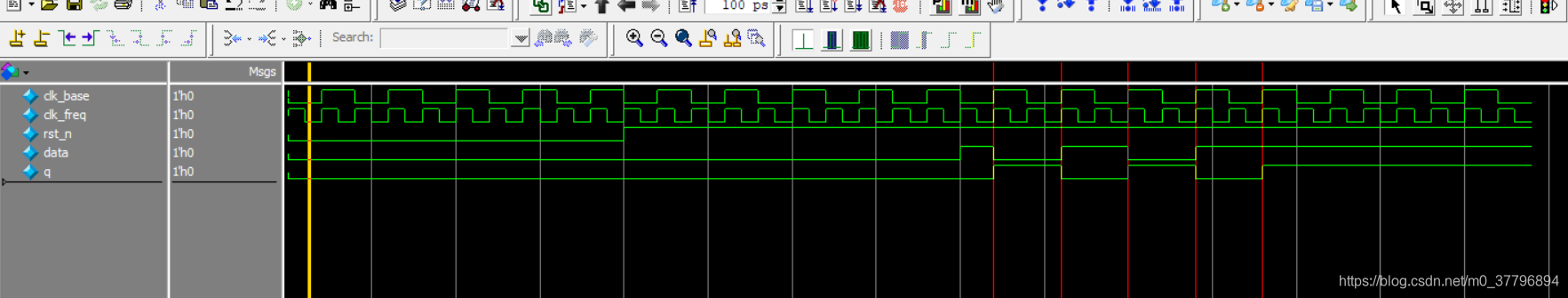

2.1 时序图

clk_base 基带信号

clk_freq 频带信号

data 输入数据(在做时序图的时候,按照data=4’h1010进行曼切斯特编解码设计。

q_encoder 编码后数据

q_decoder 解码后数据。

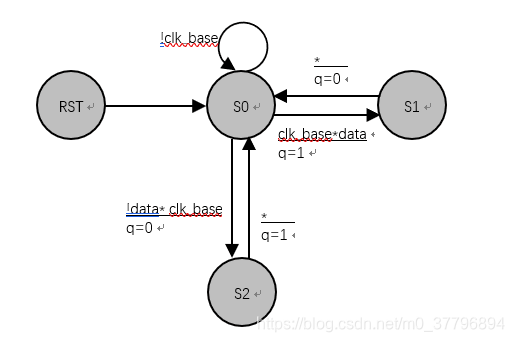

2.2 曼切斯特编码设计

2.2.1 状态转移图

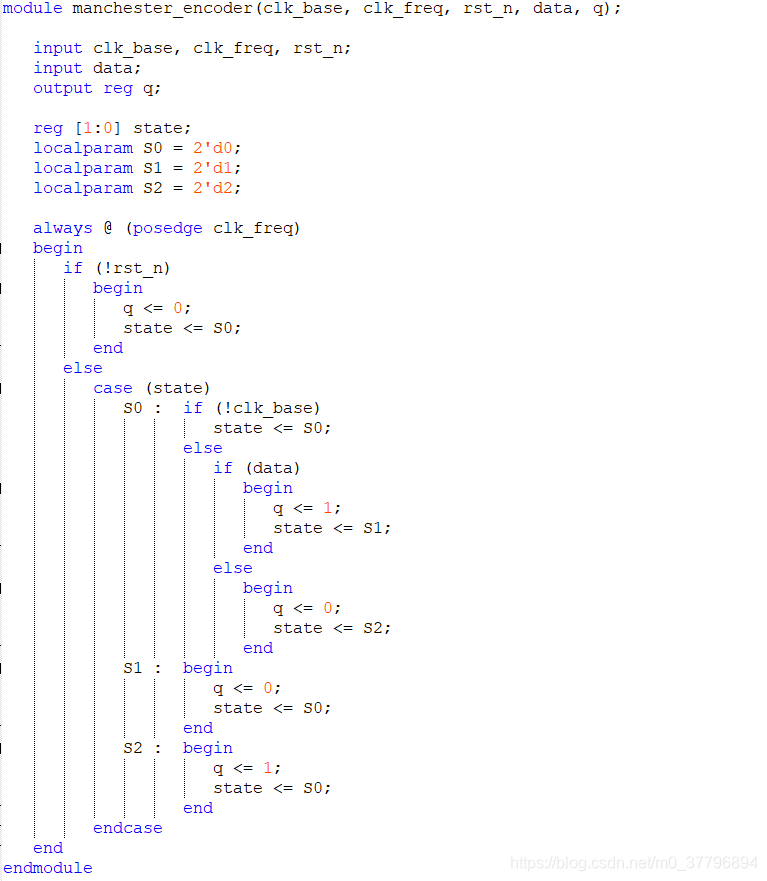

2.2.2 verilog代码

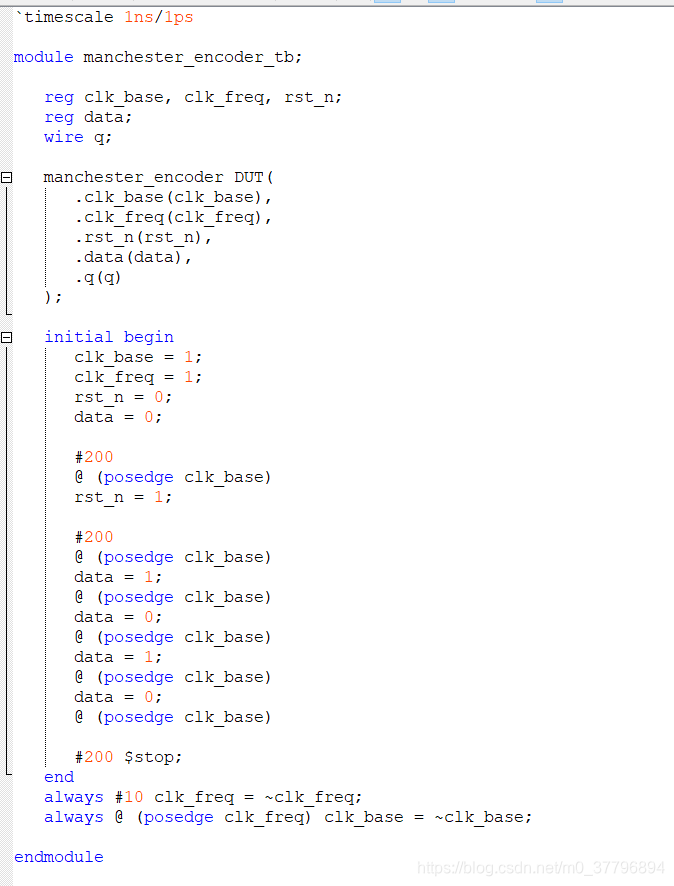

2.2.3 testbench代码

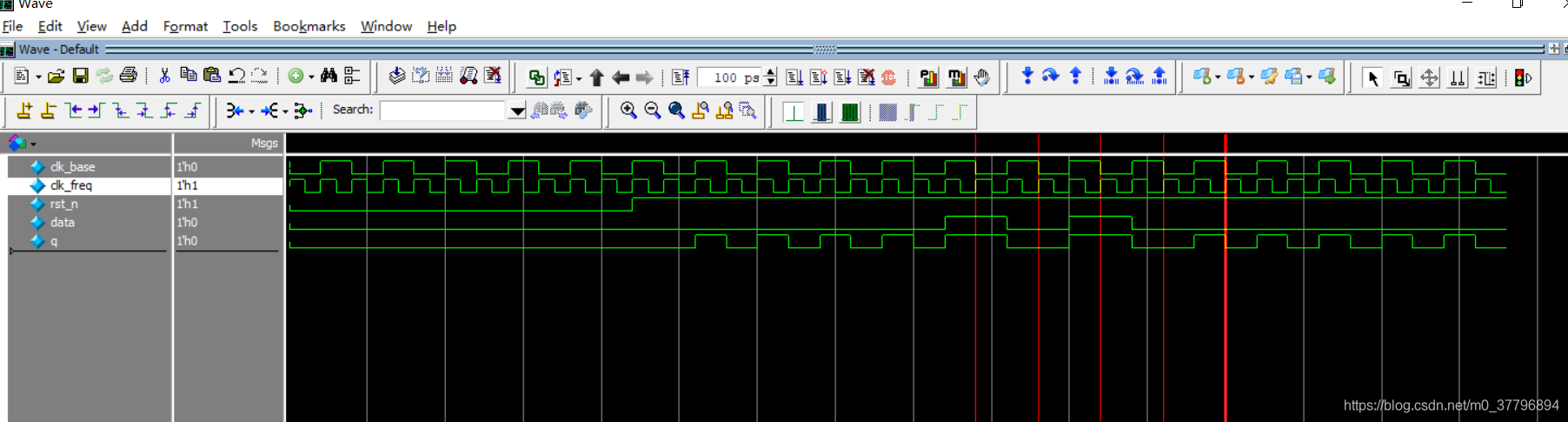

2.2.4 modelsim仿真

2.3 曼切斯特解码设计

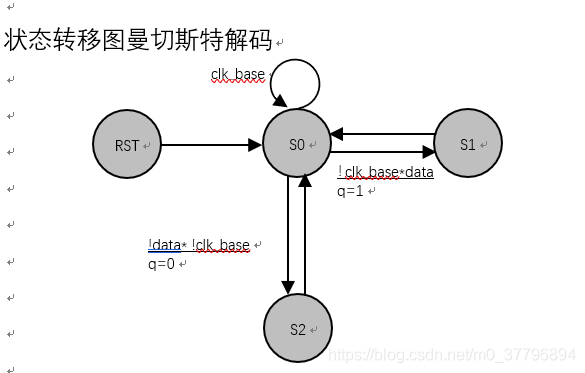

2.3.1 状态转移图

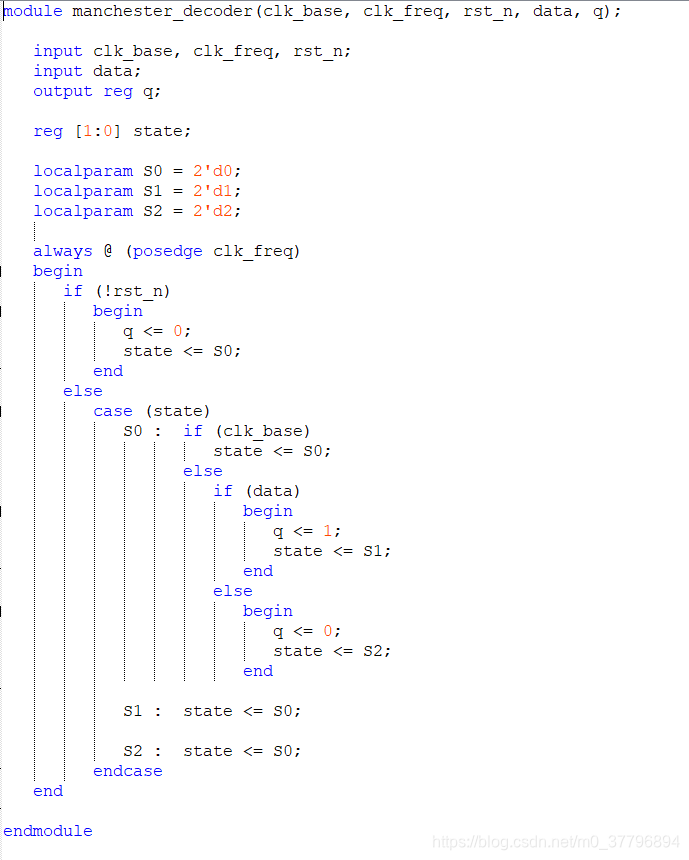

2.3.2 Verilog代码

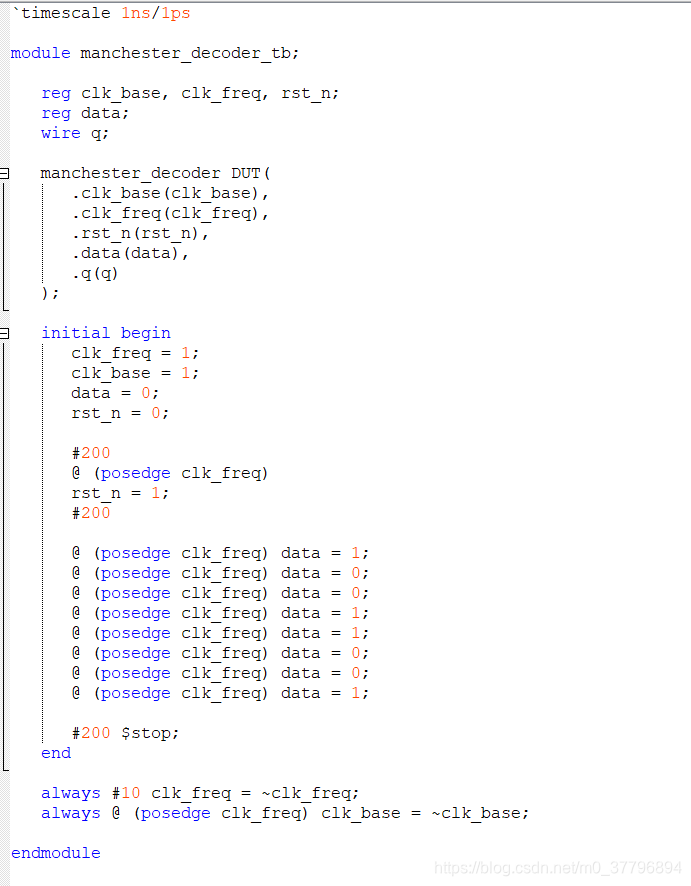

2.3.3 testbench代码

2.3.4 modelsim仿真

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?