Verilog 是硬件描述语言,硬件电路是并行执行的,当需要按照流程或者步骤来完成某个功能时,代码 中通常会使用很多个 if 嵌套语句来实现,这样就增加了代码的复杂度,以及降低了代码的可读性,这个时 候就可以使用状态机来编写代码。状态机相当于一个控制器,它将一项功能的完成分解为若干步,每一步 对应于二进制的一个状态,通过预先设计的顺序在各状态之间进行转换,状态转换的过程就是实现逻辑功 能的过程。

状态机,全称是有限状态机(

Finite State Machine,缩写为 FSM),是一种在有限个状态之间按一定规 律转换的时序电路,可以认为是组合逻辑和时序逻辑的一种组合。状态机通过控制各个状态的跳转来控制 流程,使得整个代码看上去更加清晰易懂,在控制复杂流程的时候,状态机优势明显,因此基本上都会用 到状态机,如

SDRAM 控制器等。在本手册提供的例程中,会有多个用到状态机设计的例子,希望大家能 够慢慢体会和理解,并且能够熟练掌握。

根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔

(Moore)

型状态机和米勒

(Mealy)

型状态机。

Mealy

状态机:组合逻辑的输出不仅取决于当前状态,还取决于输入状态。

Moore

状态机:组合逻辑的输出只取决于当前状态。

Mealy

状态机

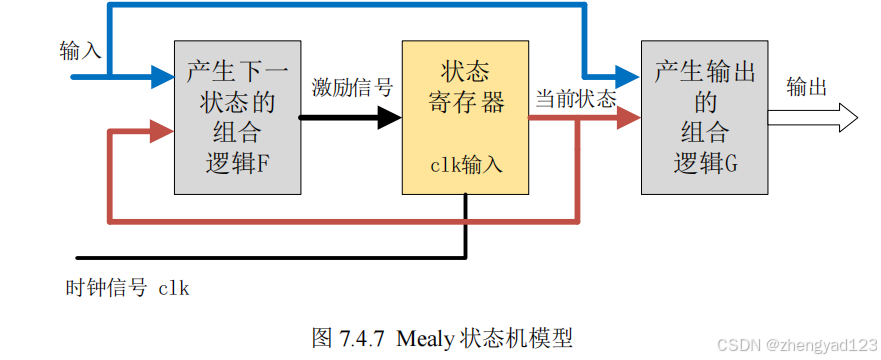

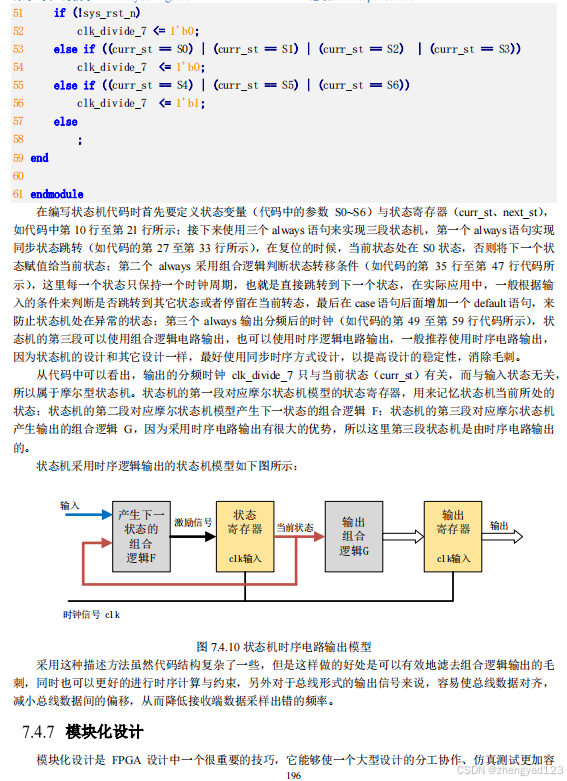

米勒状态机的模型如下图所示,模型中第一个方框是指产生下一状态的组合逻辑

F

,

F 是当前状态和 输入信号的函数,状态是否改变、如何改变,取决于组合逻辑 F 的输出;第二框图是指状态寄存器,其由 一组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳边沿;第三个框图是指 产生输出的组合逻辑

G

,状态机的输出是由输出组合逻辑

G

提供的,

G

也是当前状态和输入信号的函数。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?