目录

前言

基于stm32l433和LL库的系统时钟配置(学习RCC)。

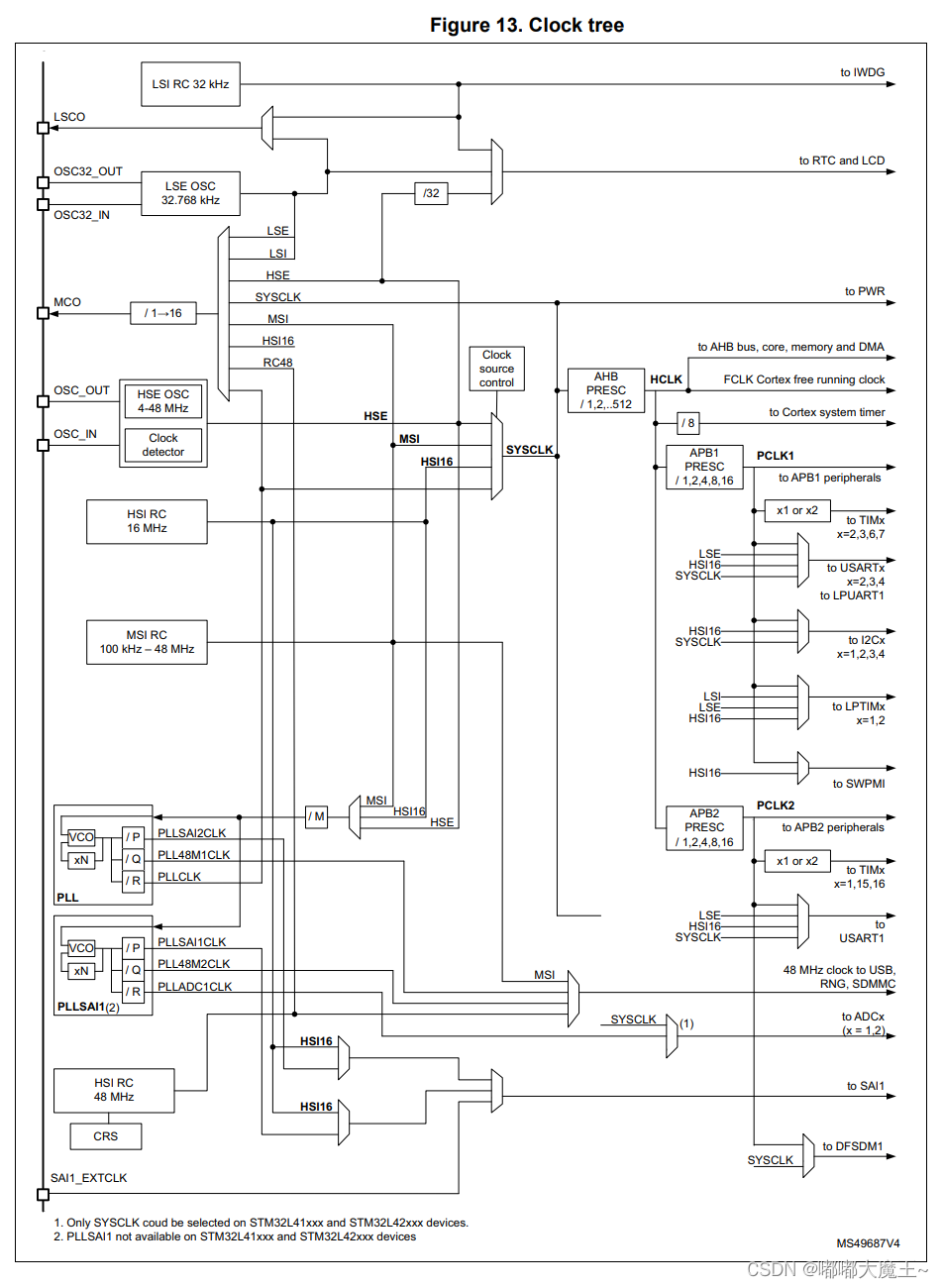

一、时钟树

芯片的时钟树,可以在对应芯片的参考手册的RCC章节找到。芯片的参考手册(Reference manual)可以在ST官网中找到,具体可以在官网先搜索对应芯片的型号,然后选择搜索类型为资源,在过滤器中选择Reference manual,即可找到对应芯片的参考手册。

本次实践,我将分别通过HSI、HSE设置系统时钟来进行演示。

二、系统时钟配置

1.HSE配置系统时钟

代码如下:

LL_FLASH_SetLatency(LL_FLASH_LATENCY_4);//保证flash读取的数据有效,时钟频率越高,延迟周期数越大

LL_RCC_HSE_Enable();//先使能外部高速时钟

while(LL_RCC_HSE_IsReady()){};//等待HSE就绪

//PLL需要先配置再使能,反之配置无效

LL_RCC_PLL_ConfigDomain_SYS(LL_RCC_PLLSOURCE_HSE,LL_RCC_PLLM_DIV_1,20,LL_RCC_PLLR_DIV_2);//配置用于SYSCLK的PLL,PLL输出的时钟频率为HSE/1*20/2

LL_RCC_PLL_Enable();//使能PLL

LL_RCC_PLL_EnableDomain_SYS();//允许PLL作为sysclk的时钟来源

while(LL_RCC_PLL_IsReady()){};//等待PLL就绪

LL_RCC_SetSysClkSource(LL_RCC_SYS_CLKSOURCE_PLL);//选择PLL做为sysclk的时钟源

LL_RCC_SetAHBPrescaler(LL_RCC_SYSCLK_DIV_1);//对AHB时钟进行预分频,分频系数为1,即与系统时钟一致

while(LL_RCC_GetSysClkSource() != LL_RCC_SYS_CLKSOURCE_STATUS_PLL){};//检查系统时钟来源是否为pll

LL_RCC_SetAPB1Prescaler(LL_RCC_APB1_DIV_1);//对APB1预分频,系数为1 即与AHB一致

LL_RCC_SetAPB2Prescaler(LL_RCC_APB2_DIV_1);//对APB2预分频,系数为1 即与AHB一致

LL_SetSystemCoreClock(80000000);//设置系统核心时钟频率为80MHz

2.HSI配置系统时钟

代码如下:

LL_FLASH_SetLatency(LL_FLASH_LATENCY_4);//保证flash读取的数据有效,时钟频率越高,延迟周期数越大

LL_RCC_HSI_Enable();//先使能内部高速时钟16MHz

while(LL_RCC_HSI_IsReady()){}//等待HSI就绪

//PLL需要先配置再使能,反之配置无效

LL_RCC_PLL_ConfigDomain_SYS(LL_RCC_PLLSOURCE_HSI,LL_RCC_PLLM_DIV_1,10,LL_RCC_PLLR_DIV_2);//配置用于SYSCLK的PLL,PLL输出的时钟频率为HSE/1*10/2

LL_RCC_PLL_Enable();//使能PLL

LL_RCC_PLL_EnableDomain_SYS();//允许PLL作为sysclk的时钟来源

while(LL_RCC_PLL_IsReady()){};//等待PLL就绪

LL_RCC_SetSysClkSource(LL_RCC_SYS_CLKSOURCE_PLL);//选择PLL做为sysclk的时钟源

LL_RCC_SetAHBPrescaler(LL_RCC_SYSCLK_DIV_1);//对AHB时钟进行预分频,分频系数为1,即与系统时钟一致

while(LL_RCC_GetSysClkSource() != LL_RCC_SYS_CLKSOURCE_STATUS_PLL){};//检查系统时钟来源是否为pll

LL_RCC_SetAPB1Prescaler(LL_RCC_APB1_DIV_1);//对APB1预分频,系数为1 即与AHB一致

LL_RCC_SetAPB2Prescaler(LL_RCC_APB2_DIV_1);//对APB2预分频,系数为1 即与AHB一致

LL_SetSystemCoreClock(80000000);//设置系统核心时钟频率为80MHz

问题及解决

- 仅实现使用HSI,HSE配置系统时钟,MSI配置类似,LSE和LSI将在未来用于配置其他外设时使用

文章介绍了基于STM32L433芯片,利用LowLayer(LL)库来配置HSE和HSI时钟的过程。通过设置不同的时钟源、PLL参数和预分频器,实现了系统时钟频率为80MHz。代码示例详细展示了如何启用并配置HSE和HSI,以及相应的PLL和系统时钟设置步骤。

文章介绍了基于STM32L433芯片,利用LowLayer(LL)库来配置HSE和HSI时钟的过程。通过设置不同的时钟源、PLL参数和预分频器,实现了系统时钟频率为80MHz。代码示例详细展示了如何启用并配置HSE和HSI,以及相应的PLL和系统时钟设置步骤。

8290

8290

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?