有没有考虑我们常说的默认阻抗是否可以调整呢,比如usb 90 一定不可变吗?

摘自凡亿课堂高速数字电路的阻抗匹配-凡亿教育课堂

高速数字电路的阻抗匹配

这篇文章我们来聊一聊阻抗匹配,尤其是高速数字电路的阻抗匹配问题。

1)什么是阻抗匹配

阻抗匹配是指信号源、传输线、负载之间的一种搭配方式。由于实际的信号源都是有内阻的,外面接上传输线、负载时,就不可避免地出现内阻和外部阻抗“分压”的情况。

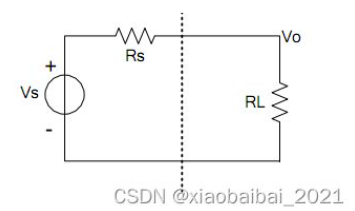

在一个低频电路中,假如信号源的电压为Vs,内阻是Rs;外部连接的负载电阻是RL,如下图所示:

假如Vs和Rs是固定的,那么简单分析一下,当RL变大时,负载上的电压Vo会变大,电路中的电流会减小;当RL变小时,负载上的电压Vo会变小,电路中的电流会变大。不难分析出,当RL=Rs时,外部的负载上能获得最大的功率,此时是就是一种“阻抗匹配”。

在高频或者高速信号中,情况要复杂一些,因为存在传输线效应。信号频率很高时,波长很短,必须考虑信号反射的问题,此时,如果反射信号很大,反射信号叠加在原信号上,会引起较大的失真。

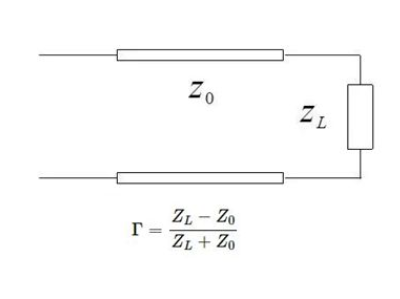

如果传输线的特征阻抗与负载阻抗不相等(不匹配)时,在负载端就会产生反射。反射信号的幅度可以由反射系数来描述,见下图:

其中Z0是传输线的特征阻抗,ZL是负载的阻抗,Γ是反射系数。如果传输过来的信号幅度为A,则反射信号的幅度为A*Γ。

容易验证,当ZL和Z0相等时,反射系数Γ为0,即不反射;不会对传输线上的信号产生反射干扰。当ZL为0时,产生幅度与输入信号相等但反相的反射波,反射波和入射波叠加后,在传输线上的某些点叠加后可能将信号完全抵消掉。当ZL开路时,产生幅度与输入信号相等且同相的反射波,在传输线上的某些点叠加后可能产生幅度加倍的信号(有时我们测量高速信号有较大的过冲,这是可能的原因之一)。

我们在信号传输时,总希望信号无反射地传输到负载端,所以需要尽量保证信号路径上的阻抗处处相等(输入阻抗和输出阻抗相等),这个状态就是阻抗匹配。

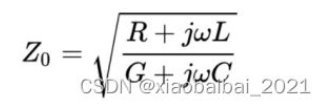

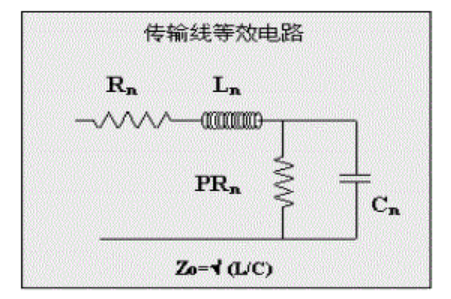

这里注意一下特征阻抗这个概念,它是传输线理论中特有的,定义为入射波电压和入射波电流的比值:(这其中有较多的偏微分方程推导,这里略过)

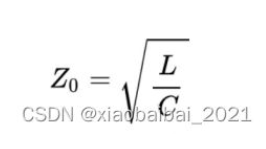

R、L、C、G分别是传输线单位长度上的电阻、电感、电容和漏电导。本来特征阻抗Z0是一个复数,但是在传输线理论适用时,信号频率ω非常大,相对地电阻R和电导G可以忽略(认为传输时无损耗),所以Z0就近似成一个实数了:

特征阻抗Z0是传输线的固有特性,由结构及材料决定的,一般线材厂家会提供,与它的长度、信号幅度、频率等均无关。(当然需注意,长度和频率要符合传输线理论的适用范围,满足这个要求后,长度再加长,或者频率再提高,特征阻抗是不变的)。

比如,我们常见的75Ω、50Ω阻抗的同轴电缆,100Ω的以太网差分线、120Ω的CAN传输线,指的就是传输线的特征阻抗,都是以纯电阻的形式表示的。

2)如何实现阻抗匹配

一般来讲,阻抗不连续的点都在信号源端、负载端,或者两段不同的传输线相连接的位置,所以,一般都需要在这些位置进行阻抗变换。但是,对于高速数字电路和高频电路使用的阻抗匹配方法又会有不同。

在高速数字电路系统中,一般只需要把信号的跳变沿传输过去就行了,只要阻抗匹配能保证波形不发生大的畸变,目的是为了抑制反射震荡等,所以一般采取串电阻、并电阻的方法就能实现。而高频电路往往需要把能量传输过去,电阻会消耗额外的功率,只能用电感、电容、短接线等方式去实现匹配,相对复杂一些。

本文中,我们先来讲简单一点的,高速数字电路的阻抗匹配,有以下几种匹配的方法:

a)串联电阻法

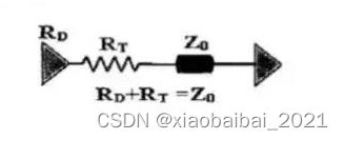

一般用于电路内部的阻抗比传输线阻抗小,常见于信号的输出端。一般器件的输出端阻抗较小,通常是十几欧姆到二十几欧姆;而一般的传输线特征阻抗通常会控制在几十欧姆到一百多欧姆,串联电阻后,可以保证阻抗匹配,如下图所示:

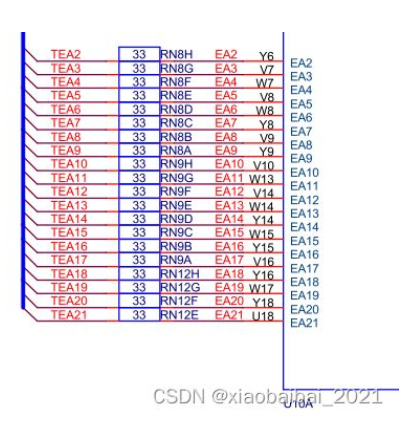

电路的输出阻抗为RD,传输线阻抗为Z0,串联RT后,使得RD+RT=Z0实现阻抗匹配。要注意RT的位置要尽量靠近输出引脚。比如,有源晶振的输出端、数据总线的输出端,很多时候推荐串联一个22Ω或33Ω的电阻,就是这个用途。使用之后高速信号的在源处的反射会改善很多,但是由于串联了电阻,信号的跳变沿会变慢一些。如下图中地址线输出的实例:

b)并联电阻法

一般用于电路内部的阻抗比传输线阻抗大的情况,常见于信号的接收端。一般器件的输入阻抗都较大,通常是数百千欧或者上兆欧,并联一个电阻后,可保证阻抗匹配,如下图所示:

电路的输入阻抗近似于无穷大时,并联RT=Z0,使得阻抗匹配,当然,这个电阻也可以加在信号线与电源之间,用电源作为参考面,或者加在差分线的正负之间。

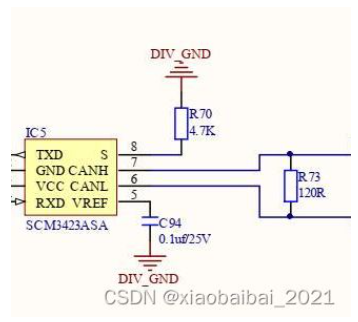

并联电阻法通常用在接收端,比如RS48、CAN芯片的输入端、LVDS信号的输入端。RT的位置要尽量靠近输入引脚。并联的电阻会产生一些额外的功耗,并且会对电平产生一点影响(比如下拉电阻使得高电平的实际电平变低)。如下图所示CAN总线的实例:

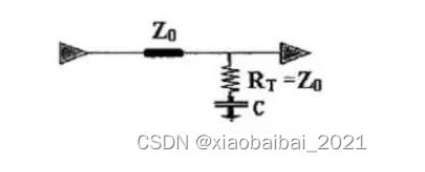

c)AC并联端接法

这个方法和并联电阻法相似,但是,采用电阻和电容串联,如下图所示:

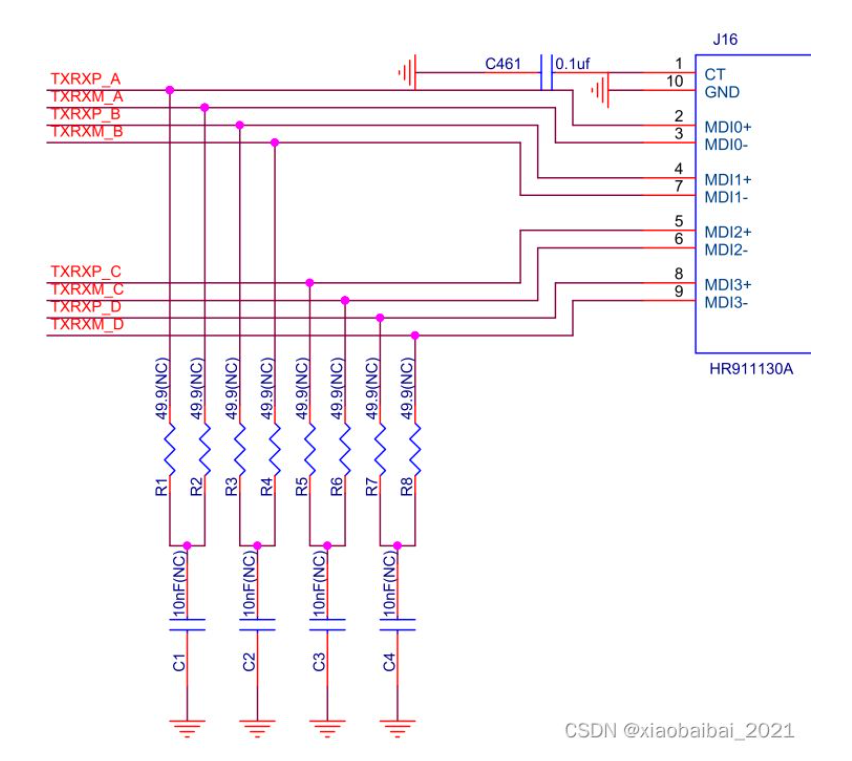

这种方法使得RT上的直流功耗减小了;但是增加了一个电容器,同时电容会造成延时;它只适用于周期性的信号(如时钟),不适用于非周期信号(如数据)。如下图的以太网匹配电路:

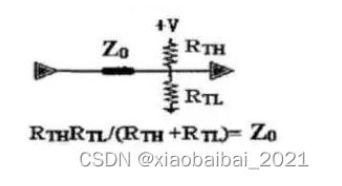

d)戴维南端接法

用两个电阻,同时上下拉来实现并联匹配。如下图所示:

要求两个电阻并联值与Z0相等。这个电路对高、低电平的影响是对等的;也会增加直流功耗。

好了,本节就到这里了,我们了解了阻抗匹配的一些基本原理问题、高速电路阻抗匹配的方法。

声明:本文转载自小白白学电子 公众号,如涉及作品内容、版权和其它问题,请于联系工作人员,我们将在第一时间和您对接删除处理!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表凡亿课堂立场。文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。

相关阅读

精彩评论

暂无评论

我来说两句

0

0

0

本文探讨了高速数字电路中阻抗匹配的重要性,介绍了阻抗匹配的基本概念,包括阻抗定义、反射问题以及如何通过串联电阻、并联电阻和AC并联端接法实现匹配。重点讲解了在信号源端和负载端使用电阻进行阻抗变换的方法。

本文探讨了高速数字电路中阻抗匹配的重要性,介绍了阻抗匹配的基本概念,包括阻抗定义、反射问题以及如何通过串联电阻、并联电阻和AC并联端接法实现匹配。重点讲解了在信号源端和负载端使用电阻进行阻抗变换的方法。

4464

4464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?