一、实验目的

1、学习触发器逻辑功能的测试方法。

2、熟悉基本RS触发器的组成、工作原理和性能。

3、熟悉集成JK触发器和集成D触发器的逻辑功能及触发方式。

二、实验仪器

1.数字电路实验箱

2.器材

三、实验内容详解

1.基本RS触发器逻辑功能的测试

基本RS触发器由两个与非门首位相接构成,如图4-1-1所示。

图中,Rd’和Sd’输入端接逻辑电平开关,Q和Q’输出端接电平显示器。

(1)按表4-1-1的要求给Rd’、Sd’端加信号,借助电平显示器观察并记录Q和Q’的状态,将结果记录于表4-1-1中。

(2)不定状态的测试

连接Rd’和Sd’并接到同一个逻辑电平开关。首先开关打向“L”,即Rd’=Sd’=0。当逻辑电平开关由“L”变为“H”时,即Rd’=Sd’=1时,观察触发器Q的状态,做5~10次或更多次,分析所得的结果,体会“不定”的含意。

2、集成JK触发器逻辑功能的测试

JK触发器是一-种下降边沿触发器,它的逻辑符号如图4-2-1。74LS112芯片是双JK集成触发器电路,其中有两个如图4-2-1的JK触发器。图4-2-2是74LS112在实验箱面板上的逻辑接线图。

(1)异步置位及复位功能的测试

如图4-2-3所示,J、K和CP任意状态(实验时一般悬空),Sa 是置位端,是Rs复位端。Sd’和Rd’接逻辑电平开关,Q和Q’接电平显示器,按表4-2-1情况测试Q端的状态,把结果填入表4-2-1中。(注意: X表示任意状态。)

(2)逻辑功能的测试(J、 K与(Q^(n+1))的关系)

a)按图4-2-4接线,先将触发器置“1”,使触发 器的初始状态为“1”,即Q=1。

①触发器置“1”时,Rd’=1,Sd’=0。

②触发器置“1”完成后,Rd’=1, Sd’=1。

从CP端输入单脉冲(从实验箱面板上取得)。按表4-2-2的情况分别测出Q端的状态,将结果填入表4-2-2中。

注意观察: i)触发器的状态与J、K之间的关系。

ii)触发器是在时钟脉冲的上升沿还是下降沿触发的。

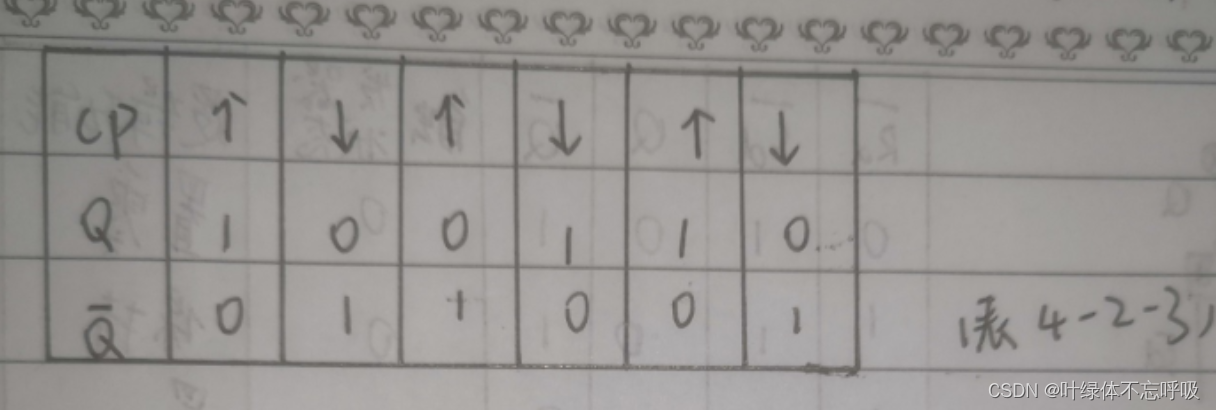

注:表中↑是CP的上升边沿,↓是为CP的下升边沿。

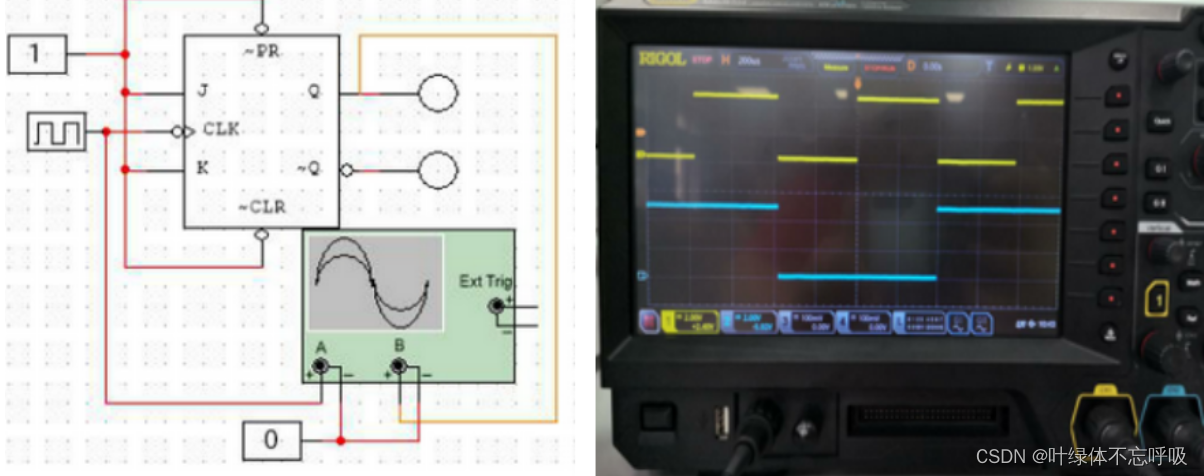

b)将JK触发器接成计数状态(JK触发器转换成T’触发器)

J=1, K=1,Rd’=1,Sd’=1。

①CP端加入单次脉冲,将结果填入表4-2-3中。

②CP端加入连续脉冲,用双踪示波器观察Q和Q’的波形。

①观察触发器被CP下降沿触发的现象:CH1→CP CH2-→Q和Q’

②观察触发器Q和Q’反相的现象:CH1→Q’ CH2-→Q

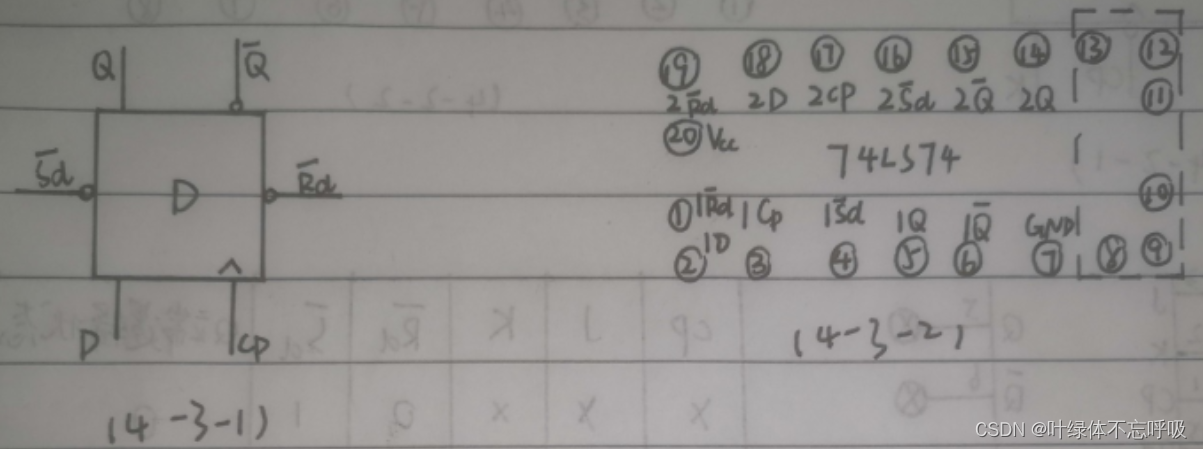

3、集成D触发器逻辑功能的测试

维持-阻塞D触发器是一种上升边沿触发器,它的逻辑符号如图4-3-1所示。74LS74芯片是双D触发器电路,其中有两个如图4-3-1的D触发器。图4-3-2是74LS74在实验箱面板上的逻辑接线图。

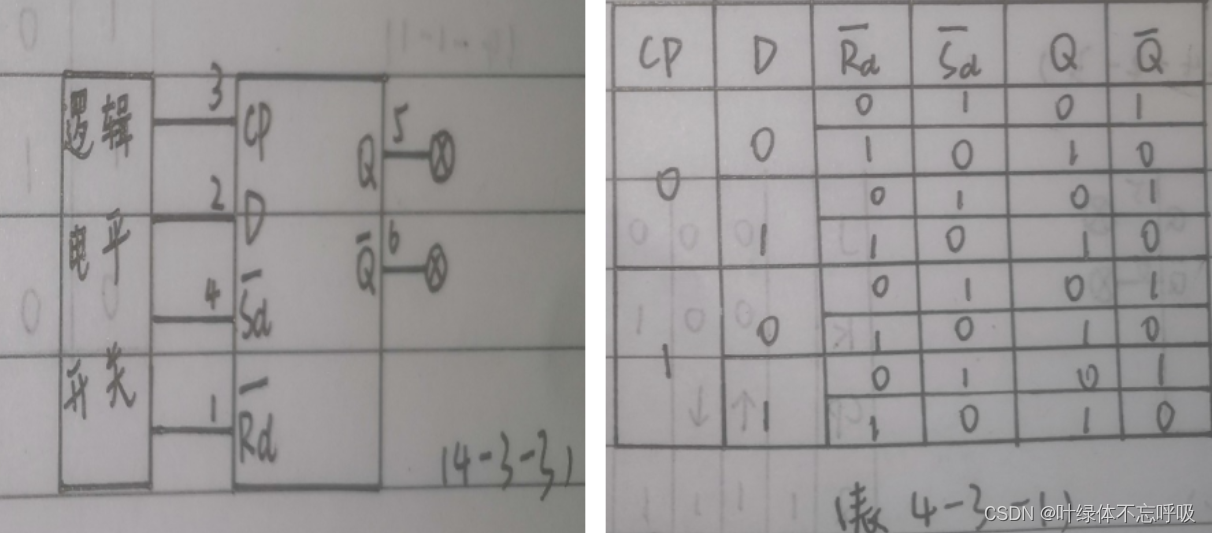

(1) Rd’和Sd’功能测试

按图4-3-3接线,按表4-3-1中情况进行实验,结果填入表4-3-1中。

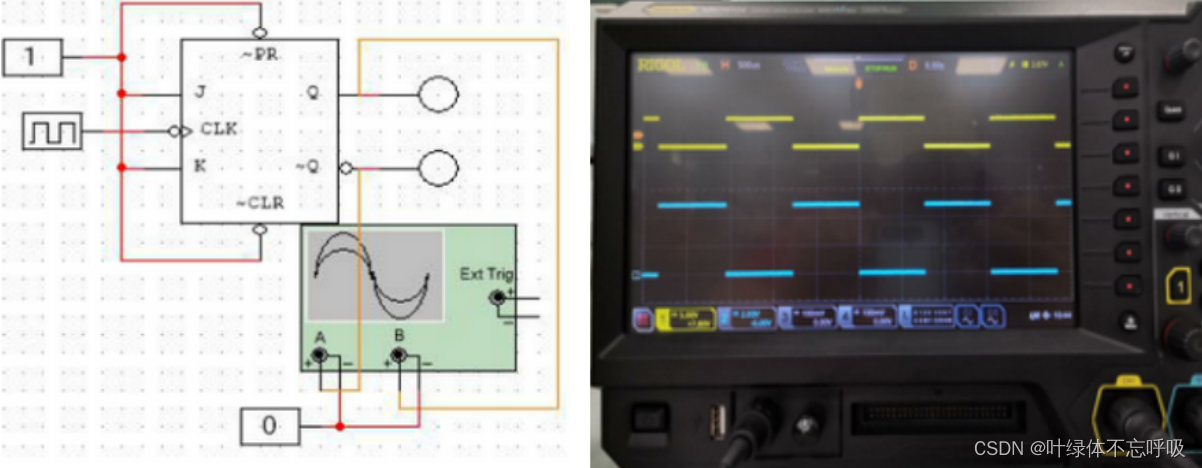

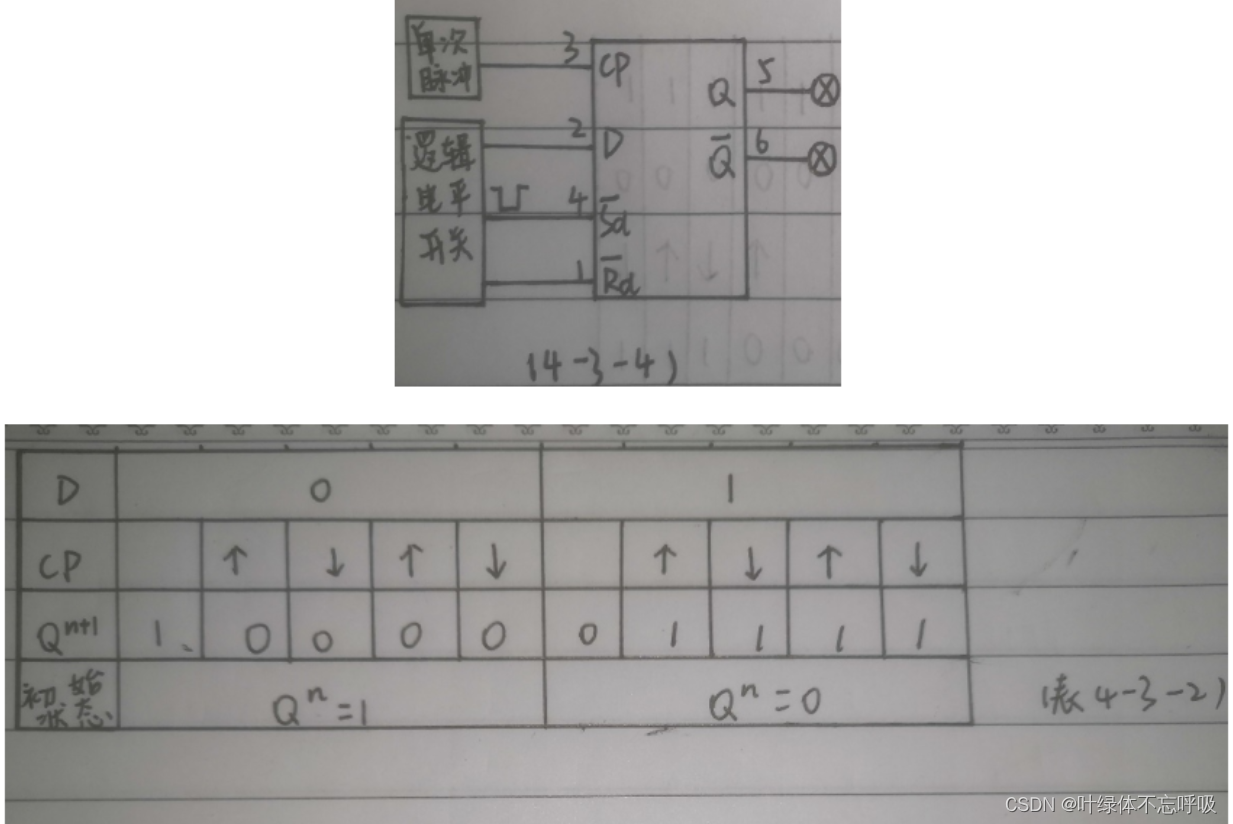

(2)逻辑功能的测试(D与(Q^(n+1))的关系)

按图4-3-4接线,Rd’=1, Sd’=1, D为1或0, CP端输入单脉冲,按表4-3-2的顺序进行实验,并将结果填入表4-3-2中。

注意观察: i)触发器是在时钟脉冲的上升沿还是下降沿被触发。

ii)时钟脉冲CP作用前后,触发器Q端的状态。

注:表中↑是CP的上升边沿,↓是为CP的下升边沿。

初始置位: {置“1”—Rd’=1,Sd’=0}

{置“0”—Rd’=0,Sd’=1},置位完成后,Rd’=1,Sd’=1。

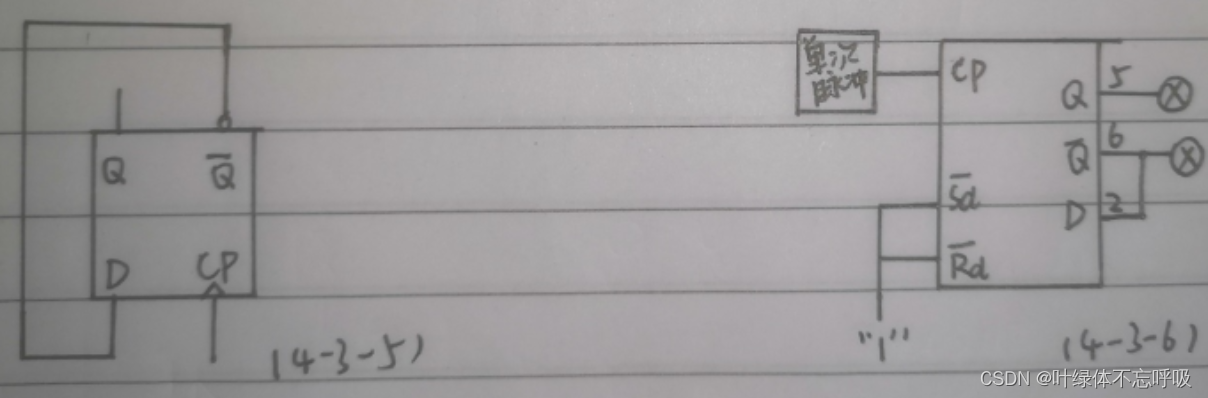

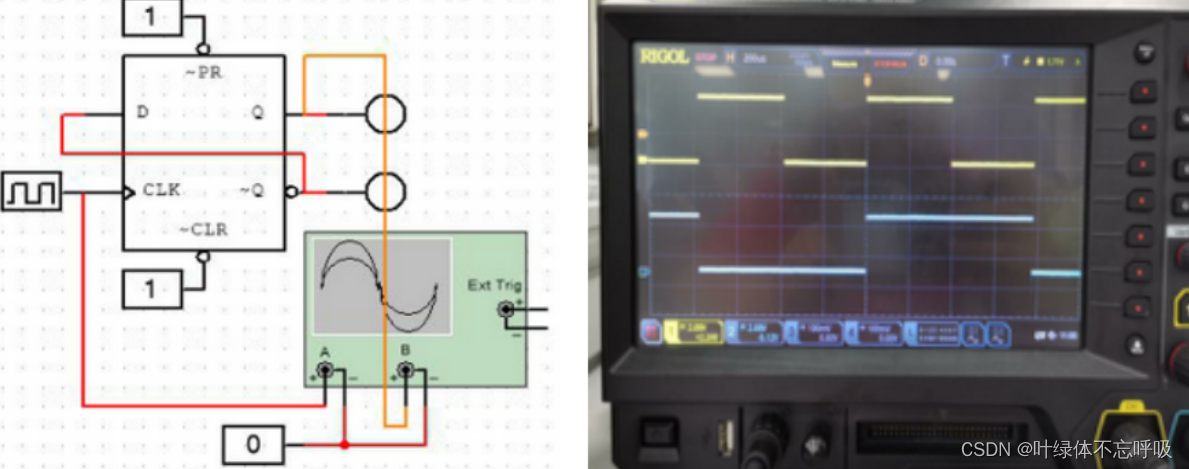

(3)触发器间的转换: T’触发器逻辑功能测试

本实验用D触发器来实现,令D=Q’,就成了T’触发器,如图4-3-5所示。T’触发器实际上就是一个计数器。

a)单次脉冲触发

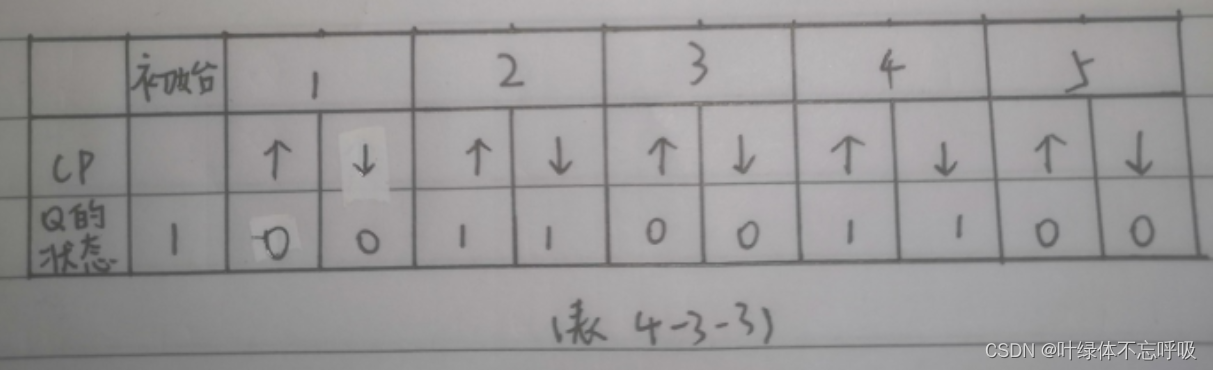

按图4-3-6连线,在CP端输入单次脉冲,按表4-3-3顺序实验,观察Q端随CP变化的规律,并填入表4-3-3中。

从上表中可以看出每一个CP, Q端状态共变化5次。

b)连续脉冲触发

将图4-3-6中的“单次脉冲”换成“连续脉冲”,用双踪示波器观察Q和Q的波形。

a)观察触发器被CP下降沿触发的现象:CH1→CP CH2→Q

博主分享了一篇关于基础人工智能学习的文章,介绍了RS触发器和JK触发器的实验步骤,包括逻辑功能测试和操作演示,适合初学者通过实践理解数字逻辑。链接提供了无广告、风趣教材,适合技术爱好者深入学习。

博主分享了一篇关于基础人工智能学习的文章,介绍了RS触发器和JK触发器的实验步骤,包括逻辑功能测试和操作演示,适合初学者通过实践理解数字逻辑。链接提供了无广告、风趣教材,适合技术爱好者深入学习。

162

162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?